Colvilles Road, Kelvin Estate - East Kilbride/Glasgow - SCOTLAND

# MCM6116

# 16K BIT STATIC RANDOM ACCESS MEMORY

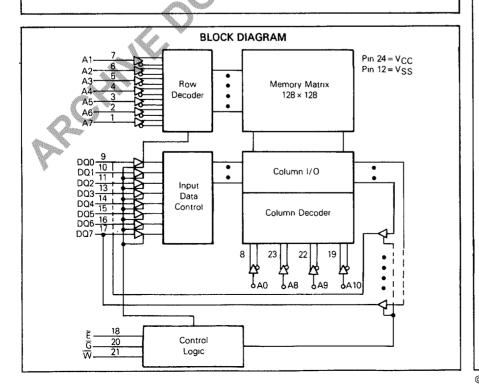

The MCM6116 is a 16,384-bit Static Random Access Memory organized as 2048 words by 8 bits, fabricated using Motorola's high-performance silicon-gate CMOS (HCMOS) technology. It uses a design approach which provides the simple timing features associated with fully static memories and the reduced power associated with CMOS memories. This means low standby power without the need for clocks, nor reduced data rates due to cycle times that exceed access time.

Chip Enable  $(\overline{E})$  controls the power-down feature. It is not a clock but rather a chip control that affects power consumption. In less than a cycle time after Chip Enable  $(\overline{E})$  goes high, the part automatically reduces its power requirements and remains in this low-power standby as long as the Chip Enable  $(\overline{E})$  remains high. The automatic power-down feature causes no performance degradation.

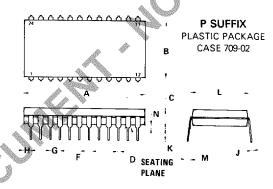

The MCM6116 is in a 24-pin dual-in-line package with the industry standard JEDEC approved pinout and is pinout compatible with the industry standard 16K EPROM/ROM.

- Single +5 V Supply

- 2048 Words by 8-Bit Operation

- HCMOS Technology

- Fully Static: No Clock or Timing Strobe Required

- Maximum Access Time: MCM6116-12 120 ns

MCM6116-15 - 150 ns

MCM6116-20 - 200 ns

- Power Dissipation: 70 mA Maximum (Active)

15 mA Maximum (Standby-TTL Levels)

2 mA Maximum (Standby)

- Low Power Version Also Available MCM61L16

- Low Voltage Data Retention (MCM61L16 Only): 50 μA Maximum

# **HCMOS**

(COMPLEMENTARY MOS)

2,048×8 BIT STATIC RANDOM ACCESS MEMORY

P SUFFIX

PLASTIC PACKAGE

CASE 709

# PIN ASSIGNMENTS

| PIN NAMES       |                                    |  |  |  |  |  |

|-----------------|------------------------------------|--|--|--|--|--|

| A0-A10          | Address Input<br>Data Input/Output |  |  |  |  |  |

| DQ0-DQ7         | Data Input/Output                  |  |  |  |  |  |

| ₩               | Write Enable                       |  |  |  |  |  |

| G               | Output Enable                      |  |  |  |  |  |

| [ 臣             | Chip Enable                        |  |  |  |  |  |

| V <sub>CC</sub> | Power (+5 V)                       |  |  |  |  |  |

| V <sub>SS</sub> | Ground                             |  |  |  |  |  |

DS9873

#### **ABSOLUTE MAXIMUM RATINGS** (See Note)

| Rating                                 | Value          | Unit |

|----------------------------------------|----------------|------|

| Temperature Under Bias                 | -10 to +80     | °C   |

| Voltage on Any Pin With Respect to VSS | -1.0  to  +7.0 | V    |

| DC Output Current                      | 20             | mA   |

| Power Dissipation                      | 1.2            | Watt |

| Operating Temperature Range            | 0 to +70       | °C   |

| Storage Temperature Range              | -65 to +150    | °C   |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this highimpedance circuit.

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to RECOMMENDED OPERAT-ING CONDITIONS. Exposure to higher than recommended voltages for extended periods of time could affect device reliability.

#### DC OPERATING CONDITIONS AND CHARACTERISTICS

(Full operating voltage and temperature ranges unless otherwise noted.)

#### RECOMMENDED OPERATING CONDITIONS

| . Parameter    | <br>Symbol      | Min    | Тур | Max | Unit |

|----------------|-----------------|--------|-----|-----|------|

| Supply Voltage | Vcc             | 4.5    | 5.0 | 5.5 | ٧    |

| Supply voltage | Vss             | 0      | 0   | 0   | ٧    |

| Lanut Valtaga  | V <sub>IH</sub> | 2.2    | 3.5 | 6.0 | ٧    |

| Input Voltage  | VIL             | - 1.0° | -   | 0.8 | ٧    |

<sup>\*</sup>The device will withstand undershoots to the -1.0 volt level with a maximum pulse width of 50 ns at the -0.3 volt level. This is periodically sampled rather than 100% tested.

# RECOMMENDED OPERATING CHARACTERISTICS

| Parameter                                                                                                               | Cumbal           |     | MCM6116 |      |     | MCM61L16 |     |      |

|-------------------------------------------------------------------------------------------------------------------------|------------------|-----|---------|------|-----|----------|-----|------|

| Farameter                                                                                                               | Symbol           | Min | Тур*    | Max  | Min | Тур*     | Max | Unit |

| Input Leakage Current (V <sub>CC</sub> =5.5 V, V <sub>in</sub> =GND to V <sub>CC</sub> )                                | Pul              | -   | _       | 1    | _   | -        | 1   | μΑ   |

| Output Leakage Current ( $E = V_{IH}$ or $G = V_{IH} V_{I/O} = GND$ to $V_{CC}$ )                                       | litol            | _   | -       | 1    | -   | -        | 1   | μΑ   |

| Operating Power Supply Current (E=V <sub>IL</sub> , I <sub>I/O</sub> =0 mA)                                             | <sup>1</sup> CC  | _   | 35      | 70   | -   | 35       | 55  | mΑ   |

| Average Operating Current Minimum cycle, duty=100%                                                                      | ICC2             | _   | 35      | 70   |     | 35       | 55  | mΑ   |

| Standby Power (E = V <sub>IH</sub> )                                                                                    | ISB              | _   | 5       | 15   | _   | 5        | 12  | mΑ   |

| Supply Current $(E \ge V_{CC} - 0.2 \text{ V}, V_{in} \ge V_{CC} - 0.2 \text{ V} \text{ or } V_{in} \le 0.2 \text{ V})$ | I <sub>SB1</sub> | -   | 20      | 2000 | -   | 4        | 100 | μA   |

| Output Low Voltage (IOL=2.1 mA)                                                                                         | VOL              | -   | _       | 0.4  | -   | -        | 0.4 | V    |

| Output High Voltage (I <sub>OH</sub> = -1.0 mA)*                                                                        | ∨он              | 2.4 |         |      | 2.4 | -        | _   | V    |

<sup>\*</sup>V<sub>CC</sub>=5 V, T<sub>A</sub>=25°C

# **CAPACITANCE** (f = 1.0 MHz, $T_A = 25$ °C, periodically sampled rather than 100% tested.)

| Characteristic                                   | Symbol           | Тур | Max | Unit |

|--------------------------------------------------|------------------|-----|-----|------|

| Input Capacitance except E                       | C <sub>in</sub>  | 3   | 5   | рF   |

| Input/Output Capacitance and E Input Capacitance | C <sub>1/O</sub> | 5   | 7   | pF   |

# **MODE SELECTION**

|                 | Mode | Ē | Ğ | W | VCC Current     | DQ     |

|-----------------|------|---|---|---|-----------------|--------|

| Standby         |      | Н | Х | Х | ISB, ISB1       | High Z |

| Read            |      | L | L | H | <sup>1</sup> CC | Q      |

| Write Cycle (1) |      | L | Н | L | Icc             | D      |

| Write Cycle (2) |      | L | L | L | <sup>1</sup> CC | D      |

<sup>\*\*</sup>Also, output voltages are compatible with Motorola's new high-speed CMOS logic family if the same power supply voltage is used.

# AC OPERATING CONDITIONS AND CHARACTERISTICS

| (Full operating voltage and temperature unless otherwise noted.) |                                          |  |  |  |  |  |  |

|------------------------------------------------------------------|------------------------------------------|--|--|--|--|--|--|

| Input Pulse Levels                                               | Input and Output Timing Reference Levels |  |  |  |  |  |  |

| Input Rise and Fall Times10 ns                                   | Output Load                              |  |  |  |  |  |  |

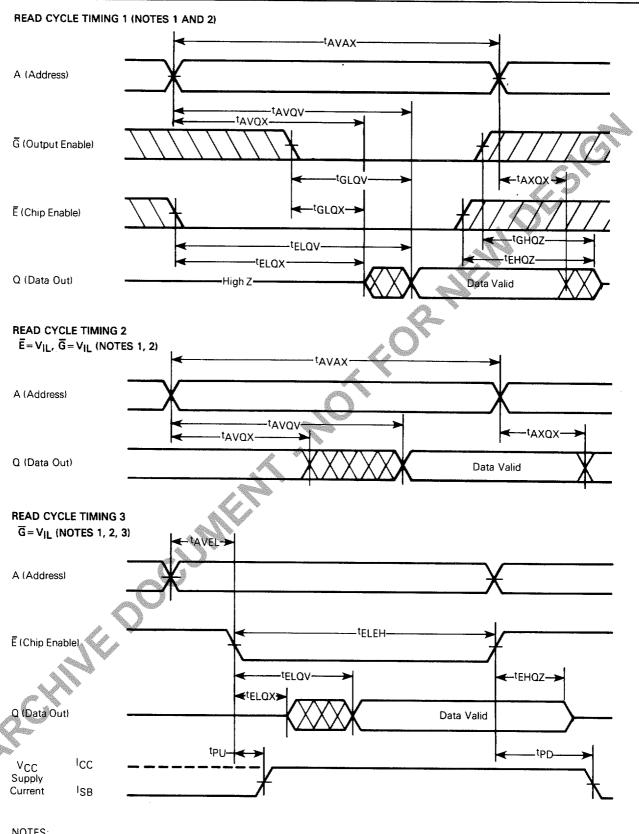

#### READ CYCLE ~

| Parameter                                                                        | Symbol            | MCM6116-12<br>MCM61L16-12 |           | MCM6116-15<br>MCM61L16-15 |     | MCM6116-20<br>MCM61L16-20 |                  | Unit |

|----------------------------------------------------------------------------------|-------------------|---------------------------|-----------|---------------------------|-----|---------------------------|------------------|------|

|                                                                                  |                   | Min                       | Max       | Min                       | Max | Min                       | Max 🧄            |      |

| Address Valid to Address Don't Care (Cycle Time when Chip Enable is Held Active) | tAVAX             | 120                       | 1         | 150                       | _   | 200                       |                  | ns   |

| Chip Enable Low to Chip Enable High                                              | tELEH             | 120                       | _         | 150                       | -   | 200                       | ( <del>-</del> ) | ns   |

| Address Valid to Output Valid (Access)                                           | tAVQV             |                           | 120       | -                         | 150 | -4%                       | 200              | ns   |

| Chip Enable Low to Output Valid (Access)                                         | <sup>t</sup> ELQV |                           | 120       |                           | 150 | \\-\\\                    | 200              | ns   |

| Address Valid to Output Invalid                                                  | tAVQX             | 10                        | _         | 15                        |     | 15                        | -                | ns   |

| Chip Enable Low to Output Invalid                                                | †ELQX             | 10                        | -         | 15                        | # 1 | 15                        | -                | ns   |

| Chip Enable High to Output High Z                                                | tEHQZ             | 0                         | 40        | 0                         | 50  | 0                         | 60               | ns   |

| Output Enable to Output Valid                                                    | tGLQV             | -                         | 80        |                           | 100 |                           | 120              | ns   |

| Output Enable to Output Invalid                                                  | tGLQX             | 10                        | -         | 15                        | _   | 15                        | _                | ns   |

| Output Enable to Output High Z                                                   | tGLQZ             | 0                         | 40        | 0                         | 50  | 0                         | 60               | ns   |

| Address Invalid to Output Invalid                                                | tAXQX             | 10                        | - /       | 15                        | 1   | 15                        | _                | ns   |

| Address Valid to Chip Enable Low (Address Setup)                                 | tAVEL             | 0                         | - * * * * | 0                         |     | 0                         | -                | ns   |

| Chip Enable to Power-Up Time                                                     | tpU               | 0                         | / ( –     | 0                         | _   | 0                         | -                | ns   |

| Chip Disable to Power-Down Time                                                  | t <sub>PD</sub>   | - //                      | 30        |                           | 30  | <b>-</b> .                | 30               | ns   |

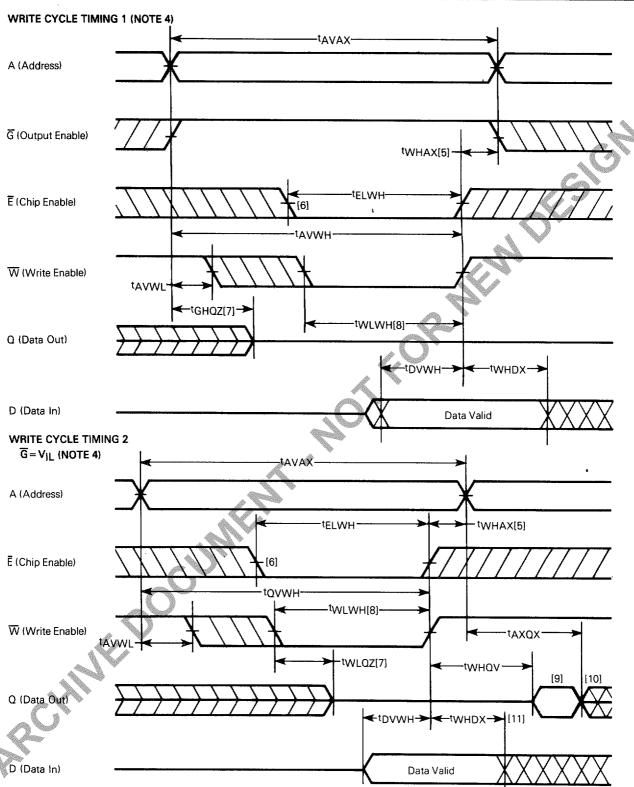

# WRITE CYCLE

| Parameter                                   | Symbol            | MCM6116-12<br>MCM61L16-12 |     | MCM6116-15<br>MCM61L16-15 |     | MCM6116-20<br>MCM61L16-20 |     | Unit |

|---------------------------------------------|-------------------|---------------------------|-----|---------------------------|-----|---------------------------|-----|------|

|                                             |                   | Min                       | Max | Min                       | Max | Min                       | Max |      |

| Chip Enable Low to Write High               | teLWH             | 70                        | _   | 90                        | _   | 120                       | _   | ns   |

| Address Valid to Write High                 | <sup>t</sup> AVWH | 105                       | -   | 120                       | -   | 140                       |     | ns   |

| Address Valid to Write Low (Address Setup)  | tAVWL             | 20                        | -   | 20                        | _   | 20                        | _   | ns   |

| Write Low to Write High (Write Pulse Width) | <sup>t</sup> WLWH | 70                        | _   | 90                        | -   | 120                       | _   | ns   |

| Write High to Address Don't Care            | tWHAX             | 5                         | _   | 10                        | _   | 10                        | _   | ns   |

| Data Valid to Write High                    | tDVWH             | 35                        |     | 40                        | _   | 60                        | -   | ns   |

| Write High to Data Don't Care (Data Hold)   | tWHDX             | 5                         | _   | 10                        | _   | 10                        | _   | ns   |

| Write Low to Output High Z                  | tWLQZ             | 0                         | 50  | 0                         | 60  | 0                         | 60  | ns   |

| Write High to Output Valid                  | tWHQV             | 5                         | _   | 10                        | _   | 10                        |     | ns   |

| Output Disable to Output High Z             | tGHQZ             | 0                         | 40  | 0                         | 50  | 0                         | 60  | ns   |

# TIMING PARAMETER ABBREVIATIONS

signal name from which interval is defined transition direction for first signal signal name to which interval is defined transition direction for second signal

The transition definitions used in this data sheet are:

H = transition to high

L = transition to low

V = transition to valid

X = transition to invalid or don't care

Z= transition to off (high impedance)

# **TIMING LIMITS**

The table of timing values shows either a minimum or a maximum limit for each parameter. Input requirements are specified from the external system point of view. Thus, address setup time is shown as a minimum since the system must supply at least that much time (even though most devices do not require it). On the other hand, responses from the memory are specified from the device point of view. Thus, the access time is shown as a maximum since the device never provides data later than that time.

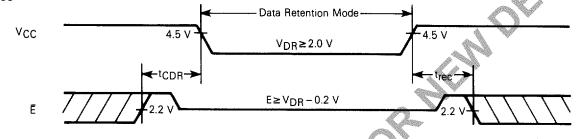

#### LOW VCC DATA RETENTION CHARACTERISTICS (TA = 0 to +70°C) (MCM61L16 Only)

| Parameter                           | Conditions                                                                                                         | Symbol            | Min    | Тур | Max | Unit       |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------|--------|-----|-----|------------|

| V <sub>CC</sub> for Data Retention  | $\overline{E} \ge V_{CC} - 0.2 \text{ V}$<br>$V_{in} \ge V_{CC} - 0.2 \text{ V or } V_{in} \le 0.2 \text{ V}$      | VDR               | 2.0    | _ ` | _   | V          |

| Data Retention Current              | $V_{CC} = 3.0 \text{ V}, \ E \ge 2.8 \text{ V}$<br>$V_{in} \ge 2.8 \text{ V} \text{ or } V_{in} \le 0.2 \text{ V}$ | <sup>I</sup> CCDR | -      | _   | 50  | μА         |

| Chip Disable to Data Retention Time | Con Describer 18/2                                                                                                 | tCDR              | 0      | _   | _   | ns         |

| Operation Recovery Time             | See Retention Waveform                                                                                             | trec              | *tAVAX |     |     | <b>≬ns</b> |

<sup>\*</sup>tAVAX = Read Cycle Time.

# LOW VCC DATA RETENTION WAVEFORM

# PACKAGE DIMENSIONS

#### NOTES

- POSITIONAL TOLERANCE OF LEADS (D),

SHALL BE WITHIN 0.25 mm (0.010) AT

MAXIMUM MATERIAL CONDITION, IN

RELATION TO SEATING PLANE AND

EACH OTHER.

- 2. DIMENSION L TO CENTER OF LEADS WHEN FORMED PARALLEL.

- 3. DIMENSION B DOES NOT INCLUDE MOLD FLASH.

|     | MILLIA         | METERS | INC       | HES             |  |

|-----|----------------|--------|-----------|-----------------|--|

| DIM | MIN            | MAX    | MIN       | MAX             |  |

| Α   | 31.37          | 32.13  | 1.235     | 1.265           |  |

| В   | 13.72          | 14.22  | 0.540     | 0.560           |  |

| C   | 3.94           | 5.08   | 0.155     | 0.200           |  |

| D   | 0.36           | 0.56   | 0.014     | 0.022           |  |

| F   | 1.02           | 1.52   | 0.040     | 0.060           |  |

| G   | 2.54           | BSC    | 0.100     | BSC             |  |

| Н   | 1.78           | 2.03   | 0.070     | 0.080           |  |

| J   | 0.20           | 0.38   | 0.008     | 0.015           |  |

| K   | 2.92           | 3.43   | 0.115     | 0.135           |  |

| L   | 15.24          |        | 0.600 BSC |                 |  |

| M   | O <sub>0</sub> | 150    | 00        | 15 <sup>0</sup> |  |

| N . | 0.51           | 1.02   | 0.020     | 0.040           |  |

This information has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Motorola reserves the right to make changes to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein. No license is conveyed under patent rights in any form. When this document contains information on a new product, specifications herein are subject to change without notice.

# **MOTOROLA** Semiconductor Products Inc. Colvilles Road, Kelvin Estate - East Kilbride/Glasgow - SCOTLAND

#### NOTES:

- 1. Write Enable (W) is High for Read Cycle.

- 2. When Chip Enable ( $\overline{\mathbf{E}}$ ) is Low, the address input must not be in the high impedance state.

- 3. Address Valid prior to or coincident with Chip Enable ( $\overline{E}$ ) transition Low.

### NOTES:

- 4. Write Enable (W) must be high during all address transitions.

- 5. tWHAX is measured from the earlier of Chip Enable (E) or Write Enable (W) going high to the end of write cycle.

- 6. If the Chip Enable (E) low transition occurs simultaneously with the Write Enable (W) low transitions or after the Write Enable (W) transition, the output remains in a high impedance state.

- 7. During this period, DQ pins are in the output state so that the input signals of opposite phase to the outputs must not be applied.

- 8. A write occurs during the overlap of a low Chip Enable ( $\overline{\mathbb{E}}$ ) and a low Write Enable ( $\overline{\mathbb{W}}$ )

- 9. Q (Data Out) is the same phase as write data of this write cycle.

- 10. Q (Data Out) is the read of the next address.

- 11. If Chip Enable (Ē) is low during this period, DQ pins are in the output state. Then the data input signals of opposite phase to the outputs must not be applied to them.