### Philips Components-Signetics

| Document No.  | 853-0153              |

|---------------|-----------------------|

| ECN No.       | 86487                 |

| Date of Issue | November 11, 1986     |

| Status        | Product Specification |

| Memory Produ  | ıcts                  |

# 82S09 82S09A 576-bit TTL bipolar RAM

#### DESCRIPTION

The organization of this device allows byte storage of data, including parity. Where parity is not monitored, the ninth bit can be used as a tag or status indicator for each word stored. Ideal for scratch pad, push down stacks, buffer memories, and other internal memory applications in which cost and performance requirements dictate a wide data path in favor of word depth.

The 82S09/09A features Open-Collector outputs, Chip Enable input, and a very low current PNP input structure to enhance memory expansion.

Ordering codes are listed in the Ordering Information Table.

The 82S09 and 82S09A devices are also processed to military requirements for operation over the military temperature range. For specifications and ordering information consult the Signetics Military Data Handbook.

#### **FEATURES**

- Address access time:

- N82S09: 45ns max

- N82S09A: 35ns max

- Write cycle time:

- N82S09/09A: 45ns max

- Power dissipation: 1.3mW/bit typ

- Input loading: -100µA max

- On-chip address decoding

- Schottky clamped

- Fully TTL ∞mpatible

- Output is non-blanked during Write

- One Chip Enable input

- Outputs: Open-Collector

#### **APPLICATIONS**

- Buffer memory

- Control register

- FIFO memory.

- Push down stack

- Scratch pad

#### **BLOCK DIAGRAM →** 01 **OUTPUT BUFFER →** O2 - 03 ADDRESS 16 × 36 MATRIX 1:16 DECODER - 04 A2 0 **→** O5 **~** 07 SENSE 9:36 MUX A5 0ю 0-INPIIT WRITE AMPL LOGIC 15 0-16 O-17 0-

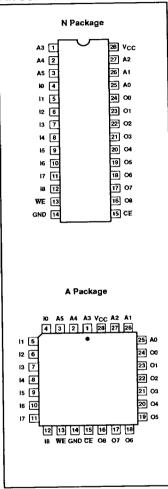

## PIN CONFIGURATIONS

ĊE

## 576-bit TTL bipolar RAM (64 $\times$ 9)

## 82S09 / 82S09A

#### ORDERING INFORMATION

| DESCRIPTION                                         | ORDER CODE          |  |  |  |

|-----------------------------------------------------|---------------------|--|--|--|

| 28-Pin Plastic Dual-In-Line<br>600mil-wide          | N82S09 N, N82S09A N |  |  |  |

| 28-Pin Plastic Leaded Chip Carrier<br>450mil-square | N82S09 A, N82S09A A |  |  |  |

#### **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL           | PARAMETER                   | RATING      | UNIT            |

|------------------|-----------------------------|-------------|-----------------|

| Vcc              | Supply voltage              | +7.0        | V <sub>DC</sub> |

| V <sub>IN</sub>  | Input voltage               | +5.5        | V <sub>DC</sub> |

| VoH              | Output voltage High         | +5.5        | V <sub>DC</sub> |

| Tamb             | Operating temperature range | 0 to +75    | ∘c              |

| T <sub>stg</sub> | Storage temperature range   | -65 to +150 | %               |

## DC ELECTRICAL CHARACTERISTICS

| SYMBOL PARAMETER | TEST CONDITIONS      |                                                  | UNIT |     |      |    |

|------------------|----------------------|--------------------------------------------------|------|-----|------|----|

|                  | 1                    |                                                  | MIN  | TYP | MAX  |    |

| input voita      | ge <sup>1</sup>      |                                                  |      |     |      |    |

| V <sub>IL</sub>  | Low                  | V <sub>CC</sub> = 4.75V                          |      |     | 0.8  | V  |

| V <sub>IH</sub>  | High                 | $V_{CC} = 5.25V$                                 | 2.0  |     | 1 1  | ٧  |

| V <sub>IC</sub>  | Clamp <sup>2</sup>   | $V_{CC} = 4.75V$ , $I_{IN} = -12mA$              | 1    |     | -1.5 | ٧  |

| Output vol       | lage <sup>1</sup>    |                                                  |      |     |      |    |

| VoL              | Low <sup>3</sup>     | V <sub>CC</sub> = 4.75V, I <sub>OL</sub> = 8.0mA |      |     | 0.5  | ٧  |

| Input curre      | nt                   |                                                  |      |     |      |    |

| I <sub>IL</sub>  | Low                  | V <sub>IN</sub> = 0.45V                          |      |     | -100 | μΑ |

| I <sub>tH</sub>  | High                 | $V_{1N} = 5.5V$                                  |      |     | 25   | μΑ |

| Output cur       | rent                 |                                                  |      |     |      |    |

| l <sub>OLK</sub> | Leakage <sup>4</sup> | $V_{CC} = 5.25V, V_{OUT} = 5.5V$                 |      |     | 40   | μΑ |

| Supply cur       | rent <sup>5</sup>    |                                                  |      |     |      |    |

| lcc              |                      | V <sub>CC</sub> = 5.25V                          |      |     | 190  | mA |

| Capacitano       | ≫e .                 |                                                  |      |     |      |    |

|                  |                      | V <sub>CC</sub> = 5.0V                           |      |     |      |    |

| CIN              | Input                | $V_{IN} = 2.0V$                                  |      | 5   |      | ρF |

| Cout             | Output               | $V_{OUT} = 2.0V$                                 | 1    | В   | 1    | ρF |

#### NOTES:

- All voltage values are with respect to network ground. Test each input one at a time

- Measured with the logic Low stored Output sink current is applied through a resistor to  $V_{CC}$ . Measured with  $V_{IH}$  applied to  $\overline{CE}$ .

Icc is measured with the Write Enable and Chip Enable inputs grounded, all other inputs at 0.45V, and the outputs open.

The operating ambient temperature ranges are guaranteed with transverse air flow exceeding 400 linear feet per minute and a 2-minute warm-up.

### **TRUTH TABLE**

| MODE      | CE | WE | ł <sub>N</sub> | O <sub>N</sub> |

|-----------|----|----|----------------|----------------|

| Read      | 0  | 1  | Х              | Stored Data    |

| Write "0" | 0  | 0  | 0              | 1              |

| Write "1" | 0  | 0  | 1              | 0              |

| Disable   | 1  | x  | X              | 1              |

X = Don't care

November 11, 1986

249

## 82S09 / 82S09A

#### **AC ELECTRICAL CHARACTERISTICS**

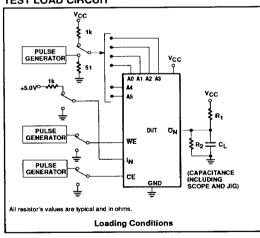

$R_1 = 600\Omega$ ,  $R_2 = 900\Omega$ ,  $C_1 = 30pF$  0°C <  $T_{amb} < +75$ °C,  $4.75V \le V_{CC} \le 5.25V$

| SYMBOL PARAMETER | то               | FROM         | N82S09       |          |          | N82S09A |          |          | UNIT |    |

|------------------|------------------|--------------|--------------|----------|----------|---------|----------|----------|------|----|

|                  | •••••            |              |              | MIN      | TYP      | MAX     | MIN      | TYP      | MAX  |    |

| Access time      | 9                |              |              |          |          |         |          |          | ,    |    |

| t <sub>AA</sub>  | Address          | Output       | Address      |          |          | 45      | 1        |          | 35   | ns |

| t <sub>CE</sub>  | Chip Enable      | Output       | Output       |          | <u> </u> | 30      |          |          | 25   | ns |

| Disable time     | e <sup>1</sup>   |              |              |          |          |         |          |          |      |    |

| t <sub>CD</sub>  |                  | Output       | Chip Enable  |          |          | 30      | l        |          | 25   | ns |

| twa              | Valid time       | Output       | Write Enable | <u> </u> |          | 30      | <u> </u> |          | 25   | ns |

| Setup and        | hold time        |              |              |          |          |         |          |          |      |    |

| twsa2            | Setup time       | Write Enable | Address      | 5        | 1        |         | 5        | 1        |      | ns |

| twha             | Hold time        | Write Enable | Address      | 5        |          |         | 5        | ļ        |      | ns |

| twsp             | Setup time       | Write Enable | Data in      | 35       |          |         | 30       |          |      | ns |

| twHD             | Hold time        | Write Enable | Data in      | 5        |          |         | 5        |          |      | ns |

| twsc             | Setup time       | Write Enable | CE           | 5        |          |         | 5        |          |      | ns |

| twic             | Hold time        | Write Enable | CE           | 5        | 1        |         | 5        | <u> </u> |      | ns |

| Pulse wid        | lth <sup>3</sup> |              |              |          |          |         |          |          |      |    |

| twp <sup>4</sup> | Write Enable     |              |              | 35       |          |         | 35       |          |      | ns |

#### NOTES:

- Measured at a delta of 0.5V from Logic level with  $R_1 = 750\Omega$ ,  $R_2 = 750\Omega$  and  $C_L = 5pF$ .

- Measured with minimum t<sub>WP</sub>.

Menimum required to gurarantee a Write into the slowest bit.

- Measured with minimum twsa.

The operating ambient temperature ranges are guaranteed with transverse air flow exceeding 400 linear feet per minute and a 2-minute warm-up.

#### **TEST LOAD CIRCUIT**

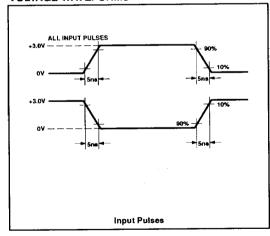

#### **VOLTAGE WAVEFORMS**

## 576-bit TTL bipolar RAM (64 $\times$ 9)

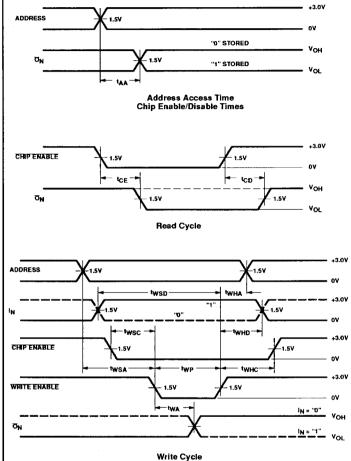

# TIMING DIAGRAMS

#### **MEMORY TIMING DEFINITIONS**

| SYMBOL           | PARAMETER                                                                                                            |

|------------------|----------------------------------------------------------------------------------------------------------------------|

| t <sub>CE</sub>  | Delay between beginning of<br>Chip Enable Low (with<br>Address valid) and when Data<br>Output becomes valid.         |

| tco              | Delay between when Chip<br>Enable becomes High and<br>Data Output is in Off-State.                                   |

| ÎAA              | Delay between beginning of valid Address (with Chip Enable Low) and when Data Output becomes valid.                  |

| twsc             | Required delay between beginning of valid Chip Enable and beginning of Write Enable pulse.                           |

| t <sub>WHD</sub> | Required delay between end of Write Enable pulse and end of valid input data.                                        |

| t <sub>WP</sub>  | Width of Write Enable pulse.                                                                                         |

| t <sub>WSA</sub> | Required delay between beginning of valid Address and beginning of Write Enable pulse.                               |

| twsp             | Required delay between beginning of valid Data Input and end of Write Enable pulse.                                  |

| twnc             | Required delay between end of Write Enable pulse and end of Chip Enable.                                             |

| t <sub>WHA</sub> | Required delay between end of Write Enable pulse and end of valid Address.                                           |

| t <sub>WR</sub>  | Delay between end of Write<br>Enable pulse and when Data<br>Output becomes valid.<br>(Assuming Address still valid.) |

| twa              | Delay between beginning of<br>Write Enable pulse and when<br>Data Output reflects<br>complement of Data Input.       |