ASYNCHRONOUS SIGNATURE PROBE OPTION 9000A-006

OPERATION MANUAL

JANUARY, 1986 2ND PRELIMINARY VERSION

John Fluke Mfg. Co., Inc.

Everett, WA 98206

# Table of Contents

| SECTION | TITLE                                                                                                                                                                                                                                                                                                                                                                                                     | PAGE                                                                                                                            |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 1       | INTRODUCTION.  1-1. TROUBLESHOOTING BEYOND THE KERNEL                                                                                                                                                                                                                                                                                                                                                     | . 1-1<br>. 1-1<br>. 1-2<br>. 1-3<br>. 1-3<br>. 1-4<br>. 1-4                                                                     |

| 2       | OPERATION                                                                                                                                                                                                                                                                                                                                                                                                 | . 2-1<br>. 2-3<br>. 2-4<br>. 2-5<br>. 2-5<br>. 2-6<br>. 2-7<br>. 2-8<br>. 2-9<br>. 2-10<br>. 2-11<br>. 2-14<br>. 2-15<br>. 2-15 |

| 3       | TEST PREPARATION.  3-1. INTRODUCTION.  3-2. CONTROL SIGNALS.  3-3. General.  3-4. START Signal.  3-5. STOP Signal  3-6. CLOCK Signal.  3-7. ENABLE Signal  3-8. GATE SECTION.  3-9. CONTROL SIGNAL EXAMPLES  3-10. SELECTING THE CONTROL SIGNAL SOURCES.  3-11. CLOCKING ON BOTH EDGES.  3-12. ESTABLISHING UUT TEST NODES  3-13. USING THE STOP COUNTER MODE  3-14. STIMULATING THE UUT  3-15. Self-Test | . 3-1<br>. 3-1<br>. 3-2<br>. 3-2<br>. 3-3<br>. 3-3<br>. 3-4<br>. 3-6<br>. 3-7<br>. 3-8                                          |

# Contents

|   | 3-16.          | Using the Troubleshooter Front Panel Functions 3-8 |

|---|----------------|----------------------------------------------------|

|   | 3-17.          | Using Programmed Routines 3-9                      |

|   | 3-18.          | Using Programmed Routines                          |

|   | 3-19.          | USING THE WAVEFORM DISPLAY                         |

|   | 3-20.          | USING THE WAVEFORM DISPLAY                         |

|   | 3-21.          | General                                            |

|   | 3-22.          | 9000A Register Usage                               |

|   | 3-23.          | LIBRARY PROGRAMS                                   |

|   | 3-24.          | Setup Hardware Program                             |

|   | 3-25.          | Arm Gate Program                                   |

|   | 3-26.          | Use of the Get Signature, Get Events, and Get      |

|   | J              | Wave Programs                                      |

|   | 3-27.          | Get Signature Program                              |

|   | 3-28.          |                                                    |

|   | 3-29.          |                                                    |

|   | 3-30.          |                                                    |

|   | 3-31.          | Send Op Code Program                               |

|   | 3-32.          | Display Waveform Program                           |

|   | 3-33.          | Append Signature Program                           |

|   | 3-371<br>2-22. | MERGE TAPE PROGRAM                                 |

|   | 3-35.          | Program Restrictions                               |

|   | 3-36.          |                                                    |

|   | 3-37.          |                                                    |

|   | 3-38.          | Program Execution                                  |

|   | 3-30.<br>3-39. |                                                    |

|   | 3-39.          |                                                    |

|   | 3-40.          | Specification Phase                                |

|   | 3-41.          |                                                    |

|   | 3-42.          | Write-Object-Tape Phase                            |

|   |                |                                                    |

|   | 3-44.          | Execute Program in Statements                      |

|   | 3-45.          | Multiple Copies of a Program 3-33                  |

| 4 | HETMC          | THE 9020A                                          |

| ~ | li 1           | INTRODUCTION                                       |

|   | 4-i.           | SIGNATURE MODULE COMMANDS                          |

|   | 4-Z.           | SENDING SIGNATURE COMMANDS TO THE MODULE 4-8       |

|   | 4-3.           | READING DATA FROM THE MODULE                       |

|   | 4-4.           | EVAMPLE DESCRIME                                   |

|   |                |                                                    |

### 1-1. TROUBLESHOOTING BEYOND THE KERNEL

The combination of the 9000 Series Microsystem Troubleshooter and the Asynchronous Signature Probe Option provide an ideal troubleshooting tool. The 9000 Series Troubleshooter, already popular for testing the kernel and for providing general stimulus, is an ideal tool for checking non-kernel areas when it is equipped with the Asynchronous Signature Probe Option.

With this option installed, the Troubleshooter can be used to solve difficult off-the-bus asynchronous problems with ease. The Troubleshooter is an ideal stimulus while the Asynchronous Signature Probe Option extends the troubleshooting ability of the combination into difficult areas such as dynamic RAM, video RAM, and exotic DMA systems.

The Asynchronous Signature Probe Option can be used in the immediate mode like any other signature equipment, but the real versatility of this option is its ability to be incorporated into 9000-type test programs. In this mode, the probe can be used in conjunction with the built-in test functions of the Troubleshooter. On-the-bus testing can be integrated with off-the-bus testing.

#### 1-2. OVERVIEW OF SIGNATURE TROUBLESHOOTING

The signature method of troubleshooting can be used to isolate faulty components in a variety of troubleshooting and test environments. While the actual procedure for using signature troubleshooting varies from equipment to equipment, the basic principle applies. The equipment under test is stimulated, by means of internally stored test routines or an external piece of stimulus equipment, in such a way that repeated signal patterns appear at meaningful test nodes. The signal pattern consists of transitions that occur at specific times relative to the basic timing of the equipment. The pattern is repeated on a regular basis and with the same timing relationships. Because the signal pattern is always the same, it may be labelled with a signature.

Since it is difficult to make a note of the signature appearing at each meaningful node using logic level and timing notation, a system is used to express the signature in four-character hexadecimal notation. Under this system, the signature equipment generates the hexadecimal signature from two types of inputs. One input monitors the signals appearing at a specific test node. The other input provides certain control signals from the UUT. The signature, which is a function of the logic level transitions and their timing relationships, is displayed on the signature equipment.

When equipment troubles exist, the signature differs from the expected signature at those nodes affected by the fault. Using the signature method of troubleshooting, the operator checks the signatures at various test nodes in the defective equipment. The present signatures are compared with those taken when the equipment was operating normally. When a signature is found that differs from the normal signature, it is usually a simple matter to trace back through the circuit to isolate the fault.

# 1-3. PURPOSE OF THE EQUIPMENT

Signature troubleshooting supplements the basic functions of the Troubleshooter. This method of troubleshooting is used in situations where the test functions of the Troubleshooter alone do not provide adequate results. This situation usually exists when a fault occurs in a circuit area that operates asynchronously with respect to the processor. In this case, the troubleshooter cannot detect the fault since it is able to examine only processor-synchronous events.

Although the Troubleshooter may not have "visibility" or access into some areas of the UUT, it is usually able to stimulate all functional areas in a consistent and repetitive manner. This type of stimulus is required to take meaningful signatures. The ability of the Troubleshooter to stimulate the UUT makes it an effective tool for signature-type fault isolation methods.

The Asynchronous Signature Option 9000A-006 provides additional Troubleshooting capability for the 9000A series Troubleshooters by using signature-type fault-isolation, events counting, and test-node waveform capture. Control signals taken from the UUT and used to establish the signature allow asynchronous operation with the Troubleshooter.

The Asynchronous Signature Option takes signatures at UUT test nodes operating at clock speeds of up to 25 MHz. For counting events, the number of data transitions appearing at the probe are accumulated up to a total of 16,777,215.

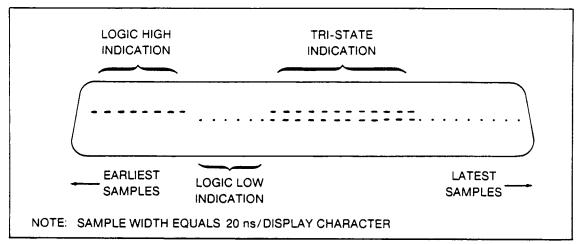

A waveform display feature permits the Troubleshooter to display a representation of the data appearing at the data probe. Thw waveform feature is useful for determining the time interval between two signal transitions. The waveform displayed shows the last 640 nanoseconds of data received by the probe before the signature-gathering operation is terminated. The display shows logic high, logic low, and tri-state levels.

During troubleshooting operations, the Troubleshooter display is used to notify the operator of all test conditions and values. The basic functions of the Troubleshooter, in conjunction with a suitable Interface Pod, provide the necessary stimulus for the unit under test (UUT) during signature troubleshooting operations.

All of these features may be accessed while you are operating the Troubleshooter in the immediate mode by using the keyboard and display. All features may also be accessed by the use of test programs that pass control and test results through registers.

# 1-4. EQUIPMENT DESCRIPTION

### 1-5. General

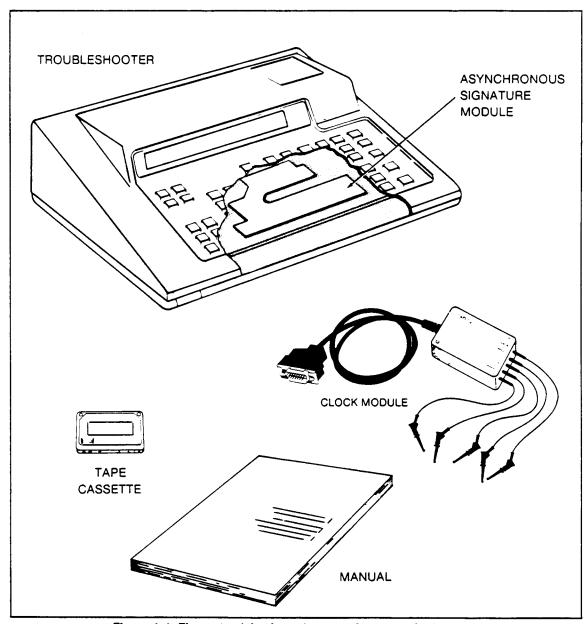

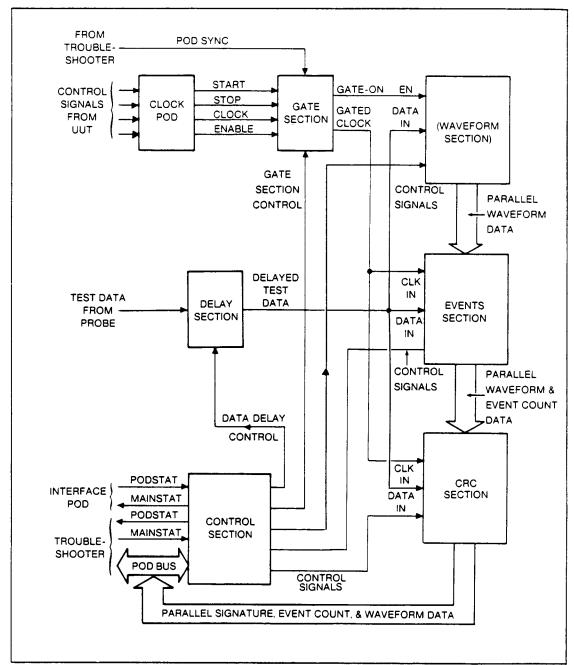

As shown in Figure 1-1, the Asynchronous Signature option consists of the Asynchronous Signature Module mounted within the Troubleshooter case, a separate Clock Module that connects to the Troubleshooter, and operating programs contained on a magnetic tape cassette. (For the Model 9020, programs are executed from within the host computer.)

Figure 1-1. Elements of the Asynchronous Signature Option

### 1-6. The Clock Module

The Clock Module provides interface and protection between the Troubleshooter and the UUT. Interface is required to effectively isolate the sources of the clock, start, stop, and enable signals located on the UUT from the input of the Troubleshooter. A fuse in the ground line provides the necessary protection. An input to the Troubleshooter from the Clock Module provides an indication of the fuse condition.

The Clock Module connects to the Troubleshooter with a 15-pin connector located below the front panel of the Troubleshooter. Connection to the UUT is made by up to five clip leads that protrude from the Clock Pod. A clip lead is provided for each of the control signal inputs (start, stop, clock, and enable), and one is provided for the ground connection to the UUT.

# 1-7. The Asynchronous Signature Module

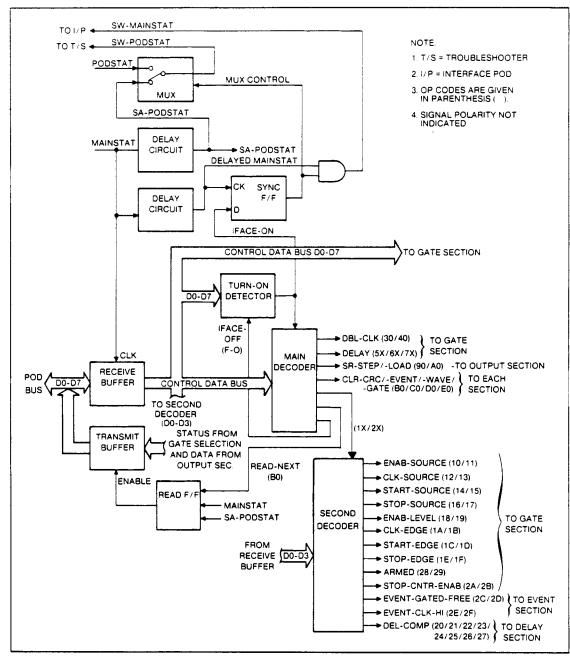

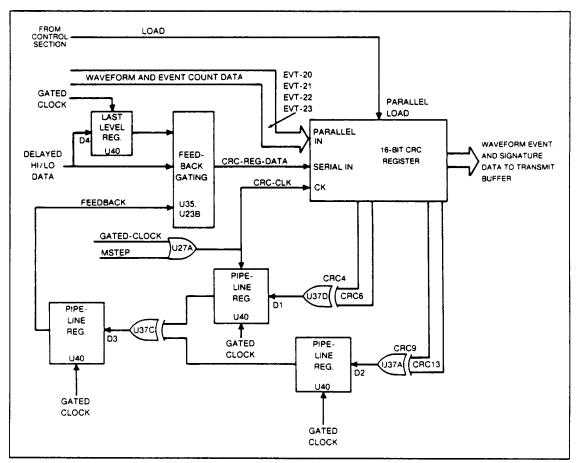

The Asynchronous Signature Module is a printed circuit board located within the Troubleshooter. It accepts the start, stop, clock, and enable signals from the Clock Module, and the data stream from the Troubleshooter data probe. The Asynchronous Signature Module uses these inputs to generate the corresponding signature, event count, and waveform data. The module sends the calculated signature and event count over the pod bus to the Troubleshooter for display on the front panel.

In addition to the signature and events count functions, a set of registers within the module stores the latest 640 nanoseconds of the data stream gathered by the data probe. The module sends this data to the Troubleshooter for display on the front panel as a waveform.

# 1-8. The Cassette Tape

The Asynchronous Signature Option in the models 9005A and 9010A is operated by a series of programs contained on a magnetic tape cassette. Once the programs are loaded into the Troubleshooter RAM, operation of the Troubleshooter in the signature mode is afforded by several front panel keys. Appropriate displays provide the necessary interaction between the Troubleshooter and the operator during signature operations. Operation of the 9020A is a function of the host computer or instrument controller.

# 1-9. ORGANIZATION OF THIS MANUAL

This manual documents the Asynchronous Signature Option to the 9000A series Troubleshooters. The manual provides information for the operator of the equipment (Operation), for the test engineer (Test Preparation), for the programmer (Remote Control of the 9020A), and for the service personnel (Theory of Operation and Maintenance). Operation, programming, and repair of the basic 9000A Series Troubleshooter are documented in the appropriate manual(s).

### 1-10. SPECIFICATIONS

Table 1-1 lists the specifications for the Asynchronous Signature Probe Option.

Start Event: A selectable positive or negative edge on the Start line,

or the Sync signal from the Interface Pod (when used).

Stop Event: A selectable positive or negative edge on the Stop line,

or the Sync signal from the Interface Pod (when used).

Clock Event: A selectable positive or negative edge, or a combination

of both, on the Clock line; or the Sync signal from the

Interface Pod (when used).

Enable Event: A selectable positive or negative level on the Enable line.

ELECTRICAL

Start, Stop, Clock, and Enable lines (through Clock Module):

Impedance: 10 pF/44 kilohms nominal

Threshold: 1.4 volts

Overvoltage: +/-15 volts maximum

Clock Module ground lead is fuse-protected

Data Channel: Uses standard data probe supplied with 9000A mainframe

TIMING

Start, Stop, Clock, and Enable signals: 0 to 25 MHz

Data Signals: 0 to 12.5 MHz

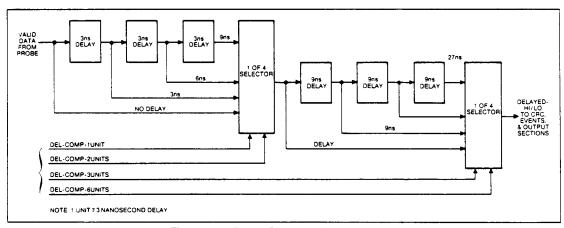

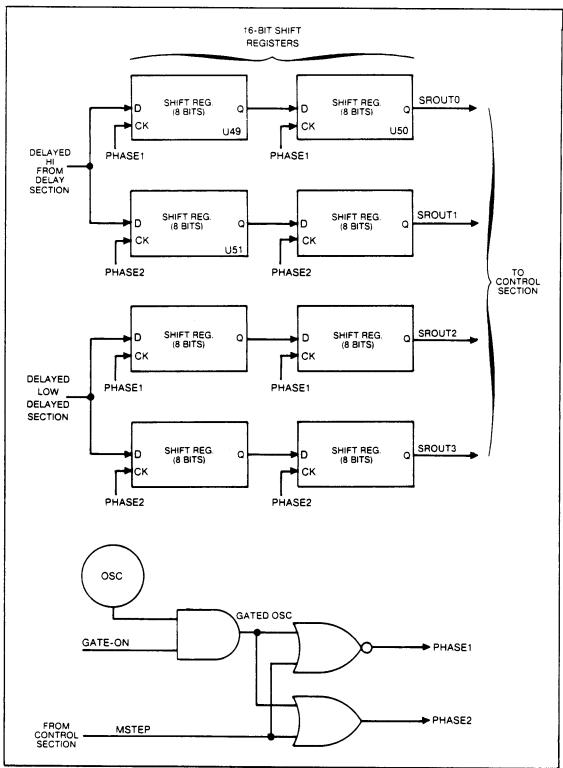

Programmable delay in data path: 0 to 36 nanoseconds

Programmable delay increment: 3 nanoseconds

### FUNCTIONS

Nodal Signatures: 4-digit CRC-16 algorithm

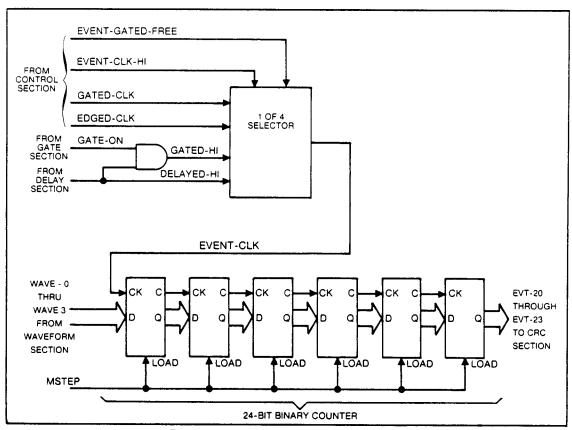

Transition Counting: 24 bits (0 to 16,777,216 counts)

Waveform Capture: 32 consecutive data samples at 20-nanosecond intervals.

High, low, and tristate levels. The 32 samples

terminate with the stop event.

### SYSTEM COMPATIBILITY

Can be installed in the Fluke 9005A, 9010A, and 9020A mainframes.

# PROGRAM CONTROL

All functions of the Asynchronous Signature Probe Option can be commanded from within a 9010A or 9005A user program. All data measured by this option may be tested in the program. A test program controlling the 9020A may command all option functions and retrieve measured data.

#### ENVIRONMENTAL

Storage: -40 to +80 degrees C, rh <75% non-condensing Operating: 0 to +50 degrees C, rh <75% non-condensing

0 to +40 degrees C, rh <95% non-condensing

#### 2-1. INTRODUCTION

This section provides general information to assist in the operation of the 9005A and 9010A Troubleshooters equipped with the Asynchronous Signature Module. For operation of the Model 9020A Troubleshooter equipped with the Asynchronous Signature Module, refer to Section 6, Using the 9020A.

The information contained in this section applies to the Asynchronous Signature Module in a general sense and does not pertain to a specific troubleshooting/repair situation. This is true because a particular piece of equipment being tested or repaired requires specific user-supplied test and test setup documentation. The signature type test documentation for a particular UUT is typically provided by the test engineer for the equipment. The test documentation should follow the guidelines set forth in Section 3, Test Preparation.

The information provided in this section describes:

- 0 The Troubleshooter keys that function in the signature mode

- O How to make connections to the UUT

- O How to enter the signature mode

- O How to verify operation of the signature mode

- O How to initialize the Troubleshooter in the signature mode

- O How to take signature, event count, and waveform readings

As already mentioned, the operating information contained in this section is general in nature. The documentation provided by the test engineer supports the above operations by providing initialization parameters, connection points on the UUT for the Clock Module, location of test nodes, as well as valid signatures, event counts, and waveforms. Be sure to obtain this documentation before beginning to test or troubleshoot equipment using the Troubleshooter equipped with the Asynchronous Signature Module.

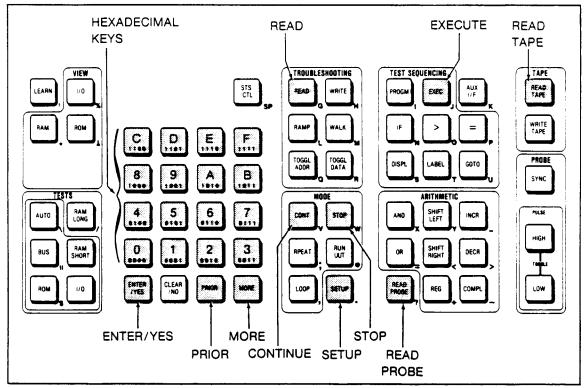

### 2-2. TROUBLESHOOTER FRONT PANEL

When you are operating the Troubleshooter in the signature mode, the functions of several front-panel keys differ from the functions described in the Troubleshooter Operation Manual. Figure 2-1 highlights the location of the Troubleshooter keys that are operative in the signature mode of operation.

- O The SETUP key allows initialization of the Troubleshooter when it is operated in the signature mode. Initialization consists of selecting control signal edges (rising or falling), the ENABLE signal level, the amount of delay compensation, and the source of the START, STOP, and CLOCK signals (UUT or interface pod).

- O The READ TAPE key causes the Troubleshooter to download the contents of the supplied cassette into memory.

- O The READ PROBE key causes the Troubleshooter to read the data appearing at the probe tip. As a result of the Read operation, the Troubleshooter computes and displays the signature and the events count. The troubleshooter also stores a portion of the test signal waveform for display on the front panel when you press the MORE key.

- O The READ key causes the Signature Module to halt a signature/event count (Read Probe) operation and displays the resulting signature and events count. The waveform is available when you press the MORE key.

- O The STOP key allows other Troubleshooter functions to be performed. To return to the signature mode, press the EXEC, 1, and ENTER keys.

- O The CONT key causes the Troubleshooter to continue operation at the point where the STOP key was pressed, provided no other key is pressed.

- O The EXEC key allows execution of the programs previously loaded into the Troubleshooter memory.

- The MORE key causes the Troubleshooter to scroll the display to the next "line," such as going from signature/event count to waveform display. Where several "lines" exist, such as in the setup procedure, this key allows the sequential display of each line.

- O The PRIOR key causes the Troubleshooter to scroll the display to the previous "line."

- O The numeric keys may be used during initialization procedures only to enter operation parameters for the various features and control signals.

Figure 2-1. Troubleshooter Keys Used With the Signature Option

# 2-3. BACKING UP THE TAPE CASSETTE

Operation of the signature feature depends on several programs contained in the supplied cassette. To ensure that these programs are always available, even in the event of a problem with the cassette, it is good practice to make a back-up copy on a blank cassette before you use it the first time. To make a back-up copy of both sides of the cassette, proceed as follows:

1. Insert the master cassette into the tape drive with side A up and press the READ TAPE key on the Troubleshooter. The display reads

READ TAPE - ARE YOU SURE?

2. Press the ENTER/YES key, and while the Troubleshooter reads and checks the contents of the cassette, the display reads

READ TAPE WAIT

When the Read Tape operation is complete, the display reads

READ TAPE OK

3. Remove the cassette from the tape drive and install a blank cassette, with side A up.

4. Press the WRITE TAPE key, and the display reads

WRITE TAPE - ARE YOU SURE?

5. Press the ENTER/YES key, and while the Troubleshooter writes the the contents of the troubleshooter memory the display reads

WRITE TAPE WAIT

When the Write Tape operation is complete, the display reads

WRITE TAPE OK

- 6. Remove the cassette from the tape drive, turn it over and repeat steps 1 through 5 for side B.

- 7. Remove the cassette from the tape drive, label it, and store it in a safe place.

### 2-4. ENTERING THE SIGNATURE MODE

The first step in signature mode operation is to load the programs contained on the supplied cassette into the Troubleshooter's memory. To load these programs, proceed as follows:

1. Insert the cassette (with side A up) into the tape drive and press the READ TAPE key on the Troubleshooter. The display reads

READ TAPE - ARE YOU SURE?

2. Press the ENTER/YES key, and while the Troubleshooter reads and checks the contents of the cassette the display reads

READ TAPE WAIT

When the Read Tape operation is complete, the display reads

READ TAPE OK

Remove the cassette from the tape drive.

3. Press the EXEC key, and the display reads

EXECUTE PROGRAM (flashing cursor)

4. Enter 0 and press the ENTER/YES key. The display indicates that the Troubleshooter is ready for operation in the signature mode when it reads

ASYNC SIGNATURE PROBE READY

# 2-5. INITIALIZATION (SETUP) OF THE SIGNATURE FUNCTION

#### 2-6. Introduction

Before to operating the Troubleshooter in the signature mode, you must load the operating programs from the cassette (as described under Entering the Signature Mode), and make the following selections on the Troubleshooter:

- O Polarity of the control signals

- O Source of the control signals

- O Count limit for the CLOCK signal

- O Amount of delay compensation

- O Mode of the events counter (gated or free-running)

Since removing power causes the previous selections to be lost, these selections must be made each time the Troubleshooter is powered-up. The selection procedures presented in the following paragraphs assume that the factory-set default parameters for the initial display of each selection are made. In actual practice, the initial display is the last parameter selected since power was applied to the Troubleshooter.

In the setup procedures, the MORE and PRIOR keys are used to scroll through setup parameters. When a particular parameter is displayed, the 1 and 2 keys allow you to select the desired field for the parameter. The setup procedures that follow explain in detail the selection of each setup parameter. Once you have completed the setup procedures one time, simple use of the MORE, PRIOR, 1, and 2 keys will allow you to perform the setup operation.

# 2-7. Selecting the START Signal

The START signal may be a positive-going or negative-going edge, taken from the start lead of the Clock Module or the SYNC signal generated by the Interface Pod. Select the START signal for this particular UUT as follows:

1. Press the SETUP key, and the display reads

START ON 1) RISING 2) EXT START

At this point it is possible to:

- a. Select the START signal parameters displayed above: positive-going edge and external source (UUT via the Clock Module), and then proceed to Selecting the STOP Signal. Perform step 4.

- b. Select the START signal to be (pod SYNC) from the Interface Pod. Proceed to step 2.

- c. Select a negative-going (falling edge) for the START signal. Proceed to step 3.

- 2. If you wish to select the SYNC signal generated by the Interface Pod as the source of the START signal, press the 2 key. The display reads

START ON 1) <edge type> 2) POD-SYNC

To change the display back to the previous selection, press the 2 key a second time.

If you wish to select the falling edge of the selected START signal, press the 1 key. The display reads

START ON 1) FALLING 2) < source >

To change the display back to the previous selection, press the 1 key a second time.

4. Press the MORE key, and proceed to Selecting the STOP Signal.

## 2-8. Selecting the STOP Signal

The STOP signal may be a positive-going edge or negative-going edge taken from the stop lead of the Clock Module or the sync signal generated by the Interface Pod. Select the STOP signal for this particular UUT as follows:

1. If you are selecting STOP signal parameters only, press the SETUP key and the display reads

START ON 1) <edge type> 2) <source>

Press the MORE key and the display reads

STOP ON 1) RISING 2) EXT STOP

At this point it is possible to:

- a. Select the STOP signal parameters displayed above (positive-going edge STOP signal external from the UUT via the Clock Module stop lead) and proceed to CLOCK signal selection. Proceed to step 4.

- b. Select the STOP signal to be from the InterFace Pod (pod SYNC). Proceed to step 2.

- c. Select a negative-going (falling edge) for the STOP signal. Proceed to step 3.

- 2. If you wish to select the sync signal generated by the Interface Pod, as the source of the STOP signal, press the 2 key. The display reads

STOP ON 1) <edge type> 2) POD-SYNC

To change the display back to the previous selection, press the 2 key a second time.

3. If you wish to select the falling edge of the selected STOP signal press the 1 key. The display reads

STOP ON 1)FALLING 2) (source)

To change the display back to the previous selection, press the 1 key a second time.

4. Press the MORE key, and proceed to Selecting the CLOCK signal.

# 2-9. Selecting the CLOCK Signal

The CLOCK signal may be a positive-going edge, a negative-going edge, or both. It may be taken from the clock lead of the Clock Module or the sync signal generated by the Interface Pod. Select the CLOCK signal for this particular UUT as follows:

1. If you are selecting CLOCK signal parameters only, press the SETUP key, and the display reads

START ON 1) <edge type 2) source>

Press the MORE key until the display reads

CLOCK ON 1) RISING 2) EXT CLOCK

At this point it is possible to:

- a. Select the CLOCK signal parameters displayed above (positive-going edge and CLOCK signal external via the Clock Pod), and proceed to ENABLE signal selection. Proceed to step 4.

- b. Select the CLOCK signal to be the pod SYNC signal from the Interface Pod. Proceed to step 2.

- c. Select a negative-going (falling) edge, or both rising and falling edges, for the CLOCK signal. Proceed to step 3.

- 2. If you wish to select the SYNC signal generated by the Interface Pod as the source of the CLOCK signal, press the 2 key. The display reads

CLOCK ON 1) <edge type> 2) POD-SYNC

To change the display back to the previous selection, press the 2 key a second time.

3. If you wish to select the falling edge of the selected CLOCK signal, press the 1 key. The display reads

CLOCK ON 1)FALLING 2) (source)

If you wish to select both edges of the selected CLOCK signal (double the clock), press the 1 key a second time, and the display reads

CLOCK ON 1)BOTH EDGE 2) (source)

To change the display back to the previous selection, press the 1 key a third time.

4. Press the MORE key, and proceed to Selecting the ENABLE signal.

# 2-10. Selecting the ENABLE Signal

The ENABLE signal may be a positive or a negative level, and it is taken from the enable lead of the Clock Module, or it is selected to be enabled at all times during signature operation. Select the ENABLE signal for this particular UUT as follows:

1. If you are selecting ENABLE signal parameters only, press the SETUP key and the display reads

START 1) <edge type> ,2) <source>

Press the MORE key until the display reads

ENABLE 1)ALWAYS

At this point it is possible to:

- a. Select this function to be enabled regardless of the state of the ENABLE line and proceed to the clock count limit selection. Proceed to step 3.

- b. Select the ENABLE signal to be external via the Clock Module. Proceed to step 2.

- 2. If you wish to set the function to the external mode and high level, press the 1 key. The display reads

ENABLE 1)ON EXT ENABLE 2)HIGH

If you wish to select a low level for the selected ENABLE signal, press the 2 key. The display reads

ENABLE 1)ON EXT ENABLE 2)LOW

To change the display back to the previous selection, press the 1 key a second time.

3. Press the MORE key, and proceed to Selecting the Stop Counter.

# 2-11. Selecting the Stop Counter

The stop count is the number of gated clock pulses that can occur before the Signature Module invokes a stop to terminate the gate time. Select the stop count as follows:

1. If you are selecting the stop count only, press the SETUP key, and the display reads

START ON 1) <edge type> 2) <source>

Press the MORE key until the display reads

STOP COUNTER 1) DISABLED

At this point it is possible to:

- a. Leave the clock count function disabled, and proceed to Selection of Delay Compensation. Proceed to step 3.

- b. Enable the clock count function, and specify a number of clock edges to be counted. Proceed to step 2.

- 2. To enable the clock count function and specify a count limit, press the 1 key. The display reads

CLOCK LIMIT 1)ENABLED 2) = cprompt>

Using the numeric keys, enter the desired number of clock edges in the range of 1 to 4095 (decimal) and press the ENTER key.

The stop counter function can be disabled by pressing the 1 key a second time.

3. Press the MORE key, and proceed to Selecting the Data Delay Compensation.

# 2-12. Selecting the Data Delay Compensation

The amount of data delay is selected in increments of approximately 3 nanoseconds, over the range of zero to 36 nanoseconds. Select the amount of delay as follows:

1. If you are selecting data delay compensation only, press the SETUP key, and the display reads

START ON 1) <edge type> 2) <source>

Press the MORE key until the display reads

DATA DELAY COMP 1)<0 or last selected value> UNITS

At this point it is possible to:

- a. Leave the delay compensation as displayed, and proceed to Selecting Event Count Parameters. Proceed to step 3.

- b. Select a specific value of delay. Proceed to step 2.

- 2. Select the desired amount of the delay (each unit equals approximately 3 nanoseconds) by entering numerical number of desired (zero through 12 units).

- 3. Press the MORE key, and proceed to Selecting Event Count Parameters.

### 2-13. Selecting Event Count (Data Transition) Parameters

The event count function can be configured to operate in two basic modes: gated operation and free-running operation. When operated in the gated mode, the events counter counts data transitions appearing at the probe tip only during the gate-time (the period between the selected START and STOP signals), and the event counter is reset to zero at the beginning of each period. When the events counter is operated in the free-running mode, it counts data transitions as long as the probe is connected to the UUT and no other Troubleshooter key is pressed.

Select the event count parameters for this particular UUT as follows:

1. If you are selecting event counter parameters only, press the SETUP key, and the display reads

START ON 1) <edge type> 2) <source>

Press the MORE key until the display reads

DATA TRANSITION COUNT 1)GATED

At this point it is possible to:

- a. Leave the event counter parameters displayed above (gated operation).

- b. Select the free-running mode. Proceed to step 2.

- 2. If you wish to operate the events counter in the free-running mode, press the 1 key. The display reads

DATA TRANSITION COUNT 1) FREE RUN

To change the display back to the previous selection, press the 1 key a second time.

### 2-14. VERIFYING EQUIPMENT OPERATION

Before operating the Troubleshooter in the signature mode, you may want to verify that the signature feature is operational. This verification procedure is brief and does not attempt to check performance of the equipment against the specifications. The procedure verifies only that the signature function is operating normally.

The verification check consists of the following basic operations:

- O Entering the signature mode

- O Making connections to the data probe

- O Setting the Troubleshooter to pulse the probe

- O Initiating a Read Probe Operation

- O Reading the signature and event count

Verify operation of the Signature Module as follows:

- 1. Connect the probe to its connector on the front underside of the Troubleshooter.

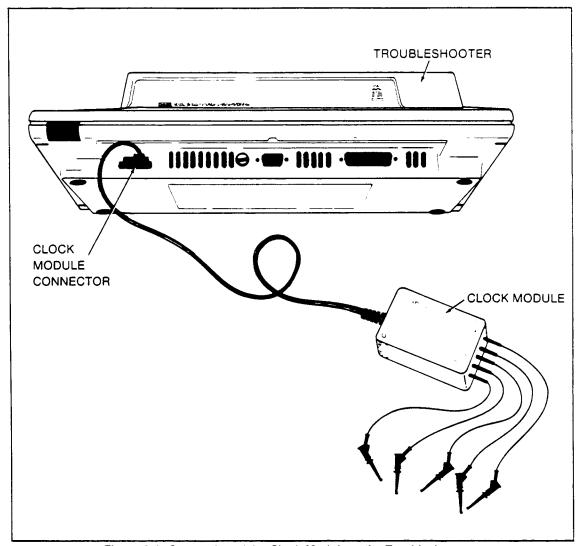

- 2. Connect the Clock Module cable to the Troubleshooter as shown in Figure 2-2.

Figure 2-2. Connection of the Clock Module to the Troubleshooter

- 3. Connect the start and clock (green and yellow) leads of the Clock Module to the tip of the data probe.

- 4. Connect the stop (red), enable (blue), and ground (black) leads to the data probe ground lead.

- 5. Connect a 33-ohm, 1/4-watt resistor across the group of connections made in step 3 and the group of connections made in step 4. (The resistor connects so that the data probe tip is shunted to the ground lead.)

- 6. Switch on the Troubleshooter, and enter the signature mode as described under Entering the Signature Mode.

- 7. For the Model 9020A, run the example program listed in Section 6, paragraph 6-5. For the 9005A and 9010A, refer to Initialization of the Signature Function and:

- O Set the start signal to a rising edge

- O Sect the clock signal to a falling edge

- O Set the stop counter to 256 (The clock limit count provides an end to the gate time in lieu of a stop signal.)

- O Set the data transition (event) count to gated

- O Set the enable signal to low

- O Set the data delay to 4

- 8. Press the PULSE HIGH key on the Troubleshooter.

- 9. Press the READ PROBE key, and the display reads

WAIT

followed by

SIGNATURE BB34 COUNT 256

Any other signature or count indicates a problem with the Signature Module, the Clock Module, or the Troubleshooter.

# 2-15. MAKING CONNECTIONS TO THE UUT

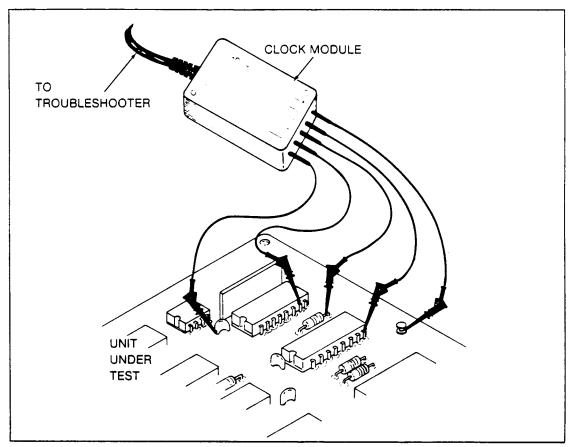

Both the Data Probe and the Clock Module must be connected to the UUT during signature operations. Connecting the Data Probe is simply a matter of touching it to the test node; however, connecting the Clock Module to the UUT requires several temporary connections to the UUT. These connections to the UUT include clock, start, stop, ground, and enable. Refer to the labels on the Clock Module case for identification of the Clock Module control signal leads.

With reference to Figure 2-3 and the documentation provided for the UUT, connect the Clock Module leads to the start, stop, clock, and ground points on the UUT. If the enable function is to be used, connect the enable lead of the Clock Module to the UUT.

Figure 2-3. Connection of the Clock Module to the UUT (Typical)

# 2-16. TAKING SIGNATURES AND EVENT COUNTS

### 2-17. Introduction

Taking a signature, although a simple operation, requires that the following operations be completed:

- O The signature mode programs must be loaded and selected on the Troubleshooter. (Refer to Entering the Signature Mode.)

- O If necessary, initialization (setup) parameters must be selected. (Refer to Initialization (Setup) of the Signature Function.)

- O Connections of the Clock Module to the Troubleshooter and UUT must be made. (Refer to Making Connections to the Troubleshooter and Making Connections to the UUT.)

- O The documentation (such as connection details, test points, and signatures) for the particular UUT being checked must be referenced.

- O The UUT must be provided with a suitable stimulus.

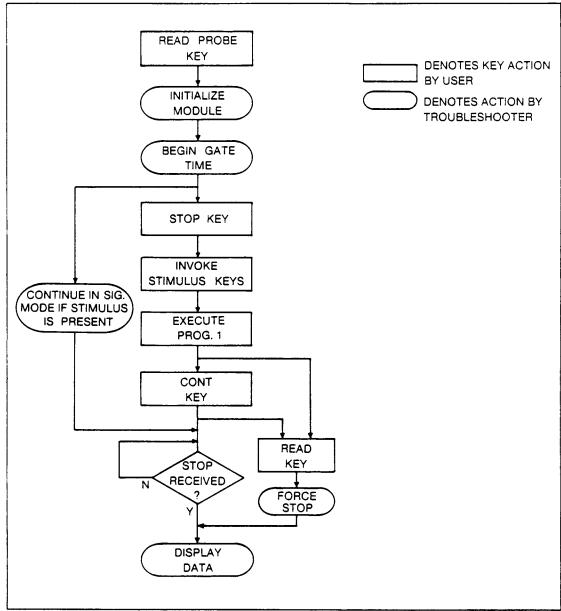

Figure 2-4. Signature Taking Flow Chart (Typical)

### 2-18. Using the Troubleshooter to Stimulate the UUT

Each UUT must be stimulated as specified in the test documentation for the particular UUT. The UUT may be stimulated by means of the Troubleshooter (by the front panel keys or by executing one or more programs) or by some other method such as self-test. If the Troubleshooter is to be used to stimulate the UUT, refer to the following procedure. If the Troubleshooter will not be used for UUT stimulus, refer to Using Non-Troubleshooter Stimulus.

Note that once operation of the Troubleshooter is initiated in the signature mode, this mode is placed in the background while the Troubleshooter stimulates the UUT and the Signature Module reads the signature. When the stimulus operation is complete, operation in the signature mode is resumed to read the signature, event count, and waveform. Refer to Figure 2-4.

Perform signature and event count operations as follows:

1. Touch the data probe to the desired test node, and press the READ PROBE key. The display reads

WAIT

This display indicates that the Asynchronous Signature Module is ready to receive (or may have already received) the necessary START signal, followed by the test data, and STOP signal.

2. Press the STOP key to leave the signature program and use the Troubleshooter to stimulate the UUT. (The Signature Module remains active and ready to receive control signals via the Clock Module and test data via the probe.)

Stimulate the UUT according to the instructions provided with the UUT test documentation. Stimulating the UUT may consist of some key-selectable test on the Troubleshooter, such as a RAMP, TOGGL DATA, etc. Or the stimulus may be provided by executing a program, specially written to stimulate this UUT, and previously loaded into the Troubleshooter memory.

3. To read the signature and event count resulting from the stimulus operation, press the EXEC key and the display reads

EXECUTE PROGRAM (flashing cursor)

Enter 1 and press the ENTER/YES key. The display indicates that the Troubleshooter has returned to operation in the signature mode when it reads

ASYNC SIGNATURE PROBE READY

- 4. To display the signature and event count, press either the CONT key (step 4a) or the READ key (step 4b).

- a. The CONT key allows the Signature Module to continue the Read Probe operation if it is not already terminated by the occurrence of a STOP signal. If the Read Probe operation is still in progress (no STOP signal received yet), the display reads

WAIT

and then when the STOP signal is received, the display reads

SIGNATURE XXXX COUNT yyyyyyy

where xxxx is the signature and yyyyyyyy is the event count.

If the WAIT display persists for a longer than normal time, it is likely that a STOP signal has not been received. In this case. Proceed to step b.

b. The READ key stops the read probe operation whether or not a STOP signal has been received, and the display reads

SIGNATURE xxxx COUNT yyyyyyy

where xxxx is the signature, and yyyyyyyy is the event count.

If the test has been designed to end with a STOP signal, pressing the READ key before the stop is received will yield invalid signatures and counts.

- 5. To display the waveform representing the last 640 nanoseconds of data occurring during the Read Probe operation, press the MORE key.

- 6. To display the signature and event count, press the PRIOR key. The PRIOR and MORE keys toggle the display between the signature/count and waveform capture displays.

### 2-20. Using Non-Troubleshooter Stimulus

When you are taking signatures without using the Troubleshooter to stimulate the UUT, it is unnecessary to suspend operation in the signature mode. With non-Troubleshooter stimulus, it is only necessary to take signature readings as the UUT is stimulated, either on a continuous basis, or on command at the stimulus source. Proceed as follows to take signatures when you are not using the Troubleshooter as the source of stimulus:

1. Touch the data probe to the desired test node, and press the READ PROBE key. The display reads

WAIT

indicating that the Asynchronous Signature Module is ready to receive (or may have already received) the necessary START signal, followed by the test data, and STOP signal.

- 2. Stimulate the UUT according to the instructions provided with the UUT test documentation.

- When the STOP signal is received, the display reads

SIGNATURE xxxx COUNT yyyyyyy

where xxxx is the signature and yyyyyyyy is the event count.

- a. If the WAIT display persists for a longer than normal time, it is likely that a STOP signal has not been received via the Clock Module. In this case, press the READ key to display the signature and event count readings.

- b. The READ key stops the read probe operation whether a STOP signal has been received or not, and the display reads

SIGNATURE XXXX COUNT YYYYYYYY

where xxxx is the signature, and yyyyyyyy is the event count.

- 4. To display the waveform representing the last 640 nanoseconds of data occurring during the Read Probe operation, press the MORE key.

- 5. To display the signature and event count, press the PRIOR key.

- 6. The PRIOR/MORE keys toggle the display between the signature/count and waveform capture displays.

### 3-1. INTRODUCTION

This section contains information regarding the implementation of signature, event count, and waveform troubleshooting methods for a particular model of UUT. Implementation consists of preparing a particular model of UUT for testing (usually by the test engineer). One-time implementation is required before any meaningful testing of the UUT can take place using the signature option. In preparing a UUT for this type of testing, the following tasks must be completed:

- O Determine the polarity and source of the control signal (START, STOP, CLOCK, and ENABLE) within the UUT.

- O Determine the nodes within the UUT that provide meaningful test signals.

- O Determine any special test conditions required such as delay compensation, setting the gate period to a specific number of CLOCK pulses, etc.

- O Determine the required stimulus condition that causes the UUT to generate consistent and repeatable test data at the chosen test nodes.

- O Take signature and/or event counts at the selected test nodes of a known-good UUT, and annotate a schematic diagram with the signatures and event counts. A list of the signatures and event counts could also be used.

- O Provide documentation to the technician that details the above selections, considerations, and expected test results so that efficient and effective troubleshooting/testing can be performed.

## 3-2. CONTROL SIGNALS

#### 3-3. General

In addition to the test pattern or data stream taken from the UUT, the signature module must also receive certain control signals. These control signals, taken from the UUT by the Clock Module, or possibly from the Troubleshooter's Interface Pod, include the START, STOP, CLOCK, and ENABLE signals. The following paragraphs briefly describe these signals since the user must be aware of their role in the signature operation.

### 3-4. START Signal

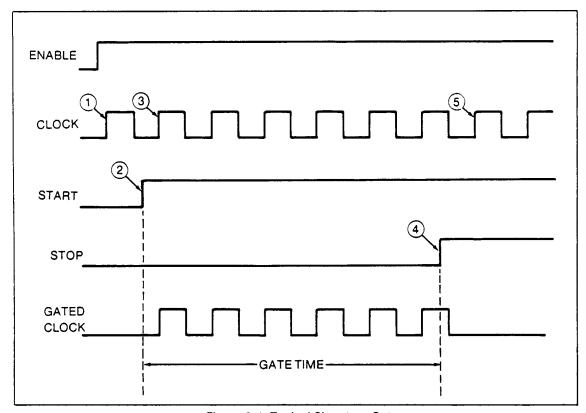

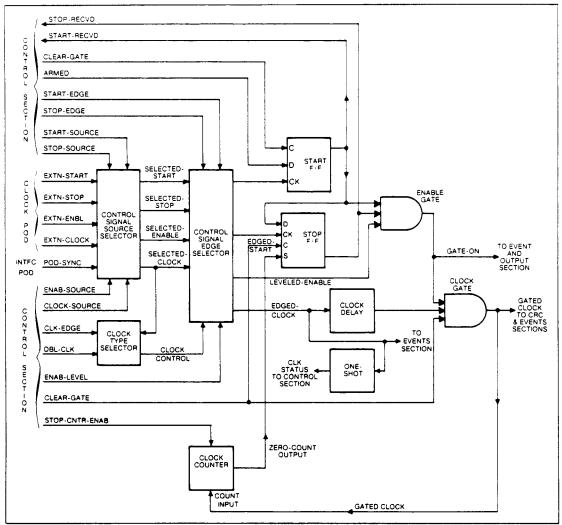

The START signal may be a positive-going or negative-going edge supplied by the UUT or the Interface Pod SYNC signal, as selected during initialization. The gate section within Signature Module is armed or preset to accept the START signal level change as shown in note 2 of Figure 3-1. (Rising CLOCK edges are chosen for this example.) The gate section operates so that it then passes the next valid CLOCK signal edge, shown in note 3 of Figure 3-1. Clocking of signature data (test pattern) begins with the occurrence of this CLOCK edge (note 2 of Figure 3-1).

Figure 3-1. Typical Signature Gate

# 3-5. STOP Signal

The STOP signal is also level sensitive, and it may be supplied by either the UUT or the Interface Pod SYNC signal. Note 4 in Figure 3-1 shows the typical STOP level change. The STOP signal allows any already-gated clock signal to be completed. The next valid CLOCK edge, following the STOP signal, does not clock in any signature data, and signature computation is halted (note 5 of Figure 3-1).

# 3-6. CLOCK Signal

The typical CLOCK signal is also shown in Figure 3-1. The Troubleshooter allows you to select either positive-going edges, negative-going edges, or both positive-going and negative-going edges for the CLOCK signal. You can also select the source of the signal (the Troubleshooter Interface Pod SYNC signal or the CLOCK lead of the Clock Module). The CLOCK edge selected must be synchronized to the valid data times of the circuit being probed with the Troubleshooter data probe. A correctly selected CLOCK edge prevents errors from occurring during unsettled signal times, such as during tri-state conditions and signal transition times.

# 3-7. ENABLE Signal

The ENABLE signal, level-sensitive instead of edge-sensitive, provides a means of inhibiting or enabling the computation of the signature. This signal enables the CLOCK signal developed within the Signature Module to clock-in the test data appearing at the probe tip. The ENABLE signal provides a means of controlling the signature computation period of the measurement.

### 3-8. GATE SECTION

All control signals are applied to the gate section of the Signature Module. The function of the gate section is to accept START, STOP, CLOCK, and ENABLE signals from the Clock Module (or possibly from the Interface Pod in the case of the START, STOP, and CLOCK signals) and output a gated CLOCK signal to the signature generator and events counter. The following statements describe the general operation of the gate section:

- O The gate section accepts a START edge only if it is armed.

- Once armed, the gate section assumes the started condition at the time of the first START edge.

- Once started, the gate section stops on the first STOP edge.

- O The ENABLE signal does not affect the recognition of START and STOP edges.

- O The gate is considered on only after it has been started and has not yet been stopped, and the ENABLE signal is asserted.

#### 3-9. CONTROL SIGNAL EXAMPLES

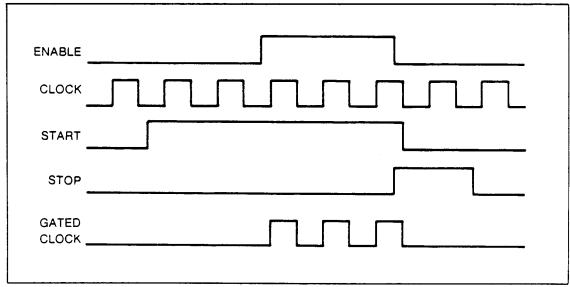

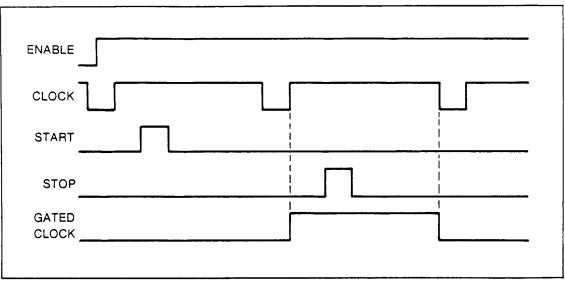

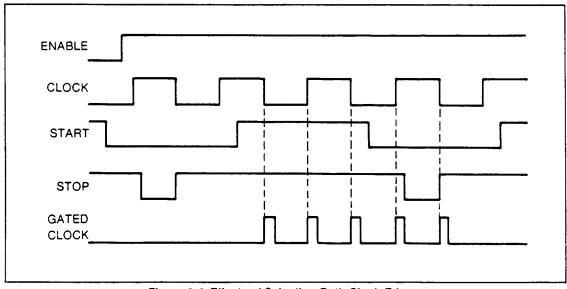

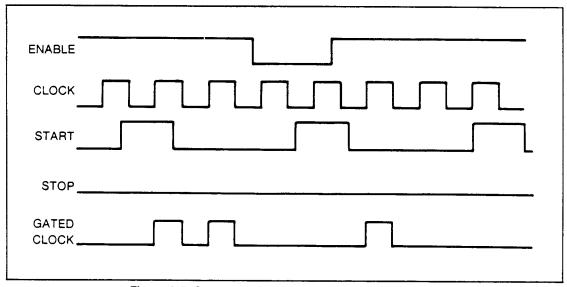

Figure 3-1 shows a typical arrangement of control signals required to produce a gated CLOCK signal and compute a signature from the data appearing at the Troubleshooter probe tip. To further illustrate the function of the control signals, Figures 3-2 through 3-7 show different control signal situations and their effect on the gated CLOCK signal. The gated CLOCK signal, which occurs when the gate section is in the "on" condition and CLOCK pulses are present, clocks the data appearing at the test probe into the signature generator and event counter. It is during the time of the gated CLOCK signal that signature generation takes place. Without the gated CLOCK signal, there is no signature computation within the module.

#### NOTE

In Figures 3-2 through 3-7, all active edges are positive-going, although you may select edges to be either positive or negative.

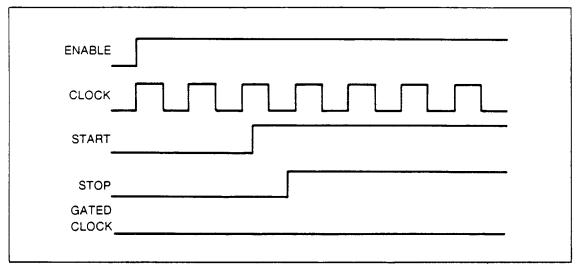

Figure 3-2 shows the resulting gated CLOCK when the START and STOP edges occur before the CLOCK signal. Even when the ENABLE line is asserted (held high in this case), there is no gated CLOCK signal. This is due to the lack of a CLOCK pulse (from the UUT or pod SYNC) after the START signal edge and before the STOP signal edge.

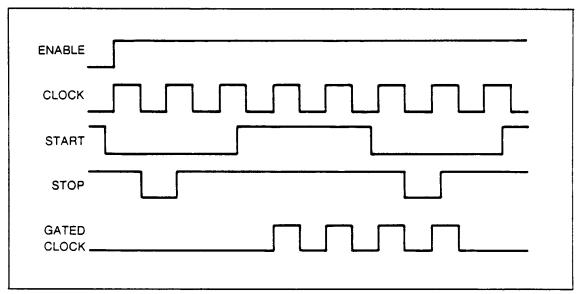

Figure 3-3 illustrates the edge sensitivity of the START and STOP signals. Note that the gated CLOCK signal does not occur until after the selected edge of the START signal, and it does not cease until after the selected edge of the STOP signal.

Figure 3-4 illustrates the effect of the ENABLE line on the gated CLOCK signal. In this example, the ENABLE line is asserted for only a portion of the time between the START and STOP signals. As a result, gated CLOCK signals are produced only during the time of the ENABLE signal.

Figure 3-5 shows more graphically that a full CLOCK width passes the gate after the occurrence of the STOP signal.

# 3-10. SELECTING THE CONTROL SIGNAL SOURCES

Since each troubleshooting/test situation is unique, there are no set rules for selecting the source for each control signal. An understanding of these four signals, as presented in the previous paragraphs, is the best tool for determining the source of these signals for a particular UUT.

The control signals include the START, STOP, CLOCK, and ENABLE signals. Connection of these signals (when used) from the UUT to the Signature Module is provided by the Clock Module and individual clip leads. Typically, START, STOP, and CLOCK signals are required, while the ENABLE signal is optional.

The pod SYNC signal, generated each time the Interface Pod executes a read or write operation with the UUT, may be used for the CLOCK and/or START/STOP signals. These signals may also be taken from the UUT by connecting the

Figure 3-2. Stop Received Before Clock

Figure 3-3. Start and Stop Are Edge Sensitive

Figure 3-4. Gated Click occurs during Enable

Figure 3-5. Gate Passes Full Clock Width

appropriate clip lead of the Clock Module. The ENABLE signal may be taken from some point on the UUT, or it may be selected to be held in the enabled condition.

While the ENABLE signal is level-sensitive, the START, STOP, and CLOCK signals are all edge-sensitive. Level and edge selection for the control signals is specified during the initialization (setup) of the Troubleshooter for operation in the signature mode.

# 3-11. CLOCKING ON BOTH EDGES

In some applications it may be desirable to sample UUT data on both edges of the CLOCK signal signal applied to the Signature Module. When clocking on both edges is selected (during initialization), a narrow-width CLOCK pulse is provided to the gate section of the Signature Module for each edge (rising and falling) of the selected CLOCK signal. Refer to Figure 3-6.

Figure 3-6. Effects of Selecting Both Clock Edges

### 3-12. ESTABLISHING UUT TEST NODES

The main function of the Asynchronous Signature Module is to take signatures at selected nodes of a UUT and present them on the Troubleshooter display as a four-character hexadecimal value. In addition to displaying the signature, the Troubleshooter also displays the accumulated count of the transitions contained in the data used to calculate the signature (unless the free-run mode is selected for the event count function).

When implementing the signature method of troubleshooting, it is necessary to first take signatures at selected points within a known-good UUT. Troubleshooting by taking signatures on a defective (or suspected defective) UUT is of little value if no valid signatures are available for reference and comparison. The assignment of test points in a particular UUT requires a detailed knowledge of UUT operation. Avoid assigning test points that may yield invalid or unstable signatures and event counts.

# 3-13. USING THE STOP COUNTER MODE

During initialization of the signature function, the user is prompted to select the STOP count function. This feature, when selected by the user, causes termination of signature-taking after a specified number of gated CLOCK pulses (i.e., CLOCK pulses passed to the signature generator and event counter by the gate section).

During operation in the stop counter mode, each gated CLOCK signal decrements a counter provided within the Signature Module from its preset count. Any CLOCK pulses inhibited by an invalid ENABLE signal do not reach the stop counter. The stop counter is only decremented by gated CLOCK pulses; i.e., those that reach the signature generator and event counter circuits.

When the counter reaches the zero condition, it generates the STOP signal necessary to terminate the signature-taking operation. Figure 3-7 shows an example of stop counter use. In this example, the stop counter is set to a value of 3, and the ENABLE signal goes low (inhibit condition) for a duration that masks two valid (rising) CLOCK edges.

Figure 3-7. Stop-After-Count Mode Example (count = 3)

The stop counter generates its STOP output in parallel with any STOP signal provided over the STOP clip lead of the Clock Module. Consequently, the occurrence of any STOP signal over the Clock Module clip leads before the stop counter is fully decremented will terminate the gate time and signature operation. If you want the stop counter to provide the STOP signal, an external STOP signal must not be received before the counter reaches zero (before the specified number of gated CLOCK pulses have occurred).

### 3-14. USING DELAY COMPENSATION

Delay compensation allows for the insertion of delay between the input from the data probe and the signature generator, the event counter, and the waveform register of the Signature Module. Delay may be inserted into the data path in increments of approximately 3 nanoseconds, up to a total of 12 increments. Selection of delay allows for the detection of and compensation for marginal timing conditions in the UUT.

Delay compensation is used most often in high CLOCK-rate systems. In such systems, determine the amount of delay compensation (which allows stable and repeatable testing of a known-good UUT) then specify that amount of delay for testing similar UUTs. In systems that use low-to-moderate CLOCK speeds (up to 10MHz), a delay setting in the middle of the range (4 units) may usually be selected for satisfactory testing.

#### 3-15. STIMULATING THE UUT

### 3-16. Self-Test

In order for repeatable testing of a UUT to take place using the signature, event count, or waveform display features provided by the Asynchronous Signature Module Option, the UUT must be stimulated into operation in some stable and repeatable manner. Some microprocessor-based systems include a self-test feature that, as long as the microprocessor section is operational, stimulates various portions of the UUT in the required manner. However, self-test routines usually provide stimulus to limited sections of the UUT. Also, any problem in the microprocessor section, such as a stuck line on the address or data bus, usually prevents any self-test operation.

# 3-17. Using Troubleshooter Front Panel Functions

The 9000A Series Microsystem Troubleshooter is an ideal source of UUT stimulus. Since the programs provided with the option allow the Troubleshooter to be first set up for signature taking and event counting, and then return to normal Troubleshooter operation, any Troubleshooter function can be used to stimulate the UUT.

In order to use the Troubleshooter to stimulate the UUT, operation in the signature mode must be stopped (STOP key). The Troubleshooter can then be used to perform any desired test operation or execute a test program to stimulate the UUT. When the test operation (stimulus) is complete, the operator executes program 1 (if using the supplied programs) to return to the signature mode.

Once back in the signature mode, the user can observe the test results of the stimulus operation by means of the CONT or READ keys. Refer to Taking Signatures and Event Counts in Section 2.

# 3-18. Using Programmed Routines

Another method of using the Troubleshooter to stimulate the UUT is to write a test program that exercises the desired portions of the UUT. Such a program can be executed in place of pressing front panel keys, thereby simplifying the stimulus operation. The Troubleshooter can be used to run a repeated stimulus program while the Asynchronous Signature Module is used to take the signatures.

#### 3-19. ESTABLISHING SIGNATURES AND EVENT COUNTS

As part of the implementation of signature testing, it is necessary to provide test/repair personnel with valid signatures or event counts for the specific UUT. The procedure for establishing signatures and event counts within the UUT consists of using the 9010A or 9005A Troubleshooter in the signature mode as described in Section 2 of this manual. In this mode, use the Troubleshooter to take signatures and event counts at the established test nodes while stimulating the UUT as specified for testing. List each of the signatures and event counts required for testing as part of the documentation for the UUT.

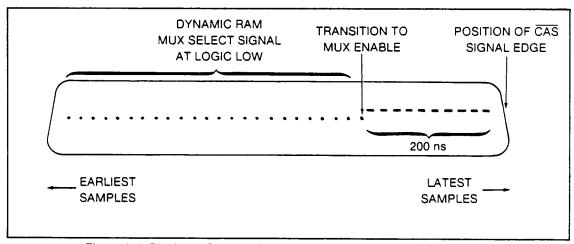

### 3-20. USING THE WAVEFORM DISPLAY

The waveform display feature may be used to measure the time relationship between two signal edges within the UUT. This feature is useful when viewing signals of less than 10 MHz due to asynchronous sampling and data probe bandwidth limitations. A typical use of this feature is checking the time relationships between such signals as the RAS (row address strobe) and WRITE ENABLE lines of a dynamic RAM. This feature can also be used to check the time relationship of the CAS and address multiplexer ENABLE lines or any other portion of a circuit where the timing of two signals is critical to UUT operation.

The waveform display feature allows the Troubleshooter to display the last 640 nanoseconds of signals applied to the data probe before a STOP was received (or before the stop counter decremented to zero). The data signal appears as logic high, logic low, or tri-state, as shown in Figure 3-8. The latest samples of the signal appear at the right side of the display. The signal edge used to STOP the gate section and halt the gathering of data does not appear on the display, but if visible, it would appear just to the right of the rightmost display character.

Figure 3-8. Waveform Display Details

Figure 3-9 shows a waveform display of the time relationship between the rising edge of the CAS signal and the rising edge of the multiplexer ENABLE signal found in a dynamic RAM circuit. To achieve this display, the CAS signal is connected to the STOP lead of the Clock Module and selected as the STOP signal during initialization. Since the CAS signal is used to terminate the gate time, it cannot appear on the display, but is assumed to occupy the next 20-nanosecond position to the right of the display.

Figure 3-9. Display of Dynamic RAM MUX and CAS Signal Timing

In Figure 3-9, the rising edge of the multiplexer ENABLE signal (picked up by the data probe) is shown to occur ten display characters from the right side of the display. Each character position represents 20 nanoseconds, so the interval between the CAS signal edge and the multiplexer ENABLE signal is approximately 200 nanoseconds.

The waveform display feature can be used to verify the time relationship of any two signal edges that occur within the 640-nanosecond range of the Troubleshooter display. Connect the data probe to the leading signal and the STOP lead of the Clock Module to the lagging signal. Perform a read-probe operation with the UUT under stimulus, then read the waveform display, counting each display character as 20 nanoseconds.

### 3-21. DOCUMENTING THE UUT FOR TESTING AND TROUBLESHOOTING

As signature-mode troubleshooting is implemented for a particular UUT, the appropriate documentation should be created and provided to personnel having the responsibility of testing and/or repairing the UUT. The documentation required may vary somewhat, depending upon the complexity of the equipment, the qualifications of the personnel, and the level of testing and troubleshooting to be undertaken. Typically, the documentation created during implementation of signature-mode testing includes the following:

- O Annotated schematic diagram(s) or node lists of the UUT that show the required signatures at each test node.

- O Complete description of the test setup: initialization parameters and connection of the control signal leads of the Clock Module.

- O Description of the action required to stimulate the UUT in the desired manner.

- O Description of any event count testing and the expected results.

- O Step-by-step test procedures.

- O Appropriate documentation for any custom testing programs, plus back-up copies of any cassettes.

# 3-22. PROGRAMS SUPPLIED ON THE CASSETTE

### 3-23. General

Several programs are supplied on the cassette included with the Asynchronous Signature Probe Option. These programs, listed and described in Table 3-1, fall into the following categories:

- O User interface programs

- O Library programs

- O Troubleshooting Self-Stimulus

- O Tape merge utility

The user interface programs (program numbers 0 through 11 on tape side A) are used by the option when it is operating in the interactive mode. These programs provide the necessary user interface by reading the 9000A mainframe keyboard and displaying the appropriate messages to the operator. The user interface programs rely heavily on the library programs, and on each other, and cannot be used outside the interactive mode of the Asynchronous Signature Probe Option.

The library programs (program numbers 12 through 20 on tape side A) operate independently from each other, and from the user interface programs, allowing them to be copied from the tape (using the merge tape utility). The library programs, some written in binary format, can be selectively copied from the cassette as required to create custom routines as required for any custom fault-isolation procedure.

Copying and renumbering programs provided in the tape is made possible by means of the Merge Tape Utility Program, also supplied on the cassette, but on side B. Also contained on side B are a pair of programs used to stimulate the module during troubleshooting operations on the module itelf.

In the paragraphs that follow, each of these programs is described in sufficient detail to enable the experienced 9010A programmer to write additional programs that provide interaction with the operator.

Table 3-1. Programs Contained on the Cassette

| PROGRAM NAME             |     | NUMBER/ DESCRIPTION<br>SIDE                                                                                                                                                                           |

|--------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Initialize               | 0/A | A program that loads the initialization register (register 8) with the default hardware (module) setup parameters then executes the Interactive Operation Program.                                    |

| Interactive<br>Operation | 1/A | A program that executes other programs in response to front panel keys, to allow interactive user operation of the Troubleshooter/Signature Module.                                                   |

| Service Gate Keys        | 2/A | A program that executes other programs in response to the front panel READ, READ PROBE, and CONT keys.                                                                                                |

| Service SETUP Key        | 3/A | A program that executes other programs to initialize the module when the Setup Hardware Program is executed. Refer to Section 2 for information pertaining to initialization of the Signature Module. |

Table 3-1. Programs Contained on the Cassette (cont.)

| 14016 3-         | . rrograms co             |                                                                                                                                                                         |

|------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROGRAM NAME     | PROGRAM NUMB<br>TAPE SIDE | ER/ DESCRIPTION                                                                                                                                                         |

| Display Gate     | 4/A                       | A program that monitors the occurrence of<br>the start, stop, and clock signal; and<br>indicates the condition of these signals<br>on the Troubleshooter display.       |

| Start Setup      | 5/A                       | A program called upon by the Service<br>SETUP Key Program to allow operator<br>selection of the START signal.                                                           |

| Stop Setup       | 6/A                       | A program called upon by the Service<br>SETUP Key Program to allow operator<br>selection of the STOP signal.                                                            |

| Clock Setup      | 7/A                       | A program called upon by the Service<br>SETUP Key Program to allow operator<br>selection of the CLOCK signal.                                                           |

| Enable Setup     | 8/A                       | A program called upon by the Service<br>SETUP Key Program to allow operator<br>selection of the ENABLE signal.                                                          |

| Stop Count Setup | 9/A                       | A program called upon by the Service<br>SETUP Key Program to allow operator<br>selection of gated CLOCK pulses for stop.                                                |

| Delay Setup      | 10/A                      | A program called upon by the Service SETUP Key Program to allow operator selection of the delay compensation.                                                           |

| Event Setup      | 11/A                      | A program called upon by the Service<br>SETUP Key Program to allow operator<br>selection of the event count parameters.                                                 |

| Setup Hardware   | 12/A                      | A binary program that initializes the module in accordance with the contents of register 8 (the initialization register) by sending a series of op codes to the module. |

| Arm Gate         | 13/A                      | A binary program that resets all registers within the module and then arms it to receive control signals (START, STOP, and CLOCK).                                      |

Table 3-1. Programs Contained on the Cassette (cont.)

| PROGRAM NAME       | PROGRAM N<br>TAPE S | NUMBER/ DESCRIPTION<br>SIDE                                                                                                         |

|--------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------|

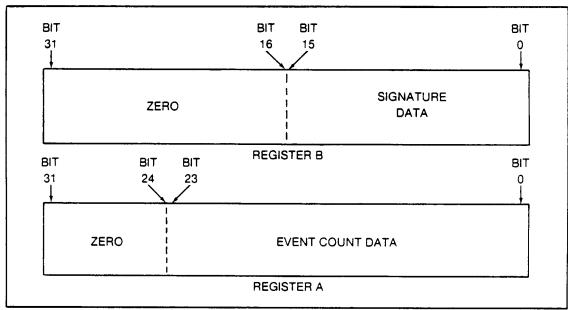

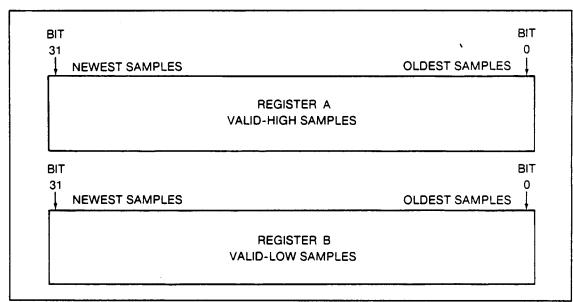

| Get Signature      | 14/A                | A binary program that retrieves the signature data from the module and places it in the B register.                                 |

| Get Events         | 15/A                | A binary program that retrieves the events data from the module and places it in the A register.                                    |

| Get Waveform       | 16/A                | A binary program that retrieves the waveform data from the module and places it in the A and B registers.                           |

| Read Data and      |                     |                                                                                                                                     |

| Status             | 17/A                | A binary program that directs the Signature Module to read one nibble of data and one nibble of status.                             |

| Send Op Code       | 18/A                | A binary program that sends one byte over<br>the pod bus to the Signature Module.                                                   |

| Display Waveform   | 19/A                | A program that presents the contents of<br>the two waveform data registers on the<br>troubleshooter display.                        |

| Append Signature   | 20/A                | A utility program that appends the value in user register B to the display in signature format.                                     |

| Merge Tape Program | 0/B                 | A utility program that allows taking programs from the supplied cassette for use as part of a custom troubleshooting program.       |

| Stimulus Program A | 1/B                 | A program used to stimulate the control and gate sections of the Signature Module during troubleshooting procedures.                |

| Stimulus Program B | 2/B                 | A program used to stimulate the signature, events, and waveform sections of the Signature Module during troubleshooting procedures. |

# 3-24. 9000A Register Usage

Several of the programs supplied on the cassette use specific registers within the 9000A mainframe. It is important to keep this in mind when you are using the registers in related 9000A programs. Table 3-2 lists the 9000A mainframe registers and their usage by the supplied programs.

Table 3-2. 9000A Register Usage

| REGISTER NO. | USAGE                                                       |

|--------------|-------------------------------------------------------------|

| 8            | Contains the setup parameters                               |

| 9            | Used for internal program control (unavailable to the user) |

| Α            | Waveform capture mode: high data samples                    |

| Α            | Contains the op code sent by send op code program (no. 18)  |

| В            | Waveform capture mode: low data samples                     |

| В            | Contains data/status from get data/status program (no. 17)  |

### NOTE

Refer to the Operator Manual that accompanied your Troubleshooter for an explanation of and the standard uses for the 16 data registers within the Troubleshooter.

#### 3-25. LIBRARY PROGRAMS

### 3-26. Setup Hardware Program

PROGRAM NUMBER: 12

NAME: Setup hardware

ACTION: Configures the asynchronous signature module with setup values.

USER REGISTERS REFERENCED: Register 8.

USER REGISTERS AFFECTED: None.

DESCRIPTION: The Setup Hardware Program is a binary program used to initialize the Signature Module to the setup values established for the control signals, delay compensation, etc. The setup values are taken from register 8, the initialization register, which is preloaded as defined in Table 3-3 prior to execution of the program.

The Setup Hardware Program performs the following basic operations:

- 1. Disarms the module

- 2. Resets the module (gate function)

- 3. Checks each field of the initialization register and sends the corresponding op code to the module.

Table 3-3. Initialization Register, Field Definitions

| FIELD<br>DESIG. | POSITION<br>(REG. BITS) | FIELD FUNCTION (bit                                                                          | ENCODING                                                                                                                              |

|-----------------|-------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| a               | 0, 1, 2,                | Designates the field displayed when setup is interrupted (used by Service SETUP Key Program) | 000 = field b<br>001 = field c<br>010 = field d<br>011 = field e<br>100 = field f<br>101 = field g<br>110 = field h<br>111 (not used) |

| Ъ               | 3, 4                    | Designates the START signal selection                                                        | <pre>bit 3: 0 = rising edge           1 = falling edge bit 4: 0 = external START lead           1 = pod SYNC</pre>                    |

Table 3-3. Initialization Register, Field Definitions (cont.)

|                 |                      | Register, Freid                                                                                     |                                                                                                                                                                                                                                                                                                                                          |

|-----------------|----------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FIELD<br>DESIG. | POSITION (REG. BITS) | FIELD FUNCTION (bits                                                                                | ENCODING 2,1,0)                                                                                                                                                                                                                                                                                                                          |

| С               | 5, 6                 | Designates the STOP signal selection                                                                | <pre>bit 5: 0 = rising edge</pre>                                                                                                                                                                                                                                                                                                        |

| d               | 7, 8, 9              | Designates the CLOCK signal selection                                                               | <pre>bit 7: 0 = single edge</pre>                                                                                                                                                                                                                                                                                                        |

| е               | 10, 11               | Designates the ENABLE signal selection                                                              | bit 10: 0 = external enable<br>1 = held enabled<br>bit 11: 0 = ENABLE on high<br>1 = ENABLE on low                                                                                                                                                                                                                                       |

| f               | 12 - 23              | Specifies the count for the stop-on-count function                                                  | zero = disable function<br>1 to 4095(decimal) sets<br>the stop-on count                                                                                                                                                                                                                                                                  |

| g               | 24 - 27              | Specifies the amount of delay compensation (1 unit = 3 ns) Left to right is bit 27, 26, 25, and 24. | 0000 = no delay 0001 = 1 unit of delay 0010 = 2 units of delay 0011 (not used) 0100 = 3 units of delay 0101 = 4 units of delay 0110 = 5 units of delay 0111 (not used) 1000 = 6 units of delay 1001 = 7 units of delay 1010 = 8 units of delay 1011 (not used) 1100 = 9 units of delay 1110 = 10 units of delay 1111 = 12 units of delay |

| h               | 28, 29               | Designates the event count selection                                                                | <pre>bit 28: 0 = gated mode           1 = free-run mode bit 29: 0 = count probe data           1 = count clocks</pre>                                                                                                                                                                                                                    |

| i               | 30, 31               | Not used                                                                                            |                                                                                                                                                                                                                                                                                                                                          |

If a timeout occurs during communications with the signature module, the user is given an error message and asked to press the CONT key before proceeding. All other keys will produce a beep (including STOP).

## 3-27. Arm Gate Program

PROGRAM: 13

NAME: Arm Gate