The sequence for reading the RULESW, TWO4SW, and 4-position DIP option switch and kick buttons are as follows:

ABUSI -

ABUSØ-15

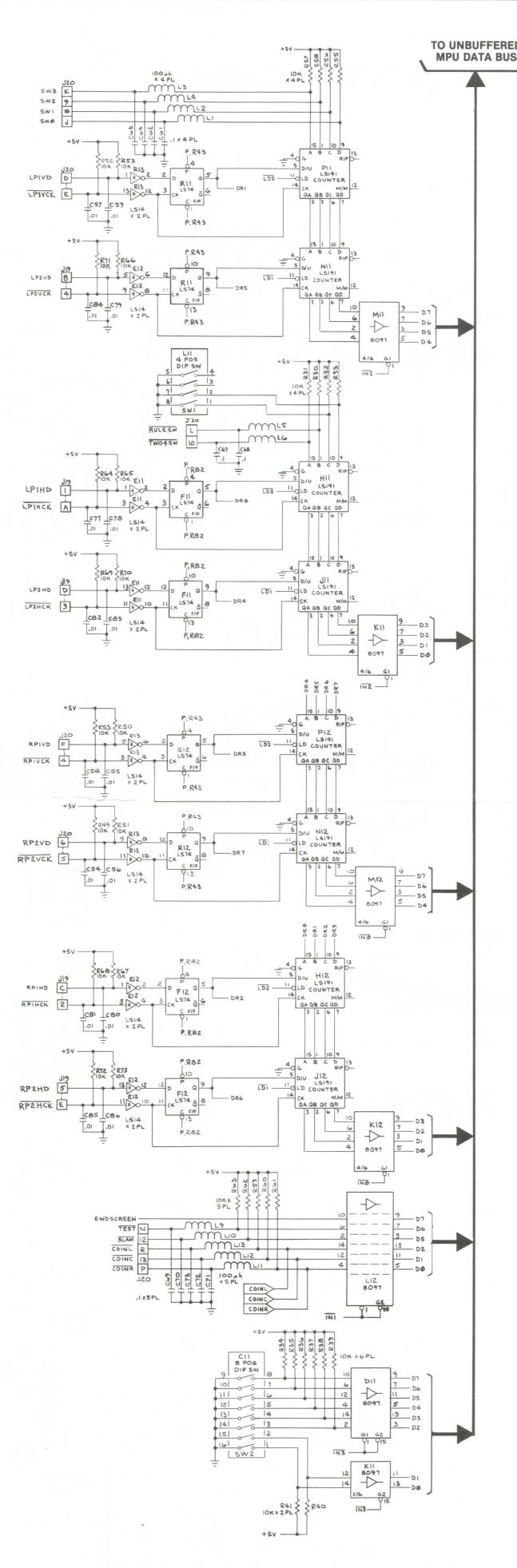

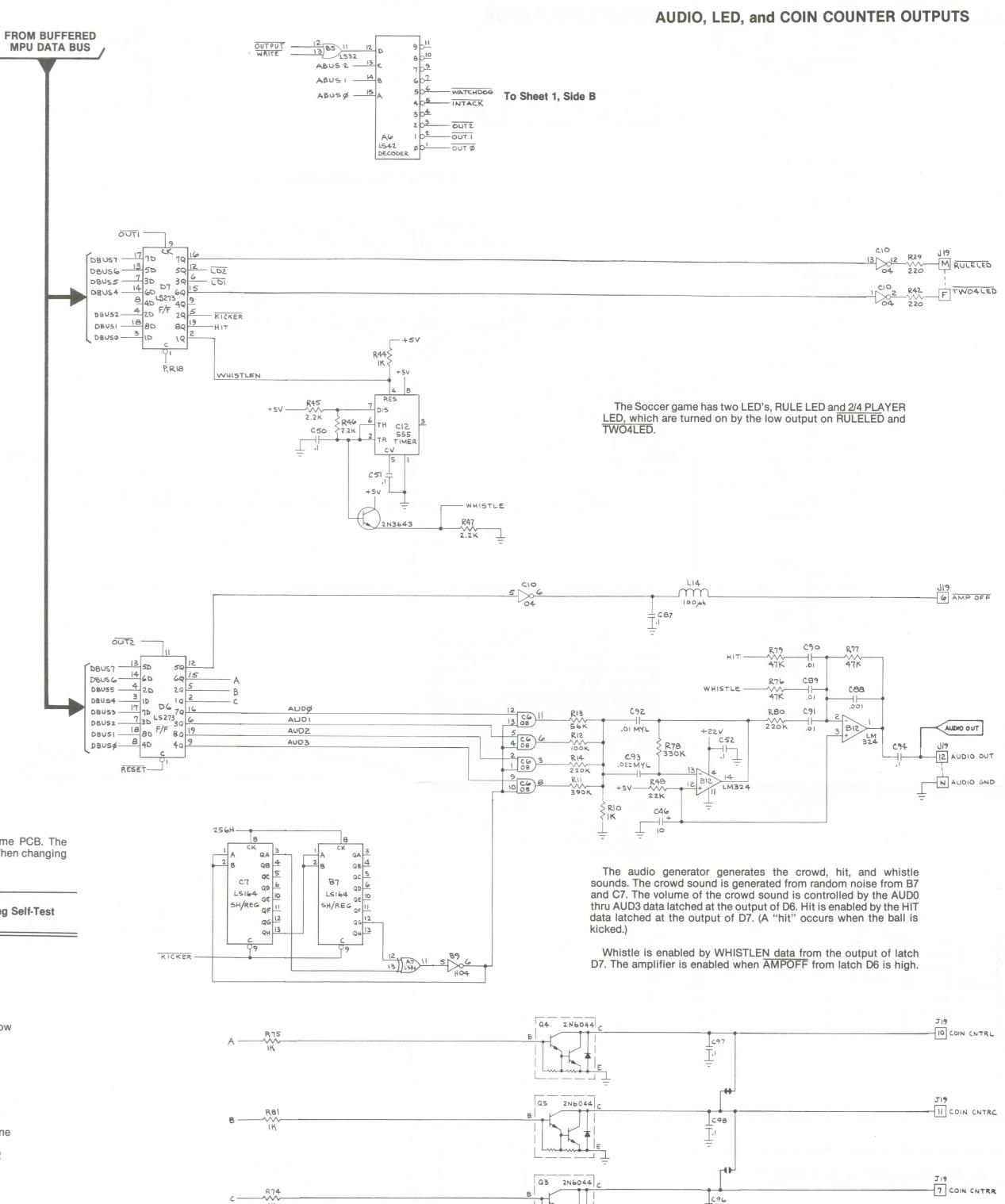

- LD1 and LD2 are latched low at the output of D6 on the rising edge of OUT1. 2. IN2 from the address decoder enables input ports K11 and

- The microprocessor reads the switches on data lines D0 to D7 through counters J11, H11, N11 and P11.

The Trak Balls are read by the microprocessor through input ports K11, M11, K12 and M12. Ports K11 and M11 are enabled by IN2 from the address decoder, and K12 and M12 are enabled by IN0. When LD1 and LD2 are both high, the microprocessor reads the rate of turn for the Trak Balls connected to J12 and N12, or connected to J11 and N11. When LD1 is low and LD2 is Balls connected to the input of counters H12 and P12, or H11 and P11. When LD1 and LD2 are both low, the microprocessor reads the direction of the "PLAYER 2" Trak Balls on data lines D4-D7, and the "PLAYER 1" Trak Balls on data lines D0-D3.

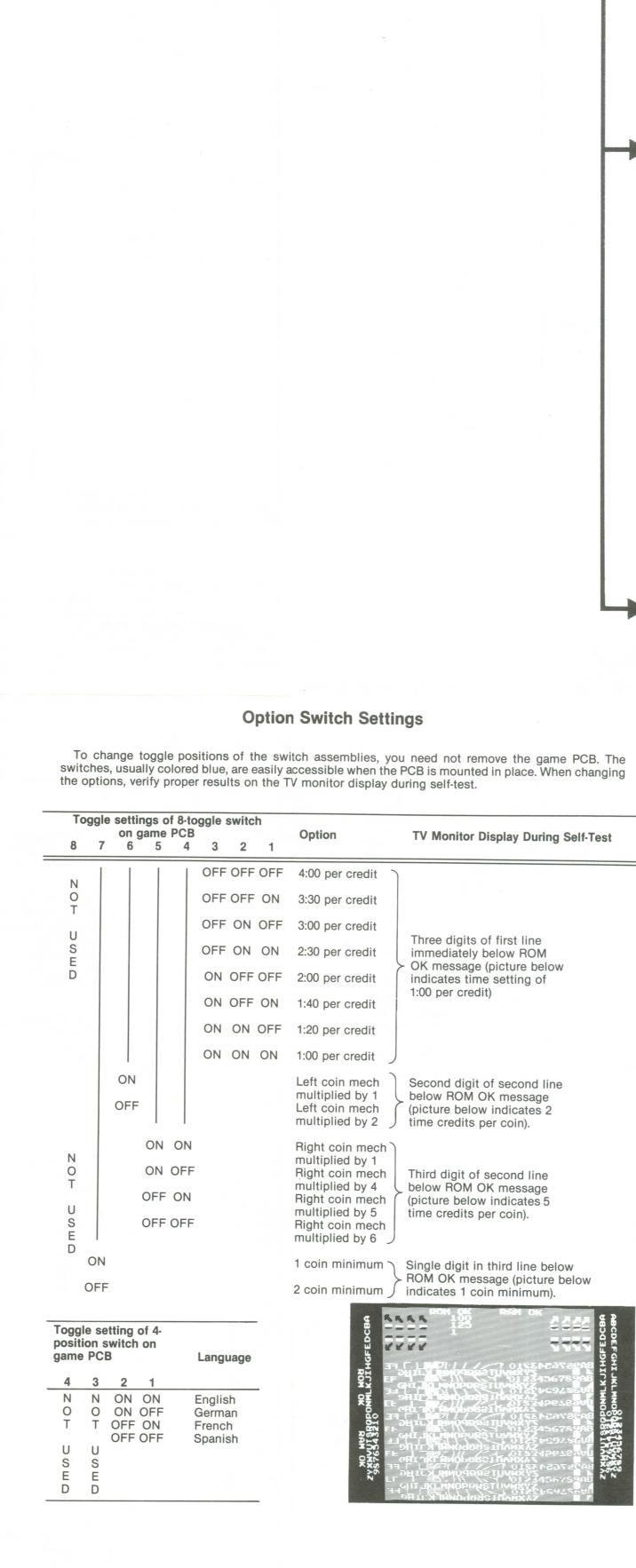

The option switch toggles are read on data lines D0 thru D7 when  $\overline{\text{IN3}}$  from address decoder enables input ports D11 and K11.

Coin slam and self-test switch inputs are connected to +5 VDC through pullup resistors. When a switch is closed, that input is pulled to ground. The switch is read by the microprocessor when switch input port L12 is enabled by IN1 from the address decoder.

Coin counters are activated by low outputs

denotes a test point

on COIN CNTRL, COIN CNTRC and COIN

CNTRR which are controlled by the latched

outputs A, B and C, from D6.

034905-XX A