Service Information (PCB Logic)

## **TABLE OF CONTENTS**

| Para.        | Title                                | Page        |

|--------------|--------------------------------------|-------------|

| 1-1          | Introduction , , . ,                 | 1.1         |

| 1-7          | Test Equipment                       | 1-1         |

| 1-10         | Required Equipment                   | 1-1         |

| 1-11         | Optional Equipment                   | 1-2         |

| 1-12         | Troubleshooting Suggestions          | 1.2         |

| 1-19         | PCB Adjustments                      | 1.2         |

| 1-21         | Logic Symbology                      | 1.3         |

|              | <u> </u>                             | . •         |

|              | ##                                   |             |

| 2-1          | The Power Supply , , ,               | 2-1         |

| 2-4          | +5 Volts                             | 2-2         |

| 2-5          | +18 Volts                            | 2-2         |

| 2-6          | -12 Volts                            | 2.2         |

| 2.7          | -5 Volts                             | 2-2         |

| 2-8          | The Pull-up Resistors                | 2-2         |

| 2-9          | Buffered Start                       | 2- <b>2</b> |

| 2-11         | The Oscillator , , , , .             | 2-2         |

| 2-13         | The Electronic Latch                 | 2-2         |

| 2.19         | The Credit and Start Circuit         | 2.3         |

| 2-24         | TV Monitor Operation , , ,           | 2-4         |

| 2 30         | Synchronization and Blanking         | 2.5         |

| 2-39         | Screech Logic                        | 2-7         |

| 2-41         | Screech and Crash Sound Generation   | 2.7         |

| 2-44         | Engine RPM Sound Generation          | 2-8         |

| 2-48         | The Audio Amplifier                  | 2.8         |

| 2-50         | Speed Control                        | 2.8         |

| 2-52         | 8103/72046 Input/Output Conditions   | 2-11        |

| 2-55         | 8099/72029 Input/Output Conditions   | 2-11        |

| 2-58         | 8098/72030 Input/Output Conditions   | 2-11        |

| 2-59         | VLd1                                 | 2-11        |

| 2-61         | 1 STOP                               | 2-12        |

| 2-63         | Ld1B                                 | 2-12        |

| 2-65         | RESET 1, ,                           | 2-12        |

| 2.67         | Steering Control                     | 2-12        |

| <b>2</b> -73 | The Steering Encoder                 | 2-13        |

| 2-77         | Crash and Playtime                   | 2-14        |

| 2-81         | The Memory Circuit                   | 2-14        |

| 2-86         | Troubleshooting the Memory Circuit . | 2-15        |

| 2-91         | The Window Cancept                   | 2-17        |

| 2-96         | Introduction to Motion               | 2-18        |

| 2-100        | Horizontal Count                     | 2-19        |

| 2-102        | Vertical Car Motion , , , ,          | 2-19        |

| 2-105        | Horizontal Car Motion                | 2-20        |

| 2-108        | Car Display,                         | 2-20        |

| 2-111        | Race Track Display                   | 2.21        |

| 2-116        | Time and Score Storage               | 2-21        |

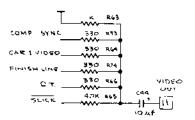

| 2-126        | Video Summer                         | 2-23        |

# LIST OF ILLUSTRATIONS

| Figure | Title                                       | Page                |

|--------|---------------------------------------------|---------------------|

| 2-1    | The Power Supply and Buffered Start -       | 2-1                 |

| 2-2    | The Oscillator                              | 2-2                 |

| 2-3    | The Electronic Latch                        | 2-3                 |

| 2-4    | The Credit and Start Circuit                | 2-4                 |

| 2-5    | Interfaced Roster Scan                      | 2-5                 |

| 2-6    | Sync Pulse Trains                           | 2.5                 |

| 2-7    | Synchronization and Blanking                | 2-6                 |

| 2-8    | Screech Logic                               | 2-7                 |

| 2-9    | Screech and Crash Sound Generator           | 2-8                 |

| 2-10   | Electronic Attenuator                       | 2.9                 |

| 2-11   | Engine RPM Sound Generator                  | 2-9                 |

| 2-12   | The Audio Amplifier                         | 2-9                 |

| 2-13   | Speed Control                               | 2-10                |

| 2-14   | VLd1                                        | _ 2-11              |

| 2-15   | 1 STOP                                      | 2-12                |

| 2-16   | Ld1B                                        | <u>.2-</u> 12       |

| 2-17   | RESET 1 · · · · · · · · · · · · · · · · · · | 2 12                |

| 2-18   | Steering Control                            | 2-13                |

| 2-19   | Steering Encoder                            | 2-14                |

| 2-20   | Crash and Playtime                          | 2-15                |

| 2-21   | The Memory Circuit                          | 2-16                |

| 2-22   | Basic Two-input Two-to-one Multiplexe       | r 2-16 <sup>*</sup> |

| 2-23   | CRT Windows                                 | 2-18                |

| 2-24   | CRT Image Motion                            | ຶ້ 2-18             |

| 2-25   | Horizontal Count                            | 2-19                |

| 2-26   | Vertical Car Motion                         | 2-19                |

| 2.27   | Horizontal Car Motion                       | 2-20                |

| 2-28   | Car Display                                 | 2-20                |

| 2-29   | Race Track Display                          | 2-21                |

| 2-30   | Time and Score Storage                      | 2-22                |

| 2-31   | Video Summer                                | 2-23                |

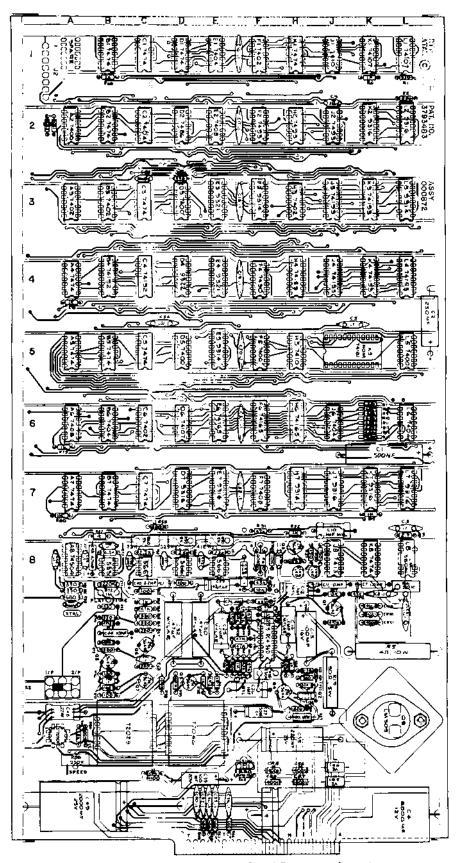

| 2-32   | Computer Board Component Layout             | 2-26                |

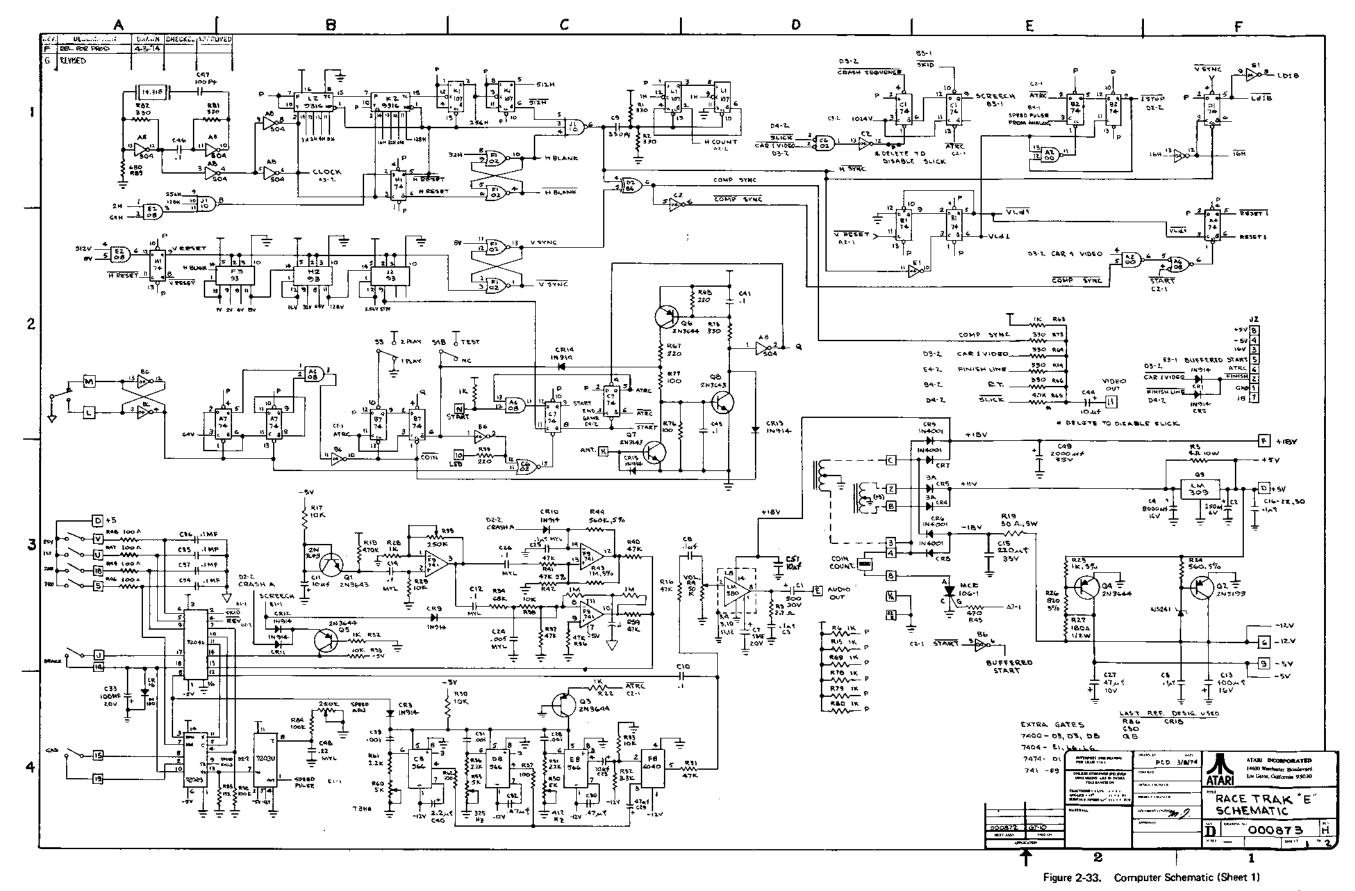

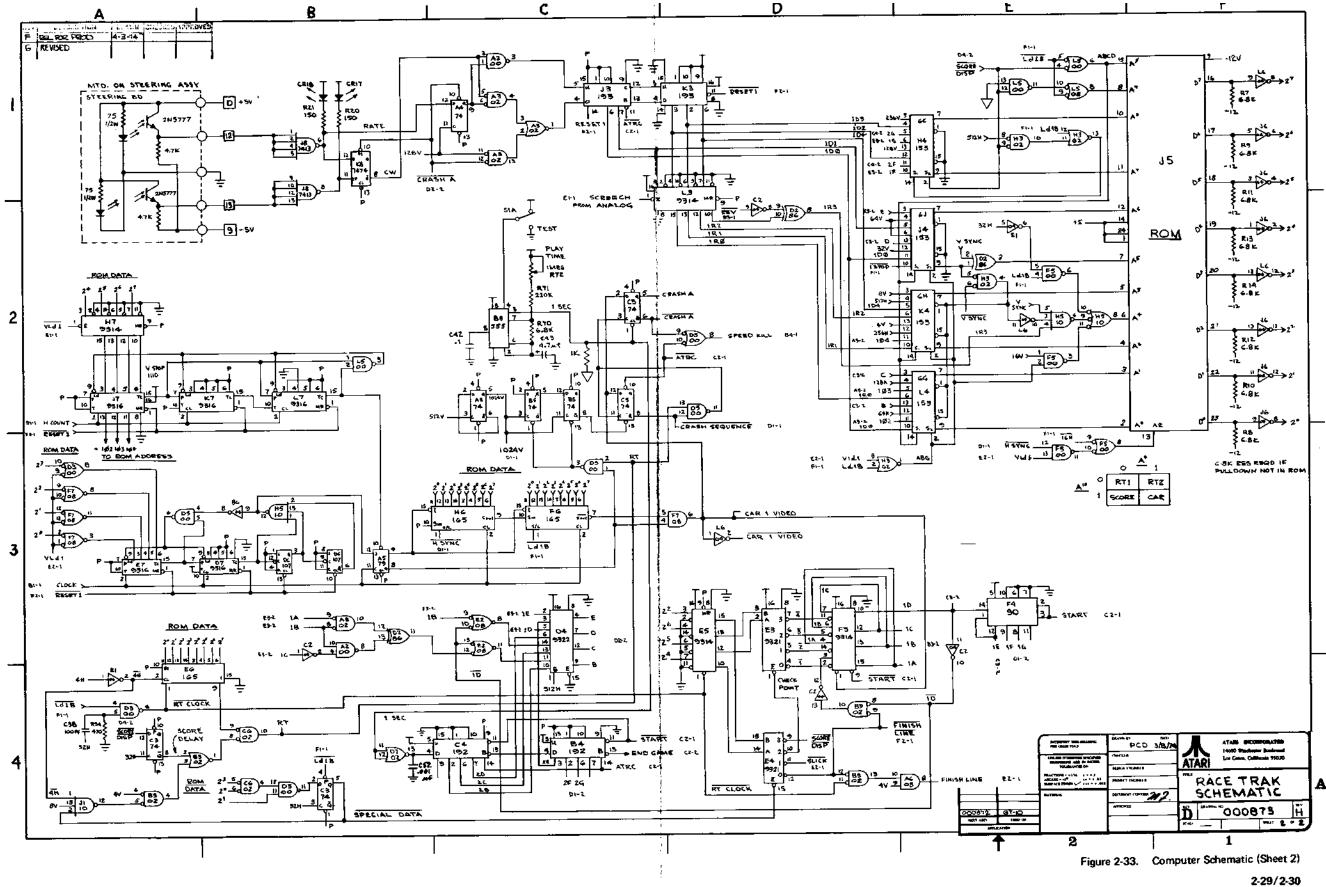

| 2.33   | Computer Schematic (2 sheets)               | 2-27/2-30           |

|        | LIST OF TABLES                              |                     |

| 1-1    | Logic Symbology                             | 1-4                 |

| 2-1    | ROM Address Table                           | 2-17                |

| 2-2    | Check Point Truth Table                     | 2-22                |

| 2 2    | Crop Trait 10 BCB Bosto List                | 2.24/2.25           |

## 1. GENERAL MAINTENANCE INFORMATION

#### 1-1. INTRODUCTION

- 1-2. Gran Trak 10 is a new type of video game, and the operation of the new circuitry must be learned before your troubleshooting attempts will be successful. However, after the basic differences are understood, it should prove no more difficult than any other Atari printed circuit board (PCB) computer. The main differences between GT-10 and previous Atari games are the steering circuitry, the hybrid chips, the ROM (read only memory) and the power supply.

- 1-3. The steering circuitry is a novel bit of engineering which employs phototransistors and infrared light emitting diodes to generate pulses indicating the direction of steering wheel rotation. Fortunately, it is quite a simple circuit and easy to troubleshoot.

- 1-4. The hybrids are three custom chips which have been specially manufactured for this game. Troubleshooting these chips involves only verifying the correct input/output conditions and replacing the chip if the output conditions are not correct.

- 1-5. The ROM is another chip which has been specially programmed for GT-10 and it is used to generate the information for the display of the car, the score and game timer and the race track. Troubleshooting the ROM is probably one of the easiest tasks because it involves only unplugging the suspected chip and replacing it with a known-to-begood ROM.

- 1-6. The power supply is more complicated because additional voltages are needed to operate the ROM, the hybrids and the on-board audio amplifier. Even though there are a few more voltages to check, the basic power supply troubleshooting methods remain unchanged.

### 1-7. TEST EQUIPMENT

- 1-8. Because of this new circuitry, more test equipment is required to check the PCB. An oscilloscope is an absolute necessity and a logic comparator would be a wise investment.

- 1-9. Some of the following instruments are absolutely <u>essential</u> to fully test the GT-10 PCB; others are desirable because they make the test procedures easier, but are not essential. Many of these items are available from the Atari Customer Service Department, and these items are indicated by an asterisk (\*). A few others are available only

from electronics supply houses or rental agencies; however, if you have difficulty in obtaining any needed instrument, contact Atari Customer Service for assistance.

- 1-10. Required Equipment: Atari recommends the following as a minimum set of test equipment:

- a. Logic Probe\*: The logic probe is an instrument designed for checking the outputs of integrated circuits. Atari recommends the Kurz-Kasch Logic Probe, model No. LP-520. The logic probe will indicate if a signal is a logic high, low or changing from one state to the other. Consult the operating instructions included with the unit for further details on its operation.

- b. Video Probe\*: The video probe is a simple, but useful testing device. It consists of two IC test clips (or one clip and a test prod), a length of wire and a 4.7K, 1/4W carbon resistor. Video probes may be obtained free of charge from the Atari Customer Service Department, or, if necessary, they can be assembled from standard parts available at any electronics supply house. To use the video probe, attach one clip to the negative side of the video coupling capacitor (C44) and clip or touch the other end to the desired signal test points as indicated in the following pages. The VP will display the signal directly on the CRT.

- c. The Oscilloscope: The oscilloscope is used for viewing various waveforms. The application requires at least a 50 MHz scope and a dual trace unit to facilitate comparison between waveforms is desirable. Atari's specific recommendation is the Tektronix model No. 465, 100 MHz dual trace oscilloscope.

- d. Atari Universal Test Fixture: The Atari Universal Test Fixture can be used to test the computer boards for Pong, Pong Doubles, Super Pong, Rebound, Space Race, Gotcha, and Quadrapong. This test fixture is equipped with a 12 inch TV monitor, two 5 volt BNC connectors for use where a regulated 5 volt source is required, and all the controls necessary to operate the computer boards. Connector cables must be ordered separately for each different type of PCB to be tested. The test fixture and cables are only available through the Atari Customer Service Department.

103-1

- 1-11. Optional Equipment: The following pieces of test equipment are not essential but will make your trouble-shooting easier.

- a. The Logic Comparator\*: This compact trouble-shooting instrument will prove invaluable in verifying correct IC operation. The unit simply clips onto in-circuit ICs and instantly displays any logic state difference between the in-circuit test IC and the reference IC in the comparator. Logic differences are identified to the specific pin by a lighted LED. If this instrument is purchased from the Atari Customer Service Department, it will be shipped with 20 pre-programmed reference boards. If the instrument is purchased elsewhere, you will have to program the boards yourself. Atari recommends either the Hewlett Packard 10529A comparator or the Fluke comparator.

- b. The Logic Pulser\*: The logic pulser is used to stimulate in-circuit ICs so they are driven to their opposite states and we recommend the Hewlett Packard 10526T pulser.

### 1-12. TROUBLESHOOTING SUGGESTIONS

- 1-13. The first step in the troubleshooting process is to correctly identify the observable symptoms of the malfunction and then to narrow down the possibly malfunctioning areas as much as you can. This should reduce the situation to one or two functional blocks which might be at fault. Then start examining these functional blocks with your test instruments and compare the results with the operational analysis and test point information under the heading of that functional block. Keep in mind, however, that the first observable symptoms of a malfunction are not necessarily due to the functional block which produced those symptoms. A failure in one part of the PCB may affect much, if not all, of the PCB.

- 1-14. Some malfunctions may produce symptoms which are not clearly attributable to one component. Sync problems can be especially nasty in this regard because you can spend quite some time verifying the presence of correct sync signals on the board only to discover it is the monitor which is distorting sync.

- 1-15. For these problems, use substitution as a trouble-shooting technique. For instance, to clearly identify which component is at fault in a sync problem, try substituting a known-to-be-good TV monitor. If you have built a test fixture, plug the suspected board into the fixture and if the sync problem disappears, the other TV must have been the

- cause. Conversely, had the problem not disappeared, the substitution test would have revealed a malfunctioning board and you would begin the troubleshooting process at the sync section.

- 1-16. The same technique can be used to test the Read Only Memory (ROM) which is inserted in a plug-in type receptacle to facilitate the substitution test. If you have a problem with the car image, the race track display or the score or timer displays, try inserting another and known-to-be-good ROM and if this clears up the malfunction, leave it there. However, we must note that the ROM failure rate has been extremely low so it is more likely that a display problem is located in either the ROM address circuitry or the display circuits.

- 1.17. There are a few other problems which need mentioning because, while they may at first appear to be board related, closer examination will reveal they are location related. If the ac line voltage fluctuates enough, the electronic latch will turn off game credit. One cause of this may be a large load connected to the same line as the machine. For example, a large air conditioner while starting up may drop the line voltage enough to break the electronic latch. Another cause may be that the line voltage drops at certain peak times of the day (e.g., dusk). Local ac power is suspect in any malfunction which occurs on an intermittent basis.

- 1-18. Another game credit problem which may be either constant or intermittent in nature is a maladjusted antenna wire. The antenna wire is connected to the electronic latch and, if the wire is too long, game credit may be accidentally turned off, especially if the machine is in a carpeted location.

#### 1-19. PCB ADJUSTMENTS

- 1-20. Most of the PCB adjustments are quite simple and only involve changing a slide switch to the desired position or adjusting a small blue trim pot "by ear". A few others, however, are more complex and require an oscilloscope or, preferably, a frequency counter. This section contains only the adjustment procedures; consult the text for a fuller understanding of how these adjustments affect their associated circuits. See Figure 2-32 for the location of the PCB adjustments.

- a. Test Switch: While you are testing the PCB, you may wish to set this switch to the TEST position which will freeze the game timer and disable the crash mode. Always return the switch to the PLAY position before placing the PCB back in operation.

1-2 103-1

- **b. 1P-2P Switch:** If this switch is set to the 1P position, the player will receive one game per each coin he deposits; if set to the 2P position, he will receive two games.

- c. Volume Adjustment: This pot controls the gain of the audio amplifier. Adjust the volume to the preference of the location, and keep in mind that the machine will sound louder with the door off.

- d. Play Time Adjustment: This pot controls both the total game length and the crash time period. The play time counter (to the right of the lap score in the pit area) always begins counting down from 78 by 2's. Adjusting the play time pot causes the game counter to count down slower or faster. Adjusting for a longer game will also increase the length of the crash time, and affect score interpretation per the "rating card" posted on front of the CRT.

- e. Speed Adjustment: This adjustment controls the maximum velocity of the car. You must have either a logic probe or an oscilloscope to perform this adjustment. Attach the probe to B2-9 and adjust the pot until the signal (1 STOP) goes completely high when the car is traveling at maximum speed in third gear.

- f. "A" Adjustment: You <u>must</u> have an oscilloscope or a frequency counter to adjust the following three engine sounds (A, B & C). Clip the test instrument to C8-3 (the square wave output pin)

- and adjust the A pot for a 13 ms square wave or a frequency counter reading of 73 Hz.

- g. "B" Adjustment: Clip test instrument to D8-3 and adjust the pot for a 3.07 ms square wave or a frequency of 325 Hz.

- h. "C" Adjustment: Clip test instrument to E8-3 and adjust the pot for a 7.42 ms square wave or a frequency of 412 Hz.

- i. Screech Adjustment: This pot adjusts both the screech and crash sounds simultaneously. Adjust the pot by ear for the best sound output.

#### 1-21. LOGIC SYMBOLOGY

1.22 Table 1-1 describes the operation of the most common logic circuits found on the computer board. Those not covered in the table are explained at their first appearance in the computer board circuit description in Section 2. Logic circuits are identified in the text and on the schematic by their actual grid location on the PCB and their output pin number (e.g., gate A6-3 would be the gate with output pin 3 in the logic package at location A6 on the PCB). The logic levels on the PCB are 0 to +0.4 volts for LO and +2.6 to +5 volts for HI. Signal names overscored (e.g., START and pronounced "start not") go LO to initiate events and those not overscored go HI when active. Overscored signals are always at the logic level opposite to that of their non-overscored counterparts (i.e., START is always at a logic level opposite to START).

Table 1-1, Logic Symbology

| CVAADO                                                      | Table 1-1. Logic Symbo                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYMBOL                                                      | TRUTH TABLE/TIMING                                                                                                                             | OPERATION                                                                                                                                                                                                                                                                                                                                                                                  |

| AND GATE  1 2 3                                             | 1 2 3<br>LO LO LO 1 1 LO<br>LO HI LO 2 LO<br>HI HI HI 3                                                                                        | Output is HI only when all inputs are HI, otherwise output is LO. Rule applies for any number of inputs.                                                                                                                                                                                                                                                                                   |

| OR GATE                                                     | 1 2 3<br>LO LO LO 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                              | Output is HI when any input is Hł. Output is LO only when <u>all</u> inputs are LO.                                                                                                                                                                                                                                                                                                        |

| NAND GATE $\frac{1}{2}$ $0^{3}$ $\frac{1}{2}$ $3$           | 1 2 3<br>LO LO HI 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                          | Output is LO only when <u>all</u> inputs are HI, otherwise output is HI.                                                                                                                                                                                                                                                                                                                   |

| NOR GATE $\frac{1}{2}$ $\frac{3}{2}$ $\frac{3}{2}$          | 1 2 3<br>LO LO HI 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                          | Output is LO when any input is HI. Output is HI only when all inputs are LO.                                                                                                                                                                                                                                                                                                               |

| EXCLUSIVE OR GATE  1 2 3                                    | 1 2 3<br>LO LO LO 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                              | Output is HI when <u>either but not both</u> inputs are HI, otherwise output is LO.                                                                                                                                                                                                                                                                                                        |

| INVERTERS                                                   | IN                                                                                                                                             | The 2-input NAND or NOR gate can be used as inverters by tying one input to a fixed level or tying both inputs together.                                                                                                                                                                                                                                                                   |

| D-TYPE  4  4    5    6    6    6    6    6                  | t = n t = n + 1  D Q Q  LO LO LO t = n t = n + 1  LO HI LO HI  HI LO HI LO PULSE  HI HI HI  Truth Table valid only when  SD and RD are both HI | When both $S_D$ (direct set) and $R_D$ (direct reset) are HI, level at input D is transferred to output Q when input C (clock) goes HI. A LO on $S_D$ forces Q HI and $\overline{Q}$ LO. A LO on $R_D$ forces $\overline{Q}$ HI and Q LO. $S_D$ and $R_D$ predominate over all other inputs.                                                                                               |

| J-K MASTER SLAVE<br>FLIP-FLOP  B J Q 5  9 CLK  11 K CLR 110 | t = n t = n + 1  J K Q Q Q  LO LO - NO CHANGE t = n   t = n   LO HI - LO HI                                                                    | <ul> <li>When CLR is H1 and:</li> <li>1. Jand K are both LO, clock pulse has no effect on outputs Q and Q.</li> <li>2. Jand K are at opposite logic levels, negative-going clock edge transfers J level to Q and K level to Q.</li> <li>3. Jand K are both HI, each negative-going clock edge alternates outputs Q and Q.</li> <li>4. LO on CLR forces and holds Q LO and Q HI.</li> </ul> |

# 2. CIRCUIT DESCRIPTION

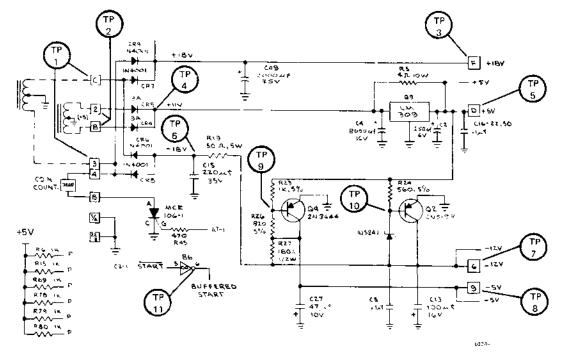

### 2-1. THE POWER SUPPLY

- 2-2. The power supply for GT-10 is a bit more complicated than in previous games because additional voltages are needed to operate new circuitry. The normal +5 volts is still used to power most of the ICs; however, the ROM requires -12 volts and the hybrids need -5 volts and -12 volts. The +18 volt source is used only to drive the audio amplifier.

- 2.3. The four circuits which generate the different voltages are very similar. See Figure 2.1. First, the 110 VAC line voltage is stepped down by the transformer(s) to 32 VAC and 16 VAC. These secondary voltages are then processed by the on-board power supply components to generate the DC supplies.

| TP 1: | OSCILLOSCOPE: 32 VAC     |        |               |                                     |

|-------|--------------------------|--------|---------------|-------------------------------------|

|       | VOM/VTVM: 32 VAC         |        |               |                                     |

|       |                          | TP 7:  | OSCILLOSCOPE: | - 12 VDC                            |

| TP 2: | OSCILLOSCOPE: 16 VAC     |        | VOM/VTVM:     | - 12 VDC                            |

|       | VOM/VTVM: 16 VAC         |        |               |                                     |

|       |                          | TP 8:  | OSCILLOSCOPE: | · 5 VDC                             |

| TP 3: | OSCILLOSCOPE: + 18 VDC   |        | VOM/VTVM:     | - 5 VDC                             |

|       | VOM/VTVM: + 18 VDC       |        |               |                                     |

|       |                          | TP 9:  | OSCILLOSCOPE: | - 0.6 VDC                           |

| TP 4: | OSCILLOSCOPE: + 11V PEAK |        | VQM/VTVM:     | - 0.6 VDC                           |

|       | VOM/VTVM: + 8.5 VDC      |        |               |                                     |

|       |                          | TP 10: | OSCILLOSCOPE: | - 1,0 VDC                           |

| TP 5: | LOGIÇ PROBE: High        |        | VOM/VTVM:     | - 1.0 VDC                           |

|       | OSCILLOSCOPE: + 5 VDC    |        |               |                                     |

|       | VOM/VTVM: + 5 VDC        | TP 11: | LOGIC PROBE:  | High pulse when the start switch is |

|       |                          |        |               | operated.                           |

| TP 6: | OSCILLOSCOPE: - 18 PEAK  |        | OSCILLOSCOPE: | High pulse when the start switch is |

|       | VOM/VTVM: - 15.5 VDC     |        |               | operated.                           |

Figure 2-1. The Power Supply and Buffered Start

- 2.4. +5 Volts: To create the regulated +5 volts needed by the ICs (and other components as well), the 16 VAC waveform at edge connector pins 2 and B is full-wave rectified by diodes CR4 and CR5. The resulting DC voltage is then filtered by capacitor C4 and then regulated to a constant +5 volts by the LM 309 voltage regulator.

- 2-5. +18 Volts: The 32 VAC waveform at pins 3 and C is rectified by CR7 and CR9, filtered by C49 and taken directly to the audio amplifier.

- 2-6. -12 Volts: Because the cathodes of CR6 and CR8 are wired to the transformer secondary, the resulting voltage will be negative with respect to ground. This waveform is filtered by C15 and then lowered to -12 volts by R19. The resulting voltage is regulated by transistor Q2 which acts like a shunt regulator to keep the voltage constant with respect to current.

- 2-7. -5 Volts: This circuit works similarly to the -12 volt circuit. Resistor R27 drops the -12 volts to -5 volts which is filtered by C27 and regulated by Q4.

- 2-8. The Pull-up Resistors: The pull-up resistors (R6, R15, R69, etc. and denoted by the schematic symbol "P") are used to provide a logic high source for inputs to ICs which need to be tied high. The resistor limits the total current drain through the LM 309.

### 2-9. BUFFERED START

2-10. In order to prevent a high, and possibly destructive, inductive kickback when the coil of the game counter is de-energized, a buffered start circuit has been incorporated so that the game counter is now tripped by a silicon controlled rectifier (MCR 106-1). START is inverted by B6 and this output is connected to the gate input of the rectifier. When the signal goes high, the silicon controlled rectifier conducts, thereby energizing the coil of the game counter. On the next half-cycle of the AC current, the rectifier is shut off by the AC waveform and the coil is deenergized.

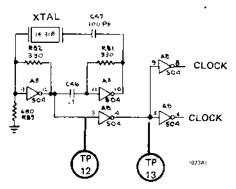

#### 2-11. THE OSCILLATOR

2-12. Since the operation of the computer is synchronous, it requires a master timing signal which is provided by the oscillator and known as the CLOCK. See Figure 2-2. The crystal oscillator generates a 14.318 MHz clock and it is kept oscillating by two closed-loop amplifiers which consist of a 330 ohm, 1/4 watt feedback resistor and an inverter. These amplifiers are coupled together by a 0.1 uf capa-

TP 12: LOGIC PROBE: High, low and pulsing. OSCILLOSCOPE: 14 MHz sine wave.

TP 13: LOGIC PROBE: High, low and pulsing.

OSCILLOSCOPE: Same as TP 12, except out of phase.

Figure 2-2. The Oscillator

citor (C46) and they operate out of phase with respect to each other. Inverter A8-4 is used as a buffer-amplifier and inverters A8-6 and A8-8 expand the oscillator's loading capacity. The clock signal is sinusoidal in form.

#### 2-13. THE ELECTRONIC LATCH

- 2-14. The electronic latch permits the starting of a new game when the coin is deposited and prevents the start of a game if the player attempts to obtain free game credit by inducing a static charge in the machine. See Figure 2-3 for the following discussion.

- 2-15. The control of game credit is accomplished by the presetting of the attract flip-flop C7-5 (see the credit and start circuit, Figure 2-4). Whenever the output of the latch circuit, signal Q, is high, the attract signal (ATRC) will also be high. If ATRC goes high, the computer is reset back to the ATTRACT mode and the game ends. In order for the game to begin, the electronic latch must be "latched" and signal Q must be low.

- 2-16. The latch cycle is started when  $\overline{COIN}$  (the normally high output of the credit circuit) goes low as the coin is deposited. This low takes the base of transistor Q6 low which causes the collector of that transistor to go high. This, in turn, causes Q8 to turn on and its collector goes low. Since the collector of Q8 is tied to  $\overline{COIN}$ , it keeps the latch circuit low even after  $\overline{COIN}$  returns high as the coin switch is released. The circuit is now said to be "latched" and will remain in the latched condition until shut off by a low R signal or a high antenna signal.

Figure 2-3. The Electronic Latch

- 2-17. R is the credit signal from B7-6 in the credit circuit. A low R drags the base of Q8 low and, since Q8 can no longer conduct, the latch cycle is broken. This toggles the attract flip-flop and resets the computer to the ATTRACT mode.

- 2-18. The same type of process is used to prevent players from gaining free game credit by inducing a static charge in the machine. When a large enough static charge is discharged to the machine, the antenna wire picks up the necessary current to create a high at the base of Q7. This causes Q7 to conduct and the low at its collector turns off Q8 and breaks the latch cycle.

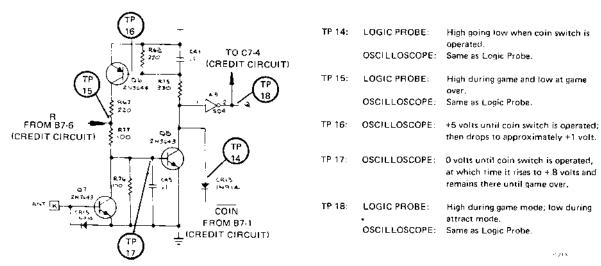

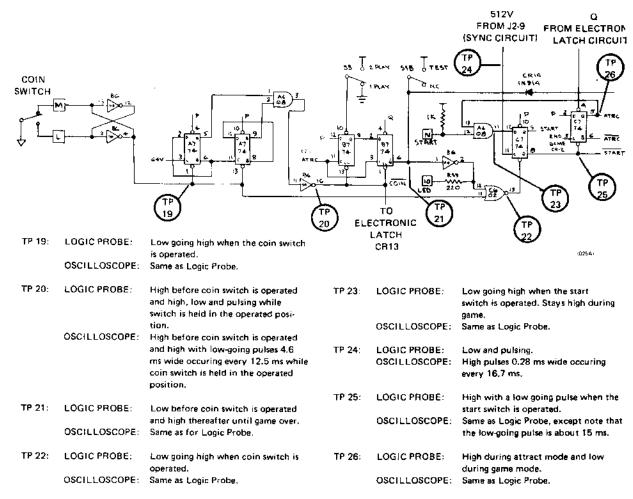

### 2-19. THE CREDIT AND START CIRCUIT

- 2:20. The credit portion of this circuit records the deposit of the coin and lights the credit lamp (LED). This provides game credit to the start circuit which is operated by the player to reset the PCB and begin the new game. The circuit is shown in Figure 2:4.

- 2-21. The deposited coin closes the normally-open side of the coin micro-switch, and the outputs of this switch are inverted by a debouncing circuit consisting of the two 86 inverters. The debouncing circuit eliminates undesired impulses created by the chattering of the coin switch contacts. The debouncing circuit outputs enter the clear inputs of flip-flops A7. These two flip-flops constitute an anti-cheat device, designed so that incidental or player-induced vibrations which may operate the coin switch trip wire will not produce game credit. In order to get the correct outputs from the A7 flip-flops, the coin switch contacts must make

for at least 128 horizontal sync pulses, or about 9 milliseconds. Since most incidental or player-induced vibrations produce a coin switch make of only a few microseconds, the Q outputs of the flip-flops will not go high and no game credit will result.

- However, if a coin is deposited, both A7 flip-flops are enabled, and when both of the Q outputs are high, pin 3 of AND gate A6 will also go high. This produces a low at pin 10 of inverter B6 which clears both B7 flip-flops. If the 1P/2P switch (1 play or 2 plays per coin) is set to the 1P mode, the preset input (pin 10) of B7 is held low and when COIN returns high, a high will appear at the Q output (pin-9) of B7. However, if the switch is set to the 2P position. when COIN goes low, the Q output (B7.9 will go low and stay low until the high at the D input (87-12) is clocked through by the ATRC signal. A low also appears at the Q output (B7-6) which is inverted at B6-2 and lights the credit LED. The same signal which cleared the 87 flip-flops (COIN) also drags the collector of transistor Q8 low and turns on the electronic latch (see Figure 2-3) which enables the attract flip-flop C7 at pin 4. Since the credit lamp must be lighted to enable gate C6, and since C6 enables the start flip-flop C7, the game cannot be started unless the credit lamp is lighted.

- 2-23. When the START switch is operated, pin 12 of AND gate A6 is pulled high by its 1K pull-up resistor, and since the ATRC line (A6-13) is already high, pin 11 of A6 will go high. This produces a high at the D input of start flip-flop C7 at pin 12. Since the clock input of this flip-flop is connected to vertical sync at 512V (J2-9), the high at the D input will be clocked out when 512V goes high and this is the START signal. Meanwhile, START goes low and

Figure 2-4. The Credit and Start Circuit

clears C7 at pin 1. This produces a low at the attract flipflop output which returns to shut off gate A6 at pin 13, thereby starting the game and locking out the start switch so the player cannot reset the computer during the game and gain additional time.

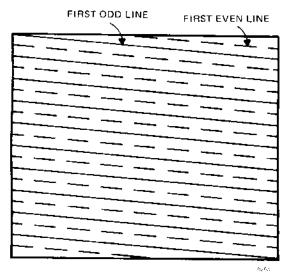

#### 2-24. TV MONITOR OPERATION

2-25. It is important that you understand the basics of TV monitor operation so that you can later comprehend how the signals generated by the PCB computer are synchronized with the operation of the monitor. We will not dwell on how the monitor receives and displays the information other than to say the electron beam illuminates spots on the phosphorescent coating of the CRT per the PCB signal information. What is critical is how these PCB signals are timed with the operation of the electron beam.

2-26. This type of TV monitor directs its electron beam in a fashion known as true interlaced raster scan. The TV screen picture (or raster) is composed of 260.5 horizontal lines stacked on top of one another. The electron beam always scans this raster whether or not it is receiving any PCB signals. The PCB signals simply modulate the electron beam so that spots of different intensity are illuminated. To see what this raster looks like, disconnect the PCB edge connector and turn the monitor brightness all the way up. The pattern of horizontal lines you see is the raster.

2-27. The electron beam begins its sweep in the top lefthand corner of the CRT and sweeps one horizontal line which ends at the right-hand side of the CRT. The electron beam is then repositioned at the left-hand side of the CRT prior to sweeping the next line. The process of moving the beam from the right side back to the left is known as hori-

2-4 103-1

Figure 2-5. Interlaced Raster Scan

zontal retrace and the beam must be blanked out (horizontal blanking) during retrace so no undesired illumination occurs.

2.28. The electron beam skips the second line, sweeps the third, is blanked out, sweeps the fifth line and so on. When the beam has swept all the odd numbered lines it is said to have completed one <u>odd field</u>. After completing the odd field, the beam is in the bottom right corner of the CRT, in order to begin the even sweep, it must be repositioned in the top center of the CRT where the first even line begins. The process of moving the beam vertically to the top of the screen is known as vertical retrace and, of course, the beam must be blanked out (vertical blanking) during vertical retrace.

2-29. The beam sweeps a full field of all the even numbered lines in the same fashion as it completed the odd field. This system of sweeping the odd lines first and then the even lines is known as interlacing. Two completely interlaced fields (one even and one odd) constitute one full frame. The electron beam sweeps the CRT at the rate of 30 frames per second.

#### 2-30. SYNCHRONIZATION AND BLANKING

2-31. A complex system of synchronization is required so the video signals generated by the PCB computer modulate the electron beam when the beam is in the correct part of the CRT. The essence of synchronization is timing. When sync is malfunctioning, the images appear to shift and move about the CRT because they are displayed in a different place each frame. The PCB signals must synchronize with the electron beam horizontally so that the information on each line is displayed in the proper sequence (and also vertically so that the vertical positioning of the images is correct). The sync pulses "tell" the electron beam when to start and stop its sweep, but do not otherwise control the raster. The sync circuit signals are also used in many other places in the PCB to time other operations with the TV monitor.

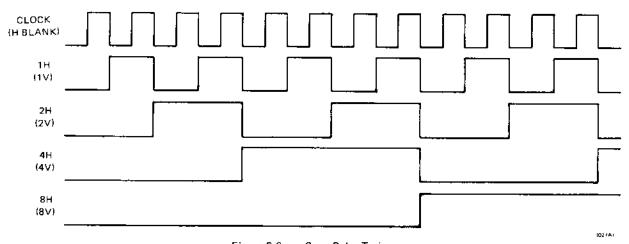

2-32. The basic timing for the horizontal sync circuit is the clock frequency. Vertical sync, however, runs off of horizontal sync. The horizontal and vertical sync counters count-down the clock pulses to form timed pulse trains (see Figure 2-6). The electron beam begins its sweep when horizontal reset (H RESET) goes low; this occurs after 451 clock pulses are counted out by the horizontal sync counters. The rising edge of the next H RESET pulse occurs

Figure 2-6. Sync Pulse Trains

103-1 2-5

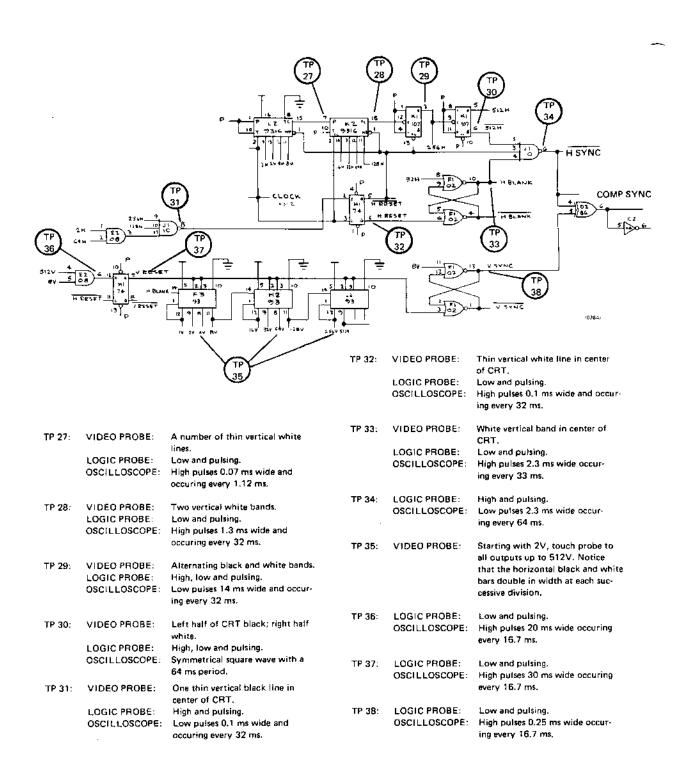

Figure 2-7. Synchronization and Blanking

when the electron beam reaches the right-hand side of the CRT, and the beam is reset back to the left-hand side by the monitor.

- 2-33. H RESET resets the sync counters after 451 clock pulses or counts. This is the end of the line (which actually occurs in the middle of the screen) so the counters must be started again. Horizontal blanking (H BLANK) is initiated by H RESET and lasts for 32 clock pulses. During this time information to be displayed in the next line is loaded into many parts of the PCB. The final horizontal sync signal (H SYNC) is composed of both H RESET and H BLANK and tells the electron beam when to start and stop its sweep.

- 2-34. Vertical reset serves the same purpose as H RESET except it occurs after 521 horizontal blanking pulses (or half lines) when the electron beam is in the lower right-hand corner of the CRT. There is no vertical blanking signal because no information needs to be loaded during vertical reset. The vertical sync signal serves the same purpose as H SYNC except it is timed to the vertical operation of the monitor.

- 2-35. The sync signals are generated in the following manner (see Figure 2-7). The clock starts L2 counting, and when L2 reaches TC (terminal count), TC goes high and stays high for one clock pulse. Since TC of L2 is connected to CEP (count enable parallel) of K2, when TC of L2 goes high, K2 is advanced by one count by the clock pulse at pin 2. K2 then counts 15 clock pulses and then TC of K2 goes high (after a total of 255 clock pulses). The falling edge of the 256th clock pulse causes K1-3 to go high and it will stay high until the 451st clock pulse when it is reset by H RESET. This 256H is divided again at K1-5 producing the 512th clock pulse or count which is the line that divides the CRT in half.

- 2-36. H RESET is an output of H1 and it is created by the addition of 256H, 128H, 64H and 2H and the result of J1-8 is a pulse 2H wide and 450 clock pulses from the last H RESET pulse. This is clocked through H1 by CLOCK producing the H RESET signal. Horizontal blanking is generated by H RESET which sets the RS flip-flop composed of the F1 gates. This causes H BLANK to go high and 32 clock pulses later it resets the RS flip-flop producing a blanking pulse 32 clock pulses wide after the H RESET pulse. Horizontal blanking is then gated with H RESET and 512H to produce H SYNC.

- 2-37. Vertical reset is generated by horizontal blanking which clocks counter F3 at pin 14. The counter divides the clock frequency by eight and the output of this counter goes to H2 where it is again divided eight times. The result-

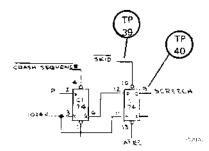

TP 30: LOGIC PROBE: High until brake switch is closed,

then drops low.

OSCILLOSCOPE: Same as Logic Probe.

TP 40: LOGIC PROBE: Low going high when brake

switch is closed,

OSCILLOSCOPE: Same as Logic Probe.

Figure 2-8. Screech Logic

ing signal is finally divided another four times by counter J2. J2 is allowed to divide only to four (a count of 512) because on the 521st count (512 plus 8V plus one more H RESET pulse) all the counters are reset by V RESET. Vertical sync is created by RS flip-flop which is set by V RESET and reset by 8V. This produces a high sync pulse which is four lines wide.

2-38. Because there are an odd number of half-lines being counted out, the electron beam must start at the center of the top of the screen every other field to achieve vertical reset. This is why the first line of the even field begins in the center of the CRT.

### 2-39. SCREECH LOGIC

2-40. This circuit (see Figure 2-8) generates the SCREECH signal, which creates the "screech" sound through the screech sound generator, and through the 8103 of the speed control circuit. ATTRACT must be high (a game started) to enable the screech circuit. If SKID (the "brakes applied" signal) goes low presetting flip-flop C1, the SCREECH signal will go high. When SKID returns high, 1024V will be clocked through two frames later turning the SCREECH signal off.

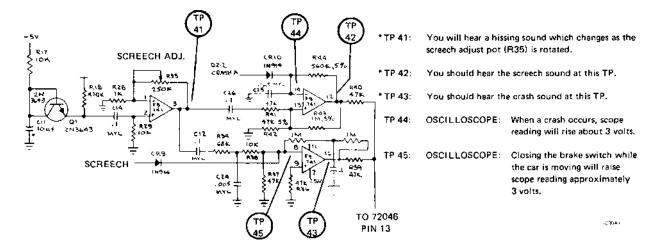

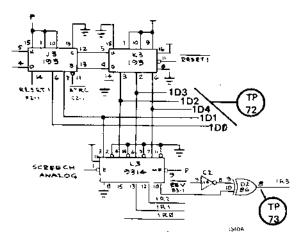

#### 2-41. SCREECH AND CRASH SOUND GENERATION

2-42. This circuit creates the screech and crash sound signals which eventually wind up in the audio amplifier where they are amplified so that they can be transformed into audible sounds by the speaker. The screech sound occurs when the brakes are applied (while the car is moving),

\*NOTE: To check test points 41 - 43, make a "noise probe" by connecting your video probe from capacitor C8 (in audio amp circuit) to TPs 41 - 43. If you hear the following sounds, the sound generator is O.K. although adjustment of R35 may be indicated. Volume of noise probe TPs may be adjusted with the volume pot.

Figure 2-9. Screech and Crash Sound Generator

and the crash sound results from a collision between the car and any one of the race course pylons. Both signals go through the 8103 hybrid before reaching the audio amplifier.

2-43. Refer to Figure 2-9. Transistor Q1 is the actual noise generator, and the signal from Q1 is amplified by F9-3. Trim pot R35 varies the feedback threshold of amplifier F9 which limits the number of "noise spikes" allowed through F9-3, thereby adjusting the quality of the screech and crash sounds. When the brake switch is closed and the car is moving, SKID is enabled. SKID presets flip-flop C1 in the screech logic and the SCREECH output at pin 9 goes high. When SCREECH goes high, the crash sound operational amplifier is shut off at F9-8 allowing only the screech sound to reach the 8103. The screech sound is always being generated except when disabled by CRASH A. If a crash occurs, CRASH A goes high which disables the screech amplifier at F9-14 allowing only the crash sound through to the 8103.

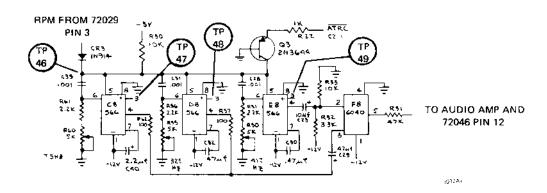

### 2-44. ENGINE RPM SOUND GENERATION

2-45. This circuit creates the sounds of the car engine both when it is idling and when it is moving. This is accomplished with three function generators and one electronic attenuator. See Figures 2-10 and 2-11.

2-46. When ATTRACT is high (during the attract mode), Q3 conducts and holds pins 5 of C8, D8 and E8 above ground potential disabling these function generators.

When a game is started, ATTRACT drops low and these function generators are enabled. Closing the gas pedal switch drops the RPM signal voltage from 0 volts to about -4 volts, which causes the function generators to modulate the frequencies of their signals.

2-47. The sound signals from C8 and D8 are the inputs to the attenuator (F8), and the signal from E8 modulates the amplitude of the attenuator output. The resulting sound signal is carried to the audio amplifier and then to the speaker. Note that each 566 function generator is individually adjustable by trim pots R60, R55, and R50. See Figure 2-11 for adjustment details.

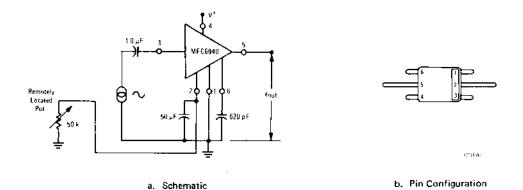

## 2-48. THE AUDIO AMPLIFIER

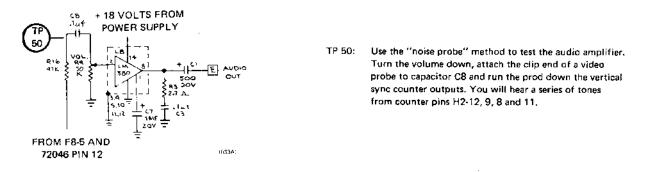

2-49. An audio amplifier is necessary to drive the speaker. See Figure 2-12. The sound signals enter the amplifier circuit through R16 and C8. The resistance of R4 determines the gain (the volume) and is adjusted by turning the small blue trim pot (marked "volume") found near the LM 380. The LM 380 is a transistor operated device which amplifies the sound signal to a level high enough to drive the speaker.

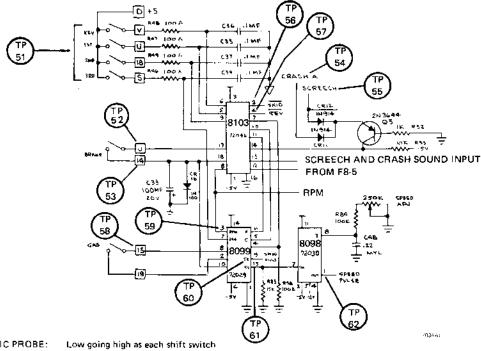

#### 2-50. SPEED CONTROL

2-51. This circuit uses three custom chips (8103, 8098 and 8099) which have been specifically designed for Gran

2-8 103-1

Figure 2-10. Electronic Attenuator

TP 48: OSCILLOSCOPE: When R55 is correctly adjusted, you OSCILLOSCOPE: Closing the gas pedal switch causes TP 46:

will see a 3.07 ms square wave. the RPM signal voltage to drop from

0 to - 4 volts.

OSCILLOSCOPE: When R50 is correctly adjusted, you TP 47: OSCILLOSCOPE: When R60 is correctly adjusted, you will see a 7.42 ms square wave.

will see a 13 ms square wave.

Figure 2-11. Engine RPM Sound Generator

Figure 2-12. The Audio Amplifier

TP 49:

TP 51: LOGIC PROBE:

is closed.

OSCILLOSCOPE: Same as Logic Probe.

TP 52: OSCILLOSCOPE: - 5 volts rising to + 2 volts when the

brake switch is closed or a crash

occurs.

VTVM: Same as Oscilloscope.

TP 53: Check voltage drop with the Oscilloscope or voltmeter

as you reach top speed in each gear.

Reverse . . . . . . - 0.8 volts 1st gear - - - - - - - 0.8 volts 2nd gear . . . . . . . - 1.7 volts 3rd gear ------ 3.5 volts

TP 54: LOGIC PROBE: Low going high when a crash

occurs.

OSCILLOSCOPE: 0 volts rising to + 3.5 volts at

VTVM: Same as Oscilloscope.

TP 55: LOGIC PROBE: Low going high when brake switch

closed.

OSCILLOSCOPE: 0 volts rising to + 3.5 volts when

brake switch is closed.

TP 56: LOGIC PROBE: High going low when brake switch

> is closed. Same as Logic Probe. OSCILLOSCOPE:

TP 57: LOGIC PROBE: High going low when gearshift is

in reverse.

OSCILLOSCOPE: Same as Logic Probe.

TP 58: Check with Oscilloscope or voltmeter. Voltage should

drop from + 5 volts to the indicated values as you reach top speed in each gear.

Reverse + 2.5 volts 1st gear ----- + 2.5 volts 2nd gear · · · · · · + 2.5 volts 3rd gear ..... + 4.3 volts

TP 59: Check with Oscilloscope or voltmeter. Voltage should

drop from 0 volts to the indicated values as you reach

top speed in each gear.

Reverse --- - 3,7 volts 1st gear ----- - 3.7 volts 2nd gear . . . - 3.8 volts 3rd gear .... - 4.3 volts

LOGIC PROBE: TP 60: Low when car is at rest; high when

car crashes.

OSCILLOSCOPE: Same as Logic Probe.

TP 61: Check with Oscilloscope or voltmeter. Voltages should

drop from 0 volts to indicated values as you reach top

speed in each gear.

Reverse - - - - 0.5 volts 1st gear - - - - 0.5 volts 2nd gear - - - - 1.2 volts 3rd gear .... - 2.6 volts

TP 62: LOGIC PROBE: Low when car at rest; low and puls-

ing when car is moving.

OSCILLOSCOPE: Following readings are to be taken

with car at top speed in each gear.

Reverse . . . . . 56 ms between pulses. 1st gear . . . . . . 58 ms between pulses. 2nd geer ..... 35 ms between pulses. 3rd gear ..... 16 ms between pulses.

Figure 2-13. Speed Control

2-10

Trak 10 and are available only through Atari, Inc. If one of these chips should fail, order a replacement by the part number on the chip itself. The speed control circuit controls the car speed, the engine RPM sound and the screech and crash sounds. Refer to Figure 2-13 for the following discussion.

#### NOTE

Schematic chip numbers 8103, 8099 and 8098 correspond to actual chip numbers 72046, 72029 and 72030.

- 2-52. 8103/72046 Input/Output Conditions: When any one of the shift switches is closed, the line connected to that switch goes high. Three of these switches (reverse, 1st and 2nd) are connected to pins 5, 6 and 9 of the 8103, and the 3rd gear switch is connected to pin 7 of the 8099. Closing these switches eventually controls the SPEED PULSES output from the 8098 as you will see under the discussion of the 8098.

- 2.53. The screech and crash sound signals enter the 8103 at pin 13. Pin 12 is the sound output. When the brake pedal switch is closed, SKID (pin 2) goes low and the SCREECH signal goes high. SCREECH disables the crash sound generator which allows only the screech sound through to the 8103. The screech sound is enabled through the 8103 by the closing of the brake switch, and continues to come out until capacitor C33 completely discharges through pin 17.

- 2-54. When a crash occurs, CRASH A goes low disabling the screech sound and allowing only the crash sound to reach the 8103. Both the screech and the crash sounds are controlled by the input to pin 14 which rises from -5 volts to +2.5 volts if you crash or step on the brake. So when a crash occurs, only the crash sound is enabled through the 8103. REV (reverse not) at pin 4 goes low whenever the reverse shift switch is closed. This signal goes to C2-9 (steering encoder circuit) and then to the ROM address multiplexers to control the direction of the car image.

- 2-55. 8099/72029 Input/Output Conditions: Pins 2 and 8 of the 8099 are connected to the gas pedal switch and control the acceleration of the car. When the car is stationary or in gear with no gas, pin 8 will be +5 volts. When you step on the gas, this will drop to approximately 2.4 volts in first and second gears and rise to 4 volts in third. Pin 2, on the other hand, is at 0 volts when the car is stationary or in gear with no gas. When in first or second gear with the gas switch closed, pin 2 will rise to about +2.4 volts and will rise to 4 volts in third gear with the gas pedal depressed.

- 2.56. Pin 3 (RPM) is at 0 volts when the gas switch is open, and drops to about -3.8 volts when you step on the gas in first. When you shift into second, pin 3 rises to approximately -2 volts and then drops to about -3.8 volts as the car picks up speed. When you shift into third, it rises to -2 volts again and drops down to about -4.2 volts when the car reaches maximum speed. Top speed in reverse should produce about -3.8 volts at pin 3.

- 2-57. Pin 13 is the input to the 8098 Speed Pulse Generator. Pin 13 starts at 0 volts and drops to -0.5 volts at top speed in first gear. When you shift into second, it rises to about -2 volts and drops to about -3.8 volts as the car picks up speed. When you shift into third, it rises to -2 volts again and then drops down to about -4.2 volts when the car reaches maximum speed. Closing the reverse switch causes pin 13 to drop from 0 volts to -0.5 volts.

- 2-58. 8098/72030 Input/Output Conditions: As pin 7 of the 8098 drops lower and lower, the speed pulses from pin 1 increase in frequency. This frequency is adjustable by the SPEED ADJUST pot R84 (see Section 1 for more details on this adjustment). The input to pin 9 of the 8099 comes from D5-8 (the crash circuit) and is used to disable the speed pulses during the attract mode or during a crash. This pin must go high to disable.

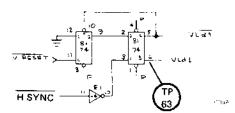

### 2-59. VLd1

2-60. VLd1 (vertical load one) is used to address the ROM for the vertical positioning of the car image. Refer to Figure 2-14. V RESET clocks the low from B1-12 out the Q output and this low waits at B1-2 until it is clocked through by H SYNC. The Q output (B1-5) presets B1-9 causing a high to appear at B1-9. This high is clocked through to B1-5 on the next H SYNC pulse. The result is a VLd1 pulse which occurs once per field and is one H SYNC pulse wide.

TP 63: LOGIC PROBE: Low and pulsing.

OSCILLOSCOPE: High pulse 63.5 ms wide occuring every 16.7 ms.

Figure 2-14. VLd1

103-1 2-11

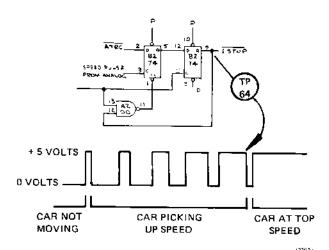

TP 64: LOGIC PROBE:

Low when car at rest.

Low and pulsing when car is accelera-

ting,

High when car reaches top speed in 3rd gear (provided speed pot is adjus-

ted correctly).

OSCILLOSCOPE: See waveform above.

Figure 2-15. 1 STOP

#### 2-61. 1 STOP

2-62. This signal is a ROM address which determines the speed with which the car image is moved. The input to this circuit (see Figure 2-15) is SPEED PULSE from pin 1 of the 8098 in the speed control circuit. As the car picks up speed, the speed pulses increase in frequency. When the car is stationary, 1 STOP is low. As the car starts moving, 1 STOP begins pulsing high and the pulses get closer together and longer in duration until the car reaches top speed in third gear, at which time the signal stays high.

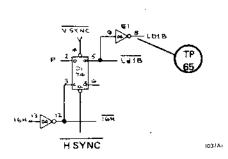

TP 65:

LOGIC PROBE: Low and pulsing,

OSCILLOSCOPE: High pulse 5 ms wide occurring

every 63.5 ms,

Figure 2-16. Ld1B

#### 2-63. Ld1B

2-64. Ld18 (load one B) is another ROM address; however, it is also used in several other places to load information into counters, etc. See Figure 2-16. H SYNC clears flip-flop D1. Sixteen clock pulses later, the high is clocked from the D input out the Q output and is inverted to become Ld1B. V SYNC disables this function once per field, producing a wider Ld1B pulse.

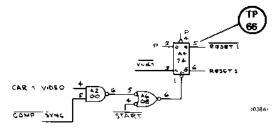

#### 2-65. RESET 1

2-66. The function of this signal is to tell the car motion circuits where to reposition the car image at the start of a new game or after the car is driven off the race course. When CAR 1 VIDEO encounters COMPOSITE SYNC (i.e., the car is driven off the screen), A2-6 goes low causing a low to appear at A6-6 and this low clears flip-flop A4. The flip-flop remains cleared until it receives the next VLd1 pulse which clocks the high from A4-2 out A4-5 and this signal is known as RESET 1. START serves a similar function in the circuit as the low from A2-6 in that it also clears RESET 1.

TP 66: LOGIC PROBE:

Low pulse when the game starts or the car is driven off the track.

OSCILLOSCOPE: Same as Logic Probe,

Figure 2-17. RESET 1

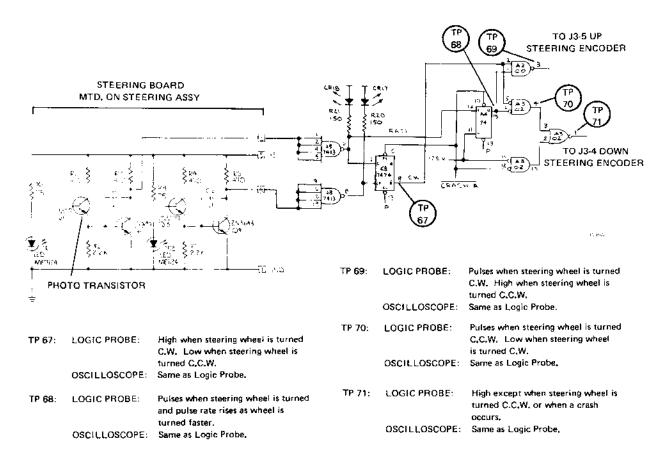

#### 2-67. STEERING CONTROL

2-68. The Steering Control circuit is shown in Figure 2-18. The two infrared light emitting diodes (LEDs) mounted on the steering assembly PCB are aimed directly at the two phototransistors and, as the slotted steering ring rotates, the path of light is broken up causing the phototransistors to pulse in a way which corresponds to the direction of the steering wheel rotation. These pulses are fed into four-input Schmitt triggers (J8) which clean up the pulses so the flip-flops can be triggered consistently.

2-69. When the steering wheel is turned in a clockwise direction, a rising edge occurs at the clock input of K8 before a rising edge reaches the D input. This causes the CW

Figure 2-18. Steering Control

(clockwise) signal to be high, which enables gate A2 to advance the steering encoder discussed below, and the steering encoder rotates the car in a clockwise direction. However, if the steering wheel is rotated in a counterclockwise direction, a rising edge will occur at the D input before a rising edge reaches the clock input. This produces a low CW signal.

- 2-70. The rate signal is clocked through A4 by 128V. If RATE and CW are high, the rising edge of 128V clocks a high out A4-9 and the counters of the encoder are incremented (advanced). If RATE and CW are both low on the rising edge of 128V, A3 will decrement the counters and the car image will be rotated in a counterclockwise direction.

- 2-71. During a crash, CRASH A goes low which presets K8 producing a low CW. It also presets A4 producing a high at A4-9 which shuts off gate A3. This allows A3 to pass 128V, decrementing the encoder counters and thereby causing the car image to spin uncontrollably during the crash.

2-72. Two LEDs (CR17 and CR18) have been included on the main PCB to facilitate troubleshooting the steering assembly. The pulses from the Schmitt triggers light the LEDs. If the LEDs flicker as you rotate the steering wheel, the steering assembly components are probably OK and the malfunction is most likely located in another part of the steering circuitry. If the LEDs do not flicker, look for foreign material between the infrared LEDs and the phototransistors of the steering PCB, physical damage to the steering assembly, broken connections or a malfunctioning Schmitt trigger.

#### 2-73. THE STEERING ENCODER

2-74. The steering encoder directs the ROM to read out the different aspects of the car image as the steering wheel is rotated. See Figure 2-19. The steering control circuit decides whether to pulse the UP (U at J3-5) or the DOWN (D at J3-4) line of the J3 up-down counter. As the UP input is pulsed, a binary code results at output pins 6 and 7 of J3. After 15 pulses into the UP input, a carry pulse is produced

103-1 2-13

TP 72: LOGIC PROBE:

Changes state twice per each complete car image revolution.

OSCILLOSCOPE:

Same as Logic Probe.

TP 73: LOGIC PROBE:

The signal from L3-10 will change

state when REV goes low.

OSCILLOSCOPE:

Same as Logic Probe.

Figure 2-19. Steering Encoder

at J3-12. This advances K3 which then produces another binary code at its output pins 2, 3, and 6. However, if the DOWN input to J3 is pulsed, J3 will count down from the last loaded number and, when it reaches 0, a borrow pulse is generated at J3-13 which decrements K3.

2-75. At the beginning of the game, or if the car is driven off the track, RESET 1 goes low. This resets the counters to zero and re-orients the car image. L3 is a latch which takes the 1D1, 1D2, 1D3 and 1D4 outputs from the counters and passes these signals on to the ROM multiplexers unless SCREECH is high. A high SCREECH latches up the last information from the counters and holds it until SCREECH goes low again. This causes the car image to continue moving in the same direction it was going when the brakes were applied, even if the steering wheel is turned which produces a realistic "slide" or "drift".

2.76. REV at C2-9 selects and inverts the most significant digit from L3, causing the car to back up in the opposite direction the car image was oriented in when the gear-shifter was placed in reverse. This is necessary to produce a realistic back-up sequence.

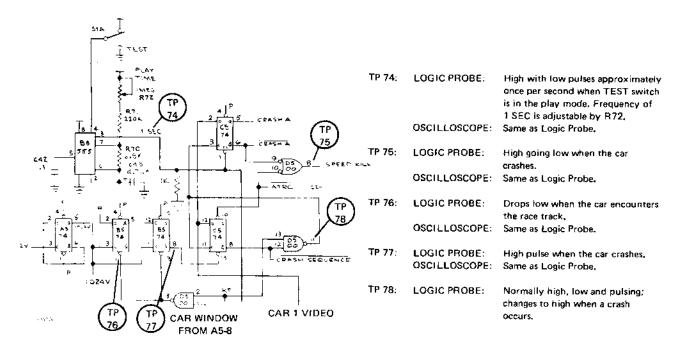

#### 2-77. CRASH AND PLAYTIME

2-78. This circuit has several functions: (1) it generates the crash signal when the car is driven into the pylons, (2) it

times the length of the game, and (3) it incorporates the TEST switch which is used to turn off the playtimer and crash mode when testing the board. See Figure 2-20 for the following discussion.

2.79. The 555 timer at B8 is the component which actually provides the timing. The amount of time it takes to charge C43 determines the pulse width out of the 555, and controls the period of time the output signal, 1 SEC, is high. R72 adjusts both the crash time period and the playtime by varying the amount of time required to charge the capacitor. The timer output is used to clear the crash flipflops after a crash has occurred. It is also the input to the game timer circuit which turns the game off after it counts a certain number of 1 SEC pulses. If the TEST switch is in the normal position, the 555 is allowed to produce the high 1 SEC pulses. However, if the switch is set to the TEST position, pin 4 of the 555 is grounded out and the game timer cannot count down.

This circuit also generates the crash signal (CRASH A) whenever the car window encounters the race track signal by gating the two signals together at D5-3. A crash produces a low at D5-3 which clears both B5 flip-flops and 2048V later, a low is clocked out B5-8. During the time B5-8 is high, flip-flop C5 is enabled and asks the question, "Is there a car on the pylons?" If the answer is "no" (i.e., one of the wheels has just barely glanced off a pylon), C5 continues to repeat the question until it is cleared at pin 13 by a low from B5-8. However, if the answer to C5's question is "yes", C5-8 goes low causing D5-11 to go high and the "yes" information is latched into C5 at pin 5 producing a high at CRASH A and a low at CRASH A. A low CRASH A produces a low SPEED KILL signal from D5-8 which stops the car motion. A low ATRC will also produce a low SPEED KILL and stop the car whenever the computer is in the attract mode.

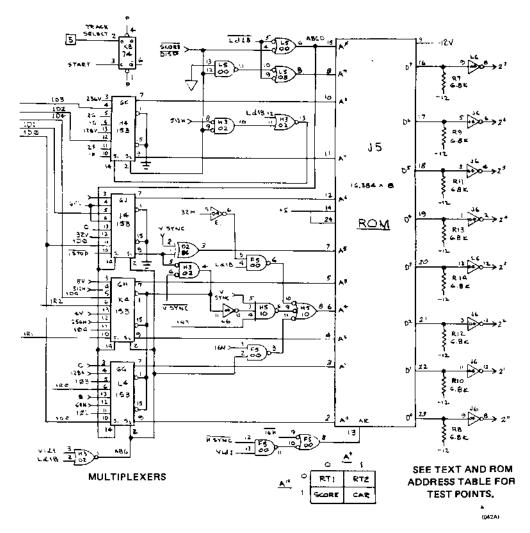

#### 2-81. THE MEMORY CIRCUIT

2-82. This circuit stores information which is later read out for the generation of the car image, the race track display and the score and timer displays. The main components are four multiplexers and one 16K ROM which has been specially programmed for Gran Trak 10 (See Figure 2-21).

2-83. The ROM is a memory unit which stores binary information. This information is read out of the ROM by the multiplexers, and these outputs go to other circuits where the information is used to form the different aspects

Figure 2-20. Crash and Playtime

of the car image, the race track display, etc. The ROM stores 2048 eight-bit words. Multiplexers select certain signals from a larger input of signals and these output signals are the "addresses" for the ROM. A different multiplexer address is required to read out each different eight-bit ROM word. For example, when information is needed for the generation of the car image, the multiplexers select the correct ROM address, and this selected signal reads out the desired car image information from the ROM. This ROM information is then fed into the car motion circuits and a new aspect of the car image is displayed on the CRT.

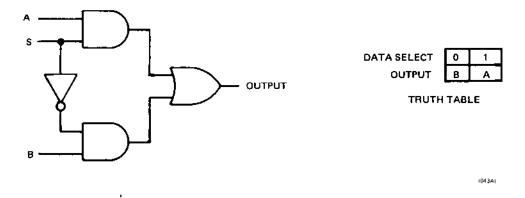

2-84. It is important to understand how the multiplexers function, so we have included a brief discussion of basic multiplexer operation. Figure 2-22 is the schematic of a basic two-input two-to-one data multiplexer. When the data select line (S) is high, the signal at the A input is reflected at the output. When S is low, signal B appears at the output and not A. The multiplexers used to address the ROM are nothing more than elaborations of the foregoing theme. The ROM requires multiplexers which can select one of two four-bit words.

2-85. The ROM itself is not a particularly complicated device; it is useful only because it can store so much information in a small space. You can visualize the ROM being constructed from 2048 rows of 8 diode gates each, where each gate is connected to one of the eight ROM outputs. Each diode in every row is specially programmed so that it reads out either a high or a low when it is addressed. Each

row of eight gates must be addressed by a different binary number. Since there are 2048 rows, the ROM requires a ten-bit address input. When this number is read out by the multiplexers into the ROM address input, each diode in the selected row reads out its high or low to one of the ROM outputs.

2-86. Troubleshooting the Memory Circuit: Some typical symptoms of malfunctions in this circuit are a distorted or missing car image, portions of the race track distorted or missing or distortion of the lap counter or game timer displays. If you suspect trouble in this section, the first step is to replace the ROM. A plug-in type receptacle has been provided to facilitate replacing the ROM. If the malfunction disappears, leave the new ROM in. However, the ROM failure rate is extremely low, so if a new ROM does not fix the problem, go on to the following troubleshooting procedures.

2-87. If the ROM is OK, next check the ROM addresses at ROM inputs  $A^0 - A^0$ . If these addresses are not OK, check the inputs to the multiplexers, the multiplexed outputs and any gating which may be between the multiplexer outputs and the ROM inputs. The ROM address table (Table 2-1) is invaluable in troubleshooting this section. We will use a car image problem to demonstrate the use of the address table. To find the correct address for the car image at the ROM inputs, look under the column labeled "CAR A". Then clip the scope probe to the device the ROM information is to be read into, which is shift register F6. The

103-1 2-15

Figure 2-21. The Memory Circuit

Figure 2-22. Basic Two-Input Two-to-One Multiplexer

2-16 103-1

Table 2-1. ROM Address Table

| CAR<br>A | SCORE<br>C | TIME<br>D | 1 R.T.<br>E | 2 R.T.<br>F | SPEED CODE<br>G | ROM<br>ADD | MULTIPLEX<br>ADD |

|----------|------------|-----------|-------------|-------------|-----------------|------------|------------------|

| 1        | 1          | 1         | 0           | 0           | 0               | AØ         |                  |

| 1        | 0          | 0         | 0           | 1           | 1               | 9          |                  |

| 103      | 1G         | 2G        | 256∨        | 256V        | 256V            | 8          | A+C+D+EFG        |

| 1D2      | 1F         | 2F        | 128∨        | 128V        | 128V            | 7          | A+C+D+EFG        |

| 1D1      | 1E         | 2E        | 64V         | 64V         | 64V             | 6          | A+C+D+EFG        |

| 1DØ      | 1D         | 2D        | 32V         | 32V         | 0G0 1 STOP      | 5          | A+C+D+EF+G       |

| 32H*     | 16V        | 16V       | 16V         | 16V         | 1R3 0 STOP      | 4          | A+C+D+EF+G       |

| 1D4      | 8V         | 8V        | 512H        | 512H        | 1R2             | 3          | A+CD+EF+G        |

| 104      | 4 V        | 4V        | 256H        | 256H        | 1R1             | 2          | A+CD+EF+G        |

| 103      | 1C         | 2C        | 128H        | 128H        | 1RØ             | 1          | A+C+D+EF+G       |

| 102      | 1B         | 2B        | 64H         | 64 H        | 1DØ             | 0          | A+C+D+EF+G       |

<sup>\* 32</sup>H-1 FIRST PART OF CAR

probe would be placed on the pin which is used to control when the data will be entered; in this case it is the shift load input (S/L) at pin 1. When the shift load pin goes low, the information will be loaded into the register. Then take the second probe and check the ROM address inputs and compare these with the information at the multiplexer inputs. Finally, compare all of this information with the table.

2-88. For example, first check ROM address A<sup>0</sup> (pin 15) with the second probe and you should see a high pulse occurring at the same time as the low shift load pulse. Note that this correctly corresponds to the ROM address table. Then look at A<sup>9</sup> (pin 8) and again there should be a high pulse occurring simultaneously with the low shift load pulse. Now go to A<sup>8</sup> and you should see signal 1D3 which will pulse high and low as the steering wheel is rotated. Continue to check all the address inputs in the same fashion. If you find some information which does not correctly correspond, start checking back through the multiplexers and gates (if any). If all the information checks out OK, examine the component that information is being loaded into (shift register F6 in this case).

2-89. To troubleshoot the multiplexers, first check the multiplexer inputs. If any of these do not check out, go to the section which produces the malfunctioning signal and locate the malfunction there. However, if all the multiplexer inputs are OK, check the data select lines by going to gates H3 and L5 and verifying the presence of the correct

Ld1B, VLd1, 512H and SCORE DISP inputs. If all of the data select inputs are also OK, you must check the multiplexers themselves.

2-90. The multiplexers are most easily checked using a logic comparator (see paragraph 1-11). The comparator will yield fast and accurate results. If you do not have a comparator, use the following procedure: first tie both multiplexer select lines low and look at the information from pins 7 and 9 (multiplexed outputs) which must match the inputs at pins 6 and 10 (multiplexer inputs). If OK, tie  $\rm S_1$  high and  $\rm S_2$  low, and pins 7 and 9 should match 5 and 11. If OK here, tie  $\rm S_1$  low and  $\rm S_2$  high, and 7 and 9 should equal 4 and 12. To check the last set, tie both select lines high and pins 7 and 9 should match 3 and 13.

### 2-91. THE WINDOW CONCEPT

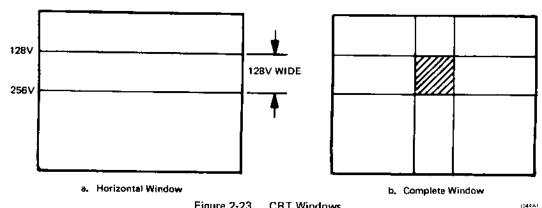

2-92. After the video signals are generated by the computer, they must be displayed on the desired part of the CRT. This is done by directing the signals to appear only within a certain area or "window". The key idea behind the window concept is that of limits or boundries.

2-93. Your video probe is a test instrument which can be used to display the windows directly on the CRT. To see a graphic display of windows, attach one probe clip to the negative (-) side of the video coupling capacitor (C44) and

<sup>- 0</sup> SECOND PART OF CAR

Figure 2-23. **CRT Windows**

run the other end across the sync counter outputs. You probably noticed, as you ran the probe across the vertical sync outputs, that the resulting windows were horizontal in appearance. The most confusing part of the window concept is the fact that it takes vertical signals to define a horizontal window and vice versa.

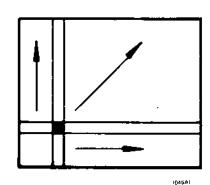

Examine Figure 2-23a and notice the vertical signat 256V which defines a horizontal line approximately half way down the CRT. Since the raster is composed of 521 half lines (or 260.5 whole lines), the signal 256V "tells" the electron beam to modulate its scan at the 256th half line down from the top of the screen and the lower half of the screen is white. This is why it takes a vertical signal to define a horizontal line a certain vertical distance down the CRT. If we create a similar line, except 128 half lines down the CRT, the result will be a band 128 half lines wide bounded at the top by 128V and at the bottom by 256V. This band is known as a horizontal window.

2-95. A complete window (Figure 2-23b) is created by generating a similar vertical window and gating the two windows together, so that we have an area with all four sides defined. The video signals are gated with the window so that they can only appear when the window occurs. The result is that the video can then only appear within the window.

#### 2-96. INTRODUCTION TO MOTION

2-97. The illusion of car motion is achieved by rapidly shifting the car image in the same way the illusion of motion is created on the motion picture screen by the film in the projector. The eye perceives this image shift as motion because of a phenomenon known as "retinal afterimage". The last seen image is "remembered" for a short time and as the position of the image is shifted a number of times in rapid succession, the eye "overlaps" the images and perceives the shifting process as continuous motion. Since the TV monitor has a frame rate of 30/second, it is possible to shift the car image so rapidly that the eye is completely fooled.

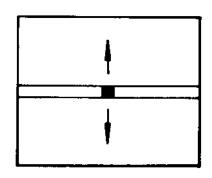

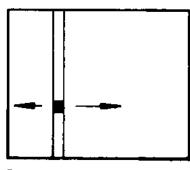

2.98. The speed or velocity of the car image is determined by the shift-rate/frame-rate ratio. If the image is shifted once every frame it will appear to move much faster than if it were shifted only once every three frames. The direction of the image is controlled by varying the rate at which the car image windows are shifted with respect to each other. Notice the vertical motion window in Figure 2-24a. As this window moves up and down, the image contained within it also moves up and down. Figure 2-24b shows the horizontal motion window which controls how the image is shifted from left to right. When the two windows are combined, the image can be vectored at any angle by individually varying the rate each window is shifted.

Figure 2-24. CRT Image Motion

2-18

Figure 2-25. Horizontal Count

2-99. The speed of the image is controlled by shifting the window with respect to sync. If the window frequency is the same as sync, it will be displayed in exactly the same place during each TV frame and it will appear stationary. However, if the window is generated a little slower or faster than sync, it will be shifted a certain amount each frame and will appear to move. This is done by entering different binary codes at the parallel inputs to the 9316 counters of the motion circuits. The stop code is that binary number which times the window with sync and therefore stops motion. Other codes cause a change in this relationship and the window is shifted with respect to sync.

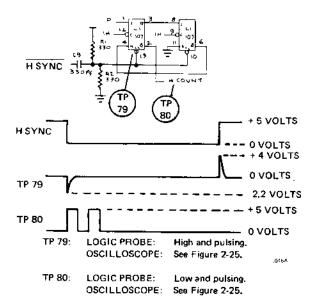

#### 2-100. HORIZONTAL COUNT

2-101. H COUNT is used to clock counter J2 (vertical positioning for the car image) twice per line. See the circuit in Figure 2-25. Capacitor C9 and resistors R1 and R2 create a very short reset pulse for both L1 flip-flops and this produces a high at both Q outputs. On the first 1H pulse, the  $\overline{Q}$  output at L1-2 goes low while L1-3 goes high. The  $\overline{Q}$  at L1-6 remains unchanged. On the second 1H pulse, L1-2 goes high and L1-6 goes low. On the third 1H pulse, both L1-2 and L1-6 go low and stay low until both flip-flops are again reset by the capacitor and resistors.

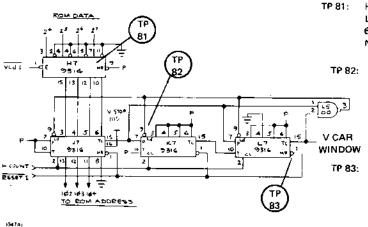

#### 2-102. VERTICAL CAR MOTION

2-103. The vertical car motion circuit is shown in Figure 2-26. When \$\overline{VLd1}\$ is high, the ROM data is latched into H7 and appears at the outputs when \$\overline{VLd1}\$ drops low again. This information is loaded into the parallel inputs of J7 when the line from L5-3 goes low. It takes 4096 H COUNT pulses to produce a low on this line. The counters start counting from the last number loaded in by L5-3 and count 4096 H COUNT pulses at which time a new number is loaded in.

2-104. The stop code for vertical motion is 3575 (1-1-1-0/1-1-1-1/1-0-1-1). When this number is entered into the counters, car motion ceases (4096 minus 3575 equals 521 which is the sync frequency). However, as the least significant digits of the stop code are changed, the 9316s begin their count from a different number and the resulting car window frequency is changed. For example, if the number 0-1-1-0 is loaded into J7, the window will move down at

Hold pin 1 of H7 low. Then using the Oscilloscope or the Logic Probe, check to see if the input signals at pins 3, 4, 6 and 7 are reflected at output pins 15, 13, 12 and 10. NOTE: CRT images break up when you hold  $\overline{VLd1}$  low.

To check counters, first look at pin 9 with the Video Probe and you should see a thin black line which moves with the car and is parallel to the bottom edge of the CRT. Then hold pin 9 low successively and check to see if the input signals of each counter (pins 3, 4, 5 and 6) are reflected at the outputs (pins 13, 12, 11 and 8).

VIDEO PROBE: At this test point, you will see the vertical car motion window which will appear as a white horizontal band.

Figure 2-26. Vertical Car Motion

103-1

Figure 2-27. Horizontal Car Motion

the slowest velocity (4096 minus 3574 equals 522 which is slightly faster than sync). Notice the RESET 1 line which resets the car image at the start of the game or after the car has been driven off the track.

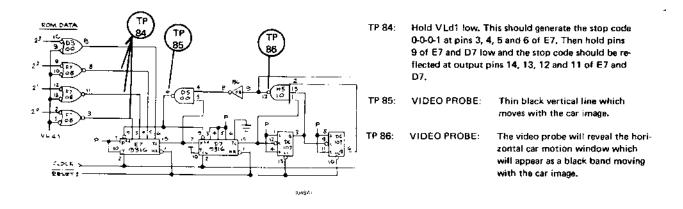

#### 2-105. HORIZONTAL CAR MOTION

2-106. The only real differences between the horizontal and vertical motion circuits are that the horizontal counters are clocked by CLOCK rather than H COUNT, and that different numbers are loaded into the counters. See Figure 2-27. VLd1 is normally low and goes high once per field. During the time VLd1 is low, the stop code 0-0-0-1 is loaded into E7. When VLd1 goes high, the ROM data is entered into £7 causing the horizontal motion window to shift.

#### 2-107. CAR DISPLAY

2-108. The car display circuit uses both the outputs of the ROM and the outputs of the car motion circuits to generate the different aspects of the car image. The ROM supplies the necessary information for the car images, the car motion circuits move the car windows (and hence where the car image can appear) and the display circuit displays all this information on the CRT.