## Am6012/6012A • Am6022/6022A

12-Bit High and Ultra-High Speed Multiplying D/A Converters

#### DISTINCTIVE CHARACTERISTICS

- All grades 12-bit monotonic over temperature

- Differential nonlinearity to ±0.012% (13 bits) max over temperature (A grades)

- Fast settling output current:

75ns (Am6022/A)

250ns (Am6012/A)

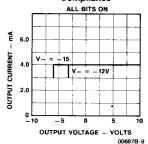

- Full scale current: 4mA

- High output impedance and compliance: −5 to +10V

- Differential current outputs

- · Low cost

- High-speed multiplying capability

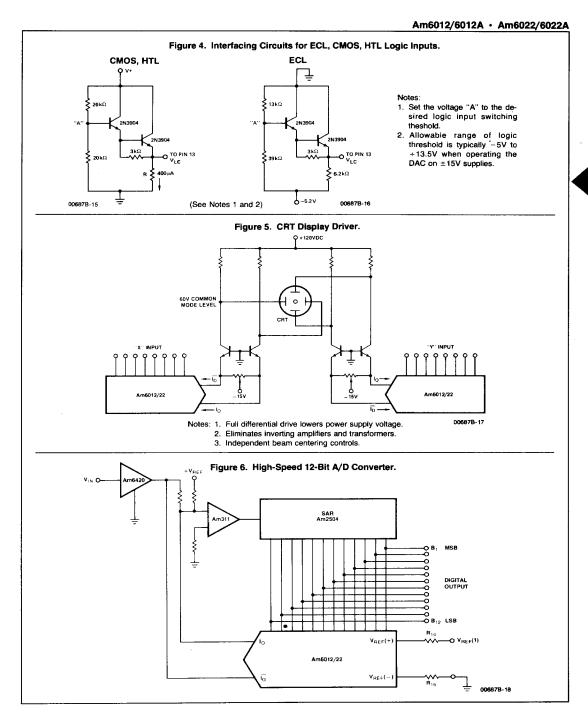

- Direct interface to TTL, CMOS, ECL, HTL, NMOS

- Low power consumption: 230mW (Am6012/A) 500mW (Am6022/A)

#### GENERAL DESCRIPTION

The Am6012/6022 series of 12-bit monolithic multiplying digital-to-analog converters represent new levels of speed, accuracy and low cost. The Am6012 and its high-performance, pin-compatible twin, the Am6022 are the first 12-bit DACs to be built using standard processing without the need for thin-film resistors or active trimming.

The Am6012/6022 design guarantees a more uniform step size than is possible with standard binarily weighted DACs. This  $\pm 1/2$  LSB differential nonlinearity is desirable in many applications where local linearity is critical. The uniform step size allows finer resolution of levels and in most applications is more useful than conformance to an ideal straight line from zero to full scale.

The Am6012/6022 have high voltage compliance, high impedance dual complementary outputs which increase their versatility and enable differential operation to effectively double

the peak to peak output swing. These outputs can be used directly without op amps in many applications. The dual complementary outputs can also be connected in A/D converter applications to present a constant load current and significantly reduce switching transients and increase system throughput. Output full scale current is specified at 4mA, allowing use of smaller load resistors to minimize the output RC delay which usually dominates settling time at the 12-bit level.

The Am6012/6022 series guarantees full 12-bit monotonicity for all grades and differential nonlinearity as tight as 0.012% (13 bits), for the A grades and 0.025% (12 bits) for the standard grades over the entire temperature range. Device performance is essentially independent of power supply voltage, and devices work over a wide operating range from +5 and, -12V to  $\pm 18$ V.

|                                                                                                                                                                                                                             | ORDERIN                                                                                                                                                                                                                                      | G INFORM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CONNECTION DIAC                                                                                                                                                                                                                           | CONNECTION DIAGRAMS - Top Views                                                                                                                                                        |                                         |                |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------|--|--|--|--|--|--|

| Package<br>Type                                                                                                                                                                                                             | Temperature<br>Range                                                                                                                                                                                                                         | Differential<br>Nonlinearity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Am6012<br>Order Number                                                                                                                                                                                                                    | Am6022<br>Order Number                                                                                                                                                                 | L-20-1<br>எ எ ் .                       | D-20-1, P-20-1 |  |  |  |  |  |  |

| Ceramic DIP Ceramic DIP Ceramic DIP Ceramic DIP Plassic DIP Plassic DIP Plassic DIP Plassic DIP Ceadless Chip-Carner ceadless Chip-Carner ceadless Chip-Carner Dice Dice Dice Dice Se available with burn- to be announced. | -55 to +125°C -55 to +125°C 0 to -70°C 0 to +70°C 0 to +70°C 0 to -70°C 0 to +70°C | ± 0.012% - 0.025% - 0.025% - 0.012% - 0.025% - 0.012% - 0.025% - 0.025% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.025% - 0.012% - 0.025% - 0.012% - 0.025% - 0.012% - 0.025% - 0.012% - 0.025% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0.012% - 0 | AM6012ADM<br>AM6012DM<br>AM6012DD<br>AM6012ADC<br>AM6012APC<br>AM6012PC<br>AM6012PL<br>AM6012ALM<br>AM6012ALM<br>AM6012ALM<br>AM6012ALM<br>AM6012ALM<br>AM6012AXM<br>AM6012XM<br>AM6012XM<br>AM6012XM<br>AM6012XM<br>AM6012XM<br>AM6012XM | AMB022ADM AMB022DM AMB022DM AMB022DC AMB022APC AMB022APC AMB022ALM** AMB022ALM** AMB022ALC** AMB022ALC** AMB022ALC** AMB022XX** AMB022XX** AMB022XX** AMB022XX** AMB022XX** AMB022XX** | 4 2 4 2 4 2 4 4 4 4 4 4 4 4 4 4 4 4 4 4 | db             |  |  |  |  |  |  |

3-17

00687B-ANA

#### Am6012/6012A · Am6022/6022A Am6012/6012A

MAXIMUM RATINGS (above which useful life may be impaired)

| Operating Temperature |               | Power Supply Voltage                                                       | ±18V       |

|-----------------------|---------------|----------------------------------------------------------------------------|------------|

| Am6012ADM, Am6012DM   | −55 to +125°C | Logic Inputs                                                               | -5 to +18V |

| Am6012ADC, Am6012DC   | 0 to +70°C    | Analog Current Outputs                                                     | -8 to +12V |

| Storage Temperature   | 65 to +125°C  | Reference Inputs V <sub>14</sub> , V <sub>15</sub>                         | V- to V+   |

| Lead Temperature      |               | Reference Input Differential Voltage (V <sub>14</sub> to V <sub>15</sub> ) | ±18V       |

| (Soldering, 60sec)    | 300°C         | Reference Input Current (I <sub>14</sub> )                                 | 1.25mA     |

#### **ELECTRICAL CHARACTERISTICS**

These specifications apply for  $V^+ = +15V$ ,  $V^- = -15V$ ,  $I_{REF} = 1.0 mA$ , over the operating temperature range unless otherwise specified.

|                     |                              |              |                                                                                          | 4            | Am6012A |               |                | Am6012       |              |              |  |

|---------------------|------------------------------|--------------|------------------------------------------------------------------------------------------|--------------|---------|---------------|----------------|--------------|--------------|--------------|--|

| arameter            | Descri                       | ption        | Test Conditions                                                                          | Min.         | Тур.    | Max.          | Min.           | Тур.         | Max.         | Units        |  |

|                     | Resolution                   |              |                                                                                          | 12           | 12      | 12            | 12             | 12           | 12           | Bits         |  |

|                     | Monotonicity                 |              |                                                                                          | 12           | 12      | 12            | 12             | 12           | 12           | Bits         |  |

|                     | Differential                 |              | D. V. A. Hardana                                                                         | -            |         | ±.012         | -              | -            | ±.025        | %FS          |  |

| D.N.L.              | Nonlinearity                 | ·            | Deviation from ideal step size                                                           | 13           | -       | -             | 12             | -            |              | Bits         |  |

| N.L.                | Nonlinearity                 |              | Deviation from ideal straight line                                                       |              | -       | ±.05          |                | -            | ±0.05        | %FS          |  |

| IFS                 | Full Scale Co                | urrent       | $V_{REF} = 10.000V$ $R_{14} = R_{15} = 10.000k\Omega$ $T_A = 25^{\circ}C$                | 3.967        | 3.999   | 4.031         | 3.935          | 3.999        | 4.063        | mA           |  |

|                     | 5.00 O1- Te                  |              |                                                                                          |              | ±5      | <b>(±20</b> ) | _              | ±10          | (±40)        | ppm/°C       |  |

| TCIFS               | Full Scale Te                | empco        |                                                                                          | -            | ±.0005  | ±.002         |                | ±.001        | ±.004        | %FS/°C       |  |

| v <sub>oc</sub>     | Output Volta<br>Compliance   |              | D.N.L. Specification guaranteed over compliance range R <sub>OUT</sub> > 10 megohms typ. | -5           | _       | +10           | -5             | -            | +10          | Volts        |  |

| I <sub>FSS</sub>    | Full Scale<br>Symmetry       |              | IFS - IFS                                                                                | _            | ±0.2    | ±1.0          | -              | ±0.4         | ±2.0         | μΑ           |  |

| Izs                 | Zero Scale C                 | Current      |                                                                                          | -            | -       | 0.10          | -              | -            | 0.10         | μΑ           |  |

| ts                  | Settling Time                | •            | To $\pm 1/2$ LSB, all bits ON or OFF, $T_A = 25^{\circ}C$                                |              | 250     | 500           | -              | 250          | 500          | nsec         |  |

| t <sub>PLH</sub>    | Propagation Delay – all bits |              |                                                                                          |              | 25      | 50            | -              | 25           | 50           | nsec         |  |

| COUT                | Output Capa                  | citance      |                                                                                          | -            | 20      | -             | _              | 20           | -            | рF           |  |

| VIL                 | Logic                        | Logic "0"    |                                                                                          | -            | -       | 0.8           | -              | -            | 0.8          | Volts        |  |

| VIH                 | Input<br>Levels              | Logic "1"    |                                                                                          | 2.0          | -       | -             | 2.0            | -            |              | 10.00        |  |

| IIN                 | Logic Input                  | Current      | V <sub>IN</sub> = -5 to +18V                                                             | -            | -       | 40            | -              | -            | 40           | μА           |  |

| VIS                 | Logic Input                  | Swing        | V- = -15V                                                                                | -5           | -       | +18           | -5             | -            | +18          | Volts        |  |

| REF                 | Reference C                  | Current      |                                                                                          | 0.2          | 1.0     | 1.1           | 0.2            | 1.0          | 1.1          | mA           |  |

| I <sub>15</sub>     | Reference B                  | lias Current |                                                                                          | 0            | -0.5    | -2.0          | 0              | -0.5         | 2.0          | μΑ           |  |

| dl/dt               | Reference II                 | nput         | $R_{14(eq)} = 800\Omega$ $CC = 0pF$                                                      | 4.0          | 8.0     | -             | 4.0            | 8.0          | -            | mA/μs        |  |

| PSSI <sub>FS+</sub> | Power Supp                   | ılv          | V+ = +13.5V to +16.5V, V- = -15V                                                         | _            | ±.00005 | ±.001         | -              | ±0.0005      | ±.001        | %FS/%        |  |

| PSSI <sub>FS</sub>  | Sensitivity                  | .,           | V- = -13.5V to -16.5V, V+ = +15V                                                         | T -          | ±.00025 | ±.001         | -              | ±.00025      | ±.001        | /61.0/11     |  |

| V+                  | Power Supp                   | olv          |                                                                                          | 4.5          | -       | 18            | 4.5            |              | 18           | Volts        |  |

| V-                  | Range                        | •            | V <sub>OUT</sub> = 0V                                                                    | - 18         |         | - 10.8        | -18            | -            | 10.8         |              |  |

| I+                  |                              |              | V+ = +5V, V- = -15V                                                                      |              | 5.7     | 8.5           |                | 5.7          | 8.5          | -            |  |

| 1-                  | Power Supp                   | oly          | V + + +3V, V 13V                                                                         |              | -13.7   | -18.0         |                | -13.7        | -18.0        | mA           |  |

| I+                  | Current                      |              | V+ = +15V, V- = -15V                                                                     |              | 5.7     | 8.5           |                | 5.7<br>-13.7 | 8.5<br>-18.0 | -            |  |

| 1~                  |                              |              |                                                                                          | <u> </u>     | -13.7   | -18.0         |                |              |              | <del> </del> |  |

| PD                  | Power                        |              | V+ = +5V, V- = -15V                                                                      | <del>-</del> | 234     | 312           | <del>  -</del> | 234          | 312          | mW           |  |

| ' D                 | Dissipation                  | 1            | V+ = +15V, V- = -15V                                                                     | -            | 291     | 397           | 1 -            | 291          | 397          | l            |  |

#### Am6022/6022A

### MAXIMUM RATINGS (above which useful life may be impaired)

| Operating Temperature |               | Power Supply Voltage                                                       | ±18V       |

|-----------------------|---------------|----------------------------------------------------------------------------|------------|

| Am6022ADM, Am6022DM   | -55 to +125°C | Logic Inputs                                                               | -5 to V+   |

| Am6022ADC, Am6022DC   | 0 to +70°C    | Analog Current Outputs                                                     | -8 to +12V |

| Storage Temperature   | -65 to +125°C | Reference Inputs V <sub>14</sub> , V <sub>15</sub>                         | V- to V+   |

| Lead Temperature      |               | Reference Input Differential Voltage (V <sub>14</sub> to V <sub>15</sub> ) | ±18V       |

| (Soldering, 60sec)    | 300°C         | Reference Input Current (I <sub>14</sub> )                                 | 1.25mA     |

#### **ELECTRICAL CHARACTERISTICS**

These specifications apply for  $V^+=\pm 15V$ ,  $V^-=\pm 15V$ ,  $I_{REF}=1.0$ mA, over the operating temperature range unless otherwise specified.

|                                      |                              |                                                                                          |          | Am6022A |       |       | Am6022  |        | ]       |

|--------------------------------------|------------------------------|------------------------------------------------------------------------------------------|----------|---------|-------|-------|---------|--------|---------|

| arameter                             | Description                  | Test Conditions                                                                          | Min.     | Тур.    | Max.  | Min.  | Тур.    | Max.   | Units   |

|                                      | Resolution                   |                                                                                          | 12       | 12      | 12    | 12    | 12      | 12     | Bits    |

|                                      | Monotonicity                 |                                                                                          | 12       | 12      | 12    | 12    | 12      | 12     | Bits    |

| D.N.L.                               | Differential                 | Deviation from ideal step size                                                           |          | İ       | ±.012 | -     | -       | ±.025  | %FS     |

| D.14.C.                              | Nonlinearity                 | Detration non-ideal step size                                                            | 13       |         | -     | 12    | -       | -      | Bits    |

| N.L.                                 | Nonlinearity                 | Deviation from ideal straight line                                                       | _        | ±0.012  | -     | -     | ±0.025  | -      | %FS     |

| IFS                                  | Full Scale Current           | $V_{REF} = 10.000V$ $R_{14} = R_{15} = 10.000k\Omega$ $T_A = 25^{\circ}C$                | 3.967    | 3.999   | 4.031 | 3.935 | 3.999   | 4.063  | mA      |

| TCIFS                                | Full Scale Tempco            |                                                                                          |          | ±5      |       |       |         | _      | ppm/°C  |

| . 0.42                               | - an occur tempor            |                                                                                          |          | ±.0005  | -     | -     | ±.00    | -      | %FS/°C  |

| v <sub>oc</sub>                      | Output Voltage<br>Compliance | D.N.L. Specification guaranteed over compliance range R <sub>OUT</sub> > 10 megohms typ. | 1        | 1       |       | -5    | _       | +10    | Volts   |

| I <sub>FSS</sub>                     | Full Scale<br>Symmetry       | IFS - IFS                                                                                |          | 7       | _     | -     | ±0.4    | _      | μА      |

| Izs                                  | Zero Scale Current           |                                                                                          |          | 0.10    | _     |       | 0.10    | -      | μА      |

| t <sub>S</sub>                       | Settling Time                | LSB, bits ON of FF = C                                                                   | 7 -      | 75      | -     |       | 75      | _      | nsec    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation<br>Delay - al s  |                                                                                          | _        | 10      |       | -     | 10      | _      | nsec    |

| Cout                                 | φυτ a                        |                                                                                          | -        | 10      | -     | -     | 10      | -      | pF      |

| VIL                                  | gic 1 c "0"                  |                                                                                          | -        | -       | 0.8   | -     | -       | 0.8    | Volts   |

| V <sub>IH</sub>                      | L Is Lt "1"                  |                                                                                          | 2.0      | -       | -     | 2.0   | -       | -      | 1 VORS  |

| In                                   | Louinput Current             | V <sub>IN</sub> = -5 to +15                                                              | -        | -       | 40    | -     | +       | 40     | μΑ      |

| V <sub>IS</sub>                      | Logic Input Swing            | V- = -15V                                                                                | -5       | -       | +15   | -5    | -       | +15    | Volts   |

| IREF                                 | Reference Current<br>Range   | V <sub>REF(-)</sub> = 0V                                                                 | 0.2      | 1.0     | 1.1   | 0.2   | 1.0     | 1.1    | mA      |

| I <sub>15</sub>                      | Reference Bias Current       |                                                                                          | 0        | -0.5    | -2.0  | 0     | -0.5    | -2.0   | μА      |

| dl/dt                                | Reference Input<br>Slew Rate | $R_{14(eq)} = 800\Omega$ $CC = 0pF$                                                      | -        | 16.0    | -     |       | 16.0    | -      | mA/μs   |

| PSSI <sub>FS+</sub>                  | Power Supply                 | V+ = +13.5V to +16.5V, V- = -15V                                                         | -        | ±.00005 |       |       | ±0.0005 |        | %FS/%   |

| PSSI <sub>FS</sub>                   | Sensitivity                  | V- = -13.5V to -16.5V, V+ = +15V                                                         | -        | ±.00025 |       | -     | ±.00025 |        | 7/F3/7/ |

| V +                                  | Power Supply                 | V 7 0V                                                                                   | 4.5      | -       | 18    | 4.5   | -       | 18     | Volts   |

| V-                                   | Range                        | V <sub>OUT</sub> = 0V                                                                    | -18      | _       | -10.8 | -18   |         | - 10.8 | VORS    |

| 1+                                   |                              | V+ = +5V, V- = -15V                                                                      |          | 11      |       |       | 11      | -      |         |

| 1                                    | Power Supply                 |                                                                                          |          | -24     | -     | -     | 24      | -      | mA.     |

| 1+                                   | Current                      | V+ = +15V, V- = -15V                                                                     | <b> </b> | 13.0    | -     | -     | 13.0    | _      | 4       |

| 1-                                   |                              |                                                                                          | -        | -24     | -     | -     | -24     |        | ļ       |

| PD                                   | Power                        | V+ = +5V, V- = -15V                                                                      | -        | 415     | -     |       | 415     | -      | mW      |

| 7                                    | Dissipation                  | V+ = +15V, V- = -15V                                                                     | -        | 555     | -     | -     | 555     | -      | L       |

#### **ACCURACY SPECIFICATIONS**

film resistors.

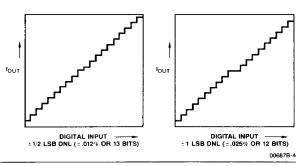

The design of the 6012/22 emphasizes differential linearity which is a measure of the uniformity of each step in the transfer characteristic. The circuit design, described in greater detail on page 6, requires resistor matching and tracking tolerances of 8 times lower than that of previous designs to achieve and maintain monotonicity over temperature. This advantage has been used in the 6012A/22A to provide 13-bit differential nonlinearity over temperature, a level of performance not generally available in previous designs, even when using thin

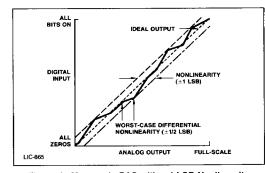

The figures illustrate that ±1/2 LSB (13-bit) differential nonlinearity guarantees a converter with 4096 distinct output levels. ±1 LSB D.N.L. guarantees monotonicity, so that when the input code is increased the output will not decrease. Note that nonlinearity, or deviation from an ideal straight line through zero and full scale, cannot be visually determined from the figures. In most applications, 12-bit resolution and differential linearity are more important than linearity. This is especially true in video and graphics, where the human eye has difficulty discerning nonlinearity of less than 5%.

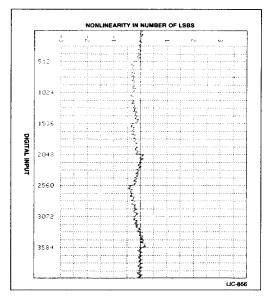

#### **DIFFERENTIAL NONLINEARITY** WORST CASE AT TEMPERATURE EXTREME

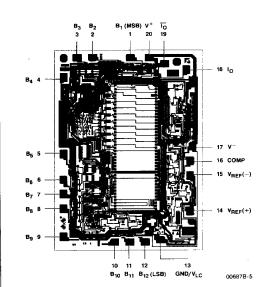

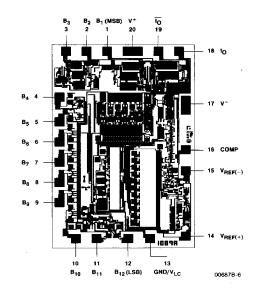

#### **METALLIZATION AND PAD LAYOUT**

#### Am6012

#### Am6022

DIE SIZE 0.093" X 0.134"

#### APPLICATION HINTS:

#### 1. Reference current and reference resistor.

There is a 1 to 4 scale factor between the reference current  $(I_{REF})$  and the full scale output current  $(I_{FS})$ . If  $V_{REF} = +10V$ and  $I_{FS} = 4mA$ , the value of the  $R_{14}$  is:

$$R_{14} = \frac{4 \times 10 \text{ Volt}}{4mA} = 10k\Omega$$

$R_{14} = R_{15}$

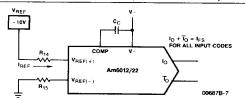

#### 2. Reference amplifier compensation. (Am6012)

For AC reference applications, a minimum value compensation capacitor (C<sub>C</sub>) is normally used. The value of this capacitor depends on the equivalent resistance at pin 14. The values to maximize bandwidth without oscillation are as fol-

#### MINIMUM SIZE COMPENSATION CAPACITOR $(I_{FS} = 4mA, I_{REF} = 1.0mA)$

(LO)

| n <sub>14</sub> (EQ) (K22) | CC (pr) |

|----------------------------|---------|

| 10                         | 50      |

| 5                          | 25      |

| 2                          | 10      |

| 1                          | 5       |

| .5                         | 0       |

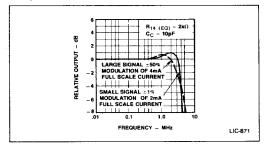

#### Reference Amplifier Frequency Response

006878.8

**Output Voltage** Compliance

Note: A 0.01µF capacitor is recommended for fixed reference operation.

| Reference Configuration           | R <sub>14</sub> | R <sub>15</sub>  | RIN | <b>c</b> c         | I <sub>REF</sub>                                                                      |

|-----------------------------------|-----------------|------------------|-----|--------------------|---------------------------------------------------------------------------------------|

| Positive Reference                | V <sub>R+</sub> | ov               | N/C | .01µF              | V <sub>R+</sub> /R <sub>14</sub>                                                      |

| Negative Reference                | ٥٧              | V <sub>R</sub> _ | N/C | .01µF              | -V <sub>R-</sub> /R <sub>14</sub>                                                     |

| Lo Impedance Bipolar<br>Reference | V <sub>R+</sub> | . 0V             | Vin | (Note 1)<br>Am6012 | (V <sub>R+</sub> /R <sub>14</sub> ) + (V <sub>IN</sub> /R <sub>IN</sub> )<br>(Note 2) |

| Hi Impedance Bipolar<br>Reference | V <sub>R+</sub> | VIN              | N/C | (Note 1)<br>Am6012 | (V <sub>R+</sub> - V <sub>IN</sub> )/R <sub>14</sub><br>(Note 3)                      |

| Pulsed Reference (Note 4)         | V <sub>R+</sub> | ov               | VIN | No<br>Cap          | (V <sub>R+</sub> /R <sub>14</sub> ) + (V <sub>IN</sub> /R <sub>IN</sub> )             |

- Notes: 1. The compensation capacitor is a function of the impedance seen at the  $\pm V_{REF}$  input and must be at least C = 5pF x  $R_{14(eq)}$  in  $k\Omega$ . For  $R_{14} < 800\Omega$  no capacitor is necessary.

- For negative values of V<sub>IN</sub>, V<sub>R+</sub>/R<sub>14</sub> must be greater than -V<sub>IN</sub> Max/R<sub>IN</sub> so that the amplifier is not turned off.

- For positive values of V<sub>IN</sub>, V<sub>R+</sub> must be greater than V<sub>IN</sub> Max so the amplifier is not turned off.

For pulsed operation, V<sub>R+</sub> provides a DC offset and may be set to zero in some cases. The impedance at pin 14 should be 800Ω or less.

- 5. For optimum settling time, decouple V- with 20 $\Omega$  and bypass with 22 $\mu$ F tantulum capacitor.

| co                   | DE FORMAT                                                                                                                         | CONNECTIONS                                       | OUTPUT SCALE                                                                                                              | MSE<br>B1                  | B2                         | <b>B</b> 3 (          | В4                    | B5 ł                  | B6 I                  | B7 I                  | B8                    | B9 (                  | B10                        | B11                   | LSB<br>B12                      | l <sub>o</sub><br>(mA)                                    | l <sub>o</sub><br>(mA)                                    | V <sub>OUT</sub>                                                  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|----------------------------|-----------------------|---------------------------------|-----------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------|

|                      | Straight binary; one polarity with true input code, true zero output.                                                             | a-c<br>b-g<br>R1 = R2 = 2.5K                      | Positive full scale<br>Positive full scale LSB<br>Zero scale                                                              | 1<br>1<br>0                | 1<br>1<br>0                | í                     | 1                     |                       | 1                     | 1                     | 1<br>1<br>0           | 1 0                   | 1<br>1<br>0                | 1<br>1<br>0           | 0 0                             | 3.999<br>3.998<br>.000                                    | .000<br>.001<br>3.999                                     | 9.9976<br>9.9951<br>.0000                                         |

| UNIPOLAR             | Complementary binary;<br>one polarity with<br>complementary input<br>code, true zero output.                                      | a-g<br>b-c<br>R1 = R2 = 2.5K                      | Positive full scale<br>Positive full scale – LSB<br>Zero scale                                                            | 0 0 1                      | 0                          | 0<br>0<br>1           | 0<br>0<br>1           | ō                     | 0                     | 0 0 1                 | 0<br>0<br>1           | 0<br>0<br>1           | 0<br>0<br>1                | 0 0 1                 | 0<br>1<br>1                     | .000<br>.001<br>3.999                                     | 3.999<br>3.998<br>.000                                    | 9.9976<br>9.9951<br>.0000                                         |

| SYM-                 | Straight offset binary;<br>offset half scale,<br>symmetrical about zero,<br>no true zero output.                                  | a-c<br>b-d<br>f-g<br>R1 = R3 = 2.5K<br>R2 = 1.25K | Positive full scale Positive full scale - LSB (+) Zero scale (-) Zero scale Negative full scale - LSB Negative full scale | 1<br>1<br>1<br>0<br>0      | 1<br>0<br>1<br>0           | 1<br>0<br>1<br>0      | 1<br>0<br>1<br>0<br>0 | 1<br>0<br>1<br>0<br>0 | 1<br>0<br>1<br>0<br>0 | 1<br>0<br>1<br>0<br>0 | 1<br>0<br>1<br>0<br>0 | 1<br>0<br>1<br>0<br>0 | 1<br>1<br>0<br>1<br>0      | 1<br>0<br>1<br>0      | 1<br>0<br>0<br>1<br>1<br>0      | 3.999<br>3.998<br>2.000<br>1.999<br>.001<br>.000          | .000<br>.001<br>1.999<br>2.000<br>3.998<br>3.999          | 9.9976<br>9.9927<br>.0024<br>0024<br>9.9927<br>9.9976             |

| METRICAL<br>OFFSET   | s complement;<br>o et half scale,<br>synmetrical about zero,<br>no true zero output<br>MSB complemented<br>(need inverter at B1). | a-c<br>b-d<br>f-g<br>R1 = R3 = 2.5K<br>R2 = 1.25K | Positive full scale Positive full scale - LSB (+) Zero scale (-) Zero scale Negative full scale - LSB Negative full scale | 0 0 1 1 1                  | 1<br>0<br>1<br>0<br>0      | 1<br>0<br>1<br>0      | 1<br>0<br>1<br>0<br>0      | 1<br>0<br>1<br>0      | 1<br>0<br>0<br>1<br>1<br>0      | 3.999<br>3.998<br>2.000<br>1.999<br>.001<br>.000          | .000<br>.001<br>1.999<br>2.000<br>3.998<br>3.999          | 9.9976<br>9.9927<br>.0024<br>0024<br>-9.9927<br>-9.9976           |

| OFFSET               | Offset binary;<br>offset half scale,<br>true zero output.                                                                         | e-a-c<br>b-g<br>R1 = R2 = 5K                      | Positive full scale Positive full scale - LSB + LSB Zero Scale - LSB Negative full scale + LSB Negative full scale        | 1<br>1<br>1<br>0<br>0      | 1<br>1<br>0<br>0<br>1<br>0 | 1<br>0<br>0<br>1<br>0      | 1<br>0<br>0<br>1<br>0 | 1<br>0<br>1<br>0<br>1<br>1<br>0 | 3.999<br>3.998<br>2.001<br>2.000<br>1.999<br>.001<br>.000 | .000<br>.001<br>1.998<br>1.999<br>2.000<br>3.998<br>3.999 | 9.9951<br>9.9902<br>.0049<br>.000<br>0049<br>-9.9951<br>-10.000   |

| WITH<br>TRUE<br>ZERO | 2's complement;<br>offset half scale<br>true zero output<br>MSB complemented<br>(need inverter at B1).                            | e-a-c<br>b-g<br>R1 = R2 = 5K                      | Positive full scale Positive full scale — LSB +1 LSB Zero scale -1 LSB Negative full scale + LSB Negative full scale      | 0<br>0<br>0<br>0<br>1<br>1 | 1<br>0<br>0<br>1<br>0      | 1 0 0 1 0 0           | 1<br>0<br>0<br>1<br>0 | 1<br>0<br>0<br>1<br>0 | 1 0 0 1 0 0           | 1<br>0<br>0<br>1<br>0 | 1<br>0<br>0<br>1<br>0 | 1<br>0<br>0<br>1<br>0 | 1<br>1<br>0<br>0<br>1<br>0 | 1<br>0<br>0<br>1<br>0 | 1<br>0<br>1<br>0<br>1<br>1      | 3.999<br>3.998<br>2.001<br>2.000<br>1.999<br>.001         | .006<br>.001<br>1.998<br>1.999<br>2.000<br>3.998<br>3.999 | 9.9951<br>9.9902<br>.0049<br>.000<br>-0.049<br>-9.9951<br>-10.000 |

#### ADDITIONAL CODE MODIFICATIONS

1. Any of the offset binary codes may be complemented by reversing the output terminal pair.  $3 \hbox{-} 22$

#### SEGMENTED DAC DESIGN INFORMATION

The design of a 12-bit D/A converter has traditionally required precision thin film resistors, a trimming method, and a binarily weighted ladder network. The 6012/22 is a 12-bit DAC which uses diffused resistors and requires no trimming, cutting, blowing, or zapping to guarantee monotonicity for all grades over the temperature range. A proprietary design technique, departing from the traditional R-2R approach used in virtually all high speed high resolution converters, provides inherent monotonicity and differential linearity as high as 13 bits. This guarantees a more uniform step size over the temperature range than available trimmed 12-bit converters. The converter's performance is immune to variations in temperature, time, process, and mechanical stress. The circuit also features differential high compliance current outputs, wide supply range, and a multiplying reference input.

In most converter applications, uniform step size is more important than conformance to an ideal straight line. Most 12-bit converters are used for high resolution rather than high linearity, since few transducers are more linear than ±0.1%. All classic binarily weighted converters require ±1/2 LSB (±.012%) linearity in order to guarantee monotonicity, which requires very tight resistor matching and tracking. This new circuit uses conventional bipolar processing to achieve high differential linearity and monotonicity without requiring correspondingly high linearity, or conformance to an ideal straight line.

One design approach which provides monotonicity without requiring high linearity is the MOS switch-resistor string. This circuit is actually a full complement to a current switched R-2R DAC since it is slower, has a voltage output, and if implemented at the 12-bit level would use 4096 low tolerance resistors rather than a minimum number of high tolerance resistors as in the R-2R network. Its lack of speed and density for 12 bits are its drawbacks.

The technique used in the Am6012 combines the advantages of both the R-2R and 2<sup>n</sup>R approaches. It is inherently monotonic, fast, and uses untrimmed resistors which are actually fewer in number than the classic R-2R ladder.

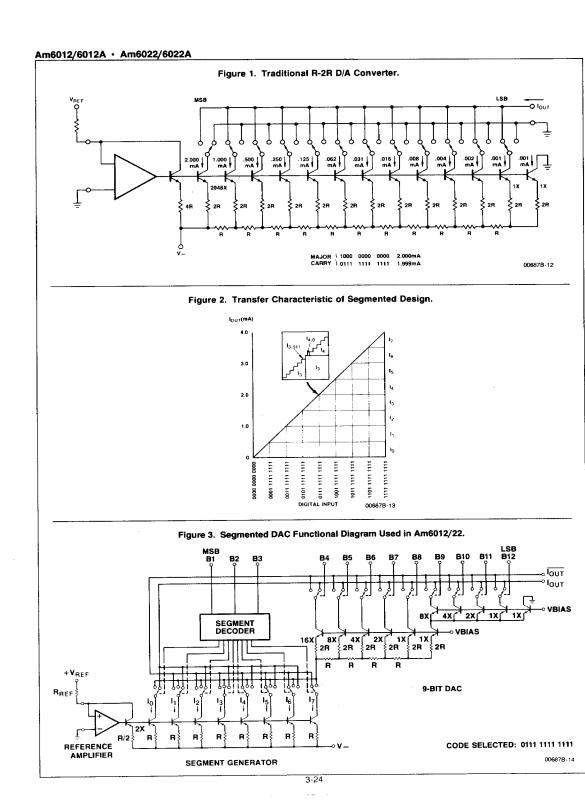

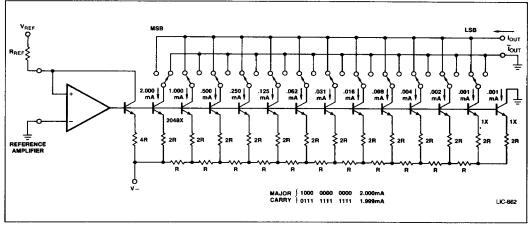

In order to properly describe the new design technique, the standard R-2R ladder approach used in previous 12-bit DAC's will first be discussed. Figure 1 shows the twelve-bit currents which are used in all possible binary combinations to generate 4096 analog output levels. The resistor ladder tolerance is most critical for the major carry, where the 11 least significant bits turn off and the most significant bit turns on. If the MSB is more than  $1\mu A$  low, or -.05%, the converter will be nonmonotonic. Table 1 shows the maximum tracking error which can be allowed over a  $100^{\circ}\text{C}$  range to maintain monotonicity, which is  $\pm 1$  LSB D.N.L. Achieving  $\pm 1/2$  LSB differential nonlinearity is especially difficult since it requires a tracking temperature coefficient of  $\pm 1.25$  ppm/°C.

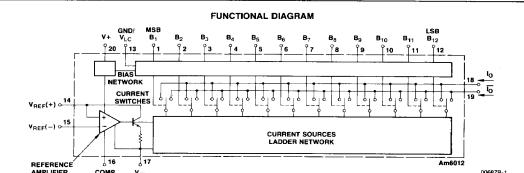

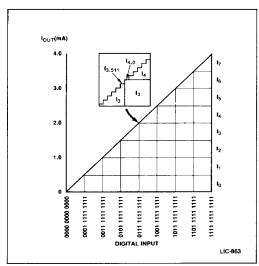

Figure 2 shows the transfer characteristic for the new technique, called the segmented DAC. The 4096 output levels are composed of 8 groups of 512 steps each. Each step group is gener-

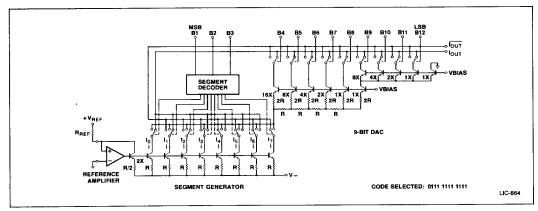

ated by a 9-bit DAC, and each of the segment slopes is determined by one of 8 equal current sources, as shown in Figure 3. The resistors which determine monotonocity are in the 9-bit DAC. The major carry of the 9-bit DAC is repeated in each of the 8 segments, and requires eight times lower initial resistor accuracy and tracking to maintain a given differential nonlinearity over temperature.

The operation of the segmented DAC may be visualized by assuming an input code of all zeroes. The first segment current  $I_O$  is divided into 512 levels by the 9-bit multiplying DAC and fed to the output,  $I_{OUT}$ . As the input code increases, a new segment current is selected for each 512 counts. The previous segment is fed to output  $I_{OUT}$  where the new step group is added to it, thus ensuring monotonicity independent of segment resistor values. All higher order segments feed  $\overline{I_{OUT}}$ .

At each segment endpoint, monotonicity is assured because no critical resistor tolerances are involved. For example, at the midpoint of the transfer characteristic, as shown in Figure 2,  $I_{4,0}$  is actually generated by the same segment resistor as  $I_{3,511}$  and has been incremented by the remainder current of the 9-bit DAC.

In the segmented DAC, the precision of the 8 main resistors determines linearity only. The influence of each of these resistors on linearity is four times lower than that of the MSB resistor in an R-2R DAC. Hence, assuming the same resistor tolerances for both, the linearity of the segmented approach would actually be higher than that of an R-2R design.

The step generator or 9-bit DAC is composed of a master and a slave ladder. The slave ladder generates the four least significant bits from the remainder of the master ladder by active current splitting utilizing scaled emitters. This saves ladder resistors and greatly reduces the range of emitter scaling required in the 9-bit DAC. All current switches in the step generator are high speed fully differential switches which are capable of switching low currents at high speed. This allows the use of a binary scaled network all the way to the least significant bit which saves power and simplifies the circuitry.

Diffused resistors have advantages over thin film resistors beyond simple economy and bipolar process compatibility. The resistors are fabricated in single crystal rather than amorphous material which gives them better long term stability and tracking and much higher moisture resistance. They are diffused at 1000°C and so are resistant to changes in value due to thermal and chemical causes. Also, no burn-in is required for stability. The contact resistance between aluminum and silicon is more predictable than between aluminum and an amorphous thin film, and no sandwich metals are required to enhance or protect the contact or limit alloying. The initial match between two diffused resistors is similar to that of thin film since both are defined by photomasks and chemical etching. Since the resistors are not trimmed or altered after fabrication, their tracking and long term characteristics are not degraded.

TABLE 1

RESISTOR SPECIFICATIONS

|                              | No. of    | Initial Matching<br>Required for |               | Required for DNL (ppm/°C) | Tracking Req'd. for ±1/2 LSB DNL (ppm/°C) |

|------------------------------|-----------|----------------------------------|---------------|---------------------------|-------------------------------------------|

| Ladder Type                  | Resistors | ±1 LSB DNL (%)                   | 0 Initial DNL | 1/2 LSB Initial DNL       | 1/4 LSB Initial DNL                       |

| Straight R-2R                | 37        | ±.05                             | 5             | 2.5                       | 1.25                                      |

| Segmented<br>3 Bits + 9 Bits | 24        | ±.4                              | 40            | 20                        | 10                                        |

# Am6012 12-Bit High-Speed DAC

### By Brian Gillings Advanced Micro Devices

Copyright © 1983 by Advanced Micro Devices, Inc.

Advanced Micro Devices cannot assume responsibility for use of any circuitry described other than circuitry entirely embodied in an Advanced Micro Devices' product.

00165A-ANA

#### INTRODUCTION

Advanced Micro Devices' Am6012 is the first 12-bit DAC ever built using standard processing without the requirements of thin film resistors and/or active trimming of individual devices. The result is a high-speed and high-accuracy converter with low cost. Offering a  $\pm \frac{1}{2}$  least significant bit (LSB) differential nonlinearity, the Am6012's uniform step size allows finer resolution of levels, and in most applications is more useful than conformance to an ideal straight line from zero to full scale.

#### **DESCRIPTION OF THE Am6012**

Figure 1 shows a simplified schematic for a traditional R-2R D/A converter used in previous 12-bit DACs. Twelve current sources are used in all possible binary combinations to gener-

ate the 4096 analog output levels. The resistor ladder tolerance is most critical at the major carry where the 11 least significant bits are turned off and the most significant bit (MSB) turns on. If the MSB is more than -0.05% low, the converter will be nonmonotonic. Achieving the initial resistor matching for  $\pm 1L\text{SB}$  differential nonlinearity ( $\pm 0.05\%$ ) has required precision resistors plus some sort of trimming method, such as laser trimming, cutting, blowing or zapping to guarantee monotonicity for all grades over the temperature range. The Am6012 uses a proprietary design technique, departing from the traditional R-2R design, which offers inherent monotonicity and differential nonlinearity as high as 13 bits (0.012%). The performance of the converter is immune to variations in temperature, time, process and mechanical stress.

Figure 1. Traditional R-2R D/A Converter

Figure 2. Transfer Characteristic of Segmented Design

Figure 2 shows the transfer characteristic for the new technique called a segmented ladder used in the Am6012. The 4096 output levels are composed of eight groups of 512 steps each

Each step of the group is generated by a 9-bit DAC and each of the segment slopes is determined by one of eight equal current sources as shown in Figure 3. The resistors that determine monotonicity are in the 9-bit DAC, and the major carry of the 9-bit DAC is repeated in each of the eight segments. This results in the need for eight times lower initial resistor accuracy and provides tracking to maintain a given differential nonlinearity over temperature.

If we assume that the input code is all ZEROES, the first segment current  $I_{\rm O}$  is divided into 512 levels by the 9-bit multiplying DAC and fed to the output  $I_{\rm OUT}$ . An increasing digital input code selects a new segment for every 512 counts. The previous segment is fed to output  $I_{\rm OUT}$  where the new group is added to it, thus ensuring monotonicity independent of segment resistor values.

In the segment DAC, the precision of the eight main resistors determines linearity only. The influence of each of these resistors on linearity is four times lower than that of the MSB resistor in a R-2R DAC. Thus, if the resistor tolerances were the same, then the segmented approach would actually be higher in linearity than that of the R-2R design.

Figure 3. Segmented DAC Functional Diagram Used in Am6012

The 9-bit DAC is composed of a master and a slave ladder. The slave ladder generates the four least significant bits from the remainder of the master ladder by using scaled emitters to split the current actively. All of the current switches in the step generator are fully differential switches capable of switching low currents at high speed. This allows the use of a binarily scaled network all the way to the least significant bit which saves power and simplifies the circuitry.

Like other monolithic DACs, the Am6012 has two types of errors that cannot be eliminated by adjustment. They are integral nonlinearity and differential nonlinearity. The integral nonlinearity shown in Figure 4 is the maximum deviation of the transfer function from the straight line drawn from actual zero through the full-scale output of the converter. Integral nonlinearity is expressed in LSBs or as a percentage of full-scale. Some products use the "best fit" straight line and specify the deviation in LSBs, however, this straight line will usually not terminate at the full-scale value. The user then must adjust his converter to this full-scale value, but is then unable to calibrate the converter to benefit from the better value offered by this specmanship. Most users are interested in the absolute value of the full-scale output and can calibrate it either manually or automatically.

Differential nonlinearity (DNL) is a measure of the deviation of each individual step size from the ideal least significant bit. A DNL of more than 1LSB defines nonmonotonicity, and a perfect converter has a zero DNL.

The Am6012A is specified as having 13 bits of DNL over temperature, a level of performance generally not available in other 12-bit converters even when using thin film resistors. This ±½LSB (13-bit) DNL guarantees the converter has 4096 separate and distinct output levels, whereas a ±1LSB DNL only guarantees monotonicity. It must be stressed again that these DNL figures are guaranteed over the complete temperature range. Also, DNL gives a measure of curve smoothness. The DAC transfer function may be more than 1LSB nonlinear and yet be smooth and useful with ½LSB DNL. This is especially true in video and graphics where the human eye has difficulty discerning nonlinearity of less than 5%. In most applications, 12-bit resolution and DNL are more important than integral nonlinearity. Figure 5 shows the nonlinearity of an actual device.

Figure 4. Monotonic DAC with ±1 LSB Nonlinearity and ±1/2 LSB Differential Nonlinearity

#### MULTIPLYING DAC

The Am6012 uses a fixed reference for most applications, but it can also handle an AC reference source. The output current  $I_{OUT}$  is a product of the digital input and analog reference voltage ( $V_{REF}$ ) or current ( $I_{REF}$ ).

The output current for current reference can be expressed as:

$$\begin{split} I_O &= 4 \cdot I_{REF} \Biggl( \frac{B_1}{2} + \frac{B_2}{4} + \frac{B_3}{8} + \frac{B_4}{16} + \frac{B_5}{32} + \frac{B_6}{64} + \frac{B_7}{128} + \\ & \frac{B_8}{256} + \frac{B_9}{512} + \frac{B_{10}}{1024} + \frac{B_{11}}{2048} + \frac{B_{12}}{4096} \Biggr) \end{split}$$

where B<sub>1</sub> is MSB.

The Am6012 has complementary/differential current outputs. The complement of  $I_{\rm O}$  is expressed as:

$$\overline{I}_0 = I_{ES} - I_0$$

where the addition of  $I_O$  and  $\overline{I_O}$  is a constant regardless of the digital code.

Figure 5. Nonlinearity Plot of Actual Device

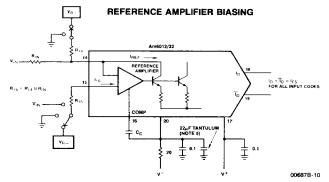

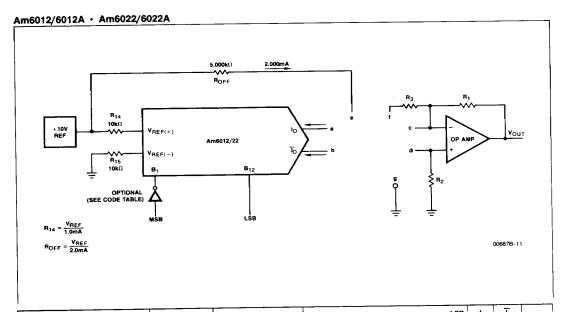

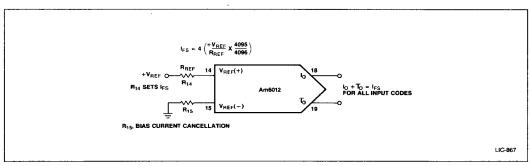

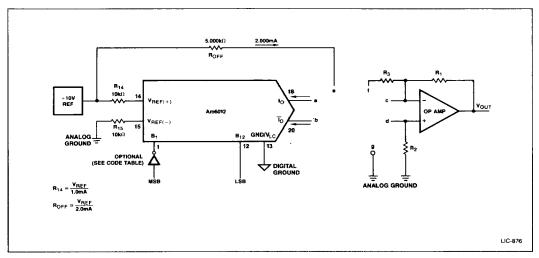

Figures 6 and 7 show the relationship of I<sub>REF</sub> to I<sub>O</sub> and I<sub>O</sub> for the basic DC connections. The reference may be positive or negative, and a bipolar output voltage may be obtained using the high-compliance current outputs alone or with an output op-amp, as described later.

An application of the external positive reference voltage (+V<sub>REF</sub>) forces current through a reference resistor (R<sub>REF</sub>) into the reference input (V<sub>REF</sub>(+)), which is a virtual ground created by the reference amplifier feedback loop. Reference current (I<sub>REF</sub>) is defined as:

A  $\pm 10V$  supply for  $\pm V_{REF}$  is recommended for optimum full-scale temperature operation. Resistor  $R_{15}$  minimizes the temperature coefficient of output offset voltage of the reference amplifier by matching it to  $R_{14}$ .

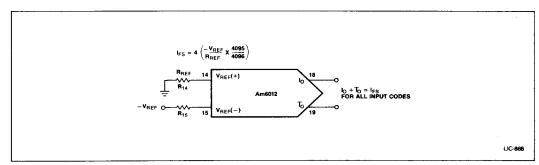

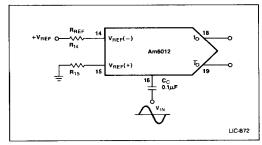

In negative reference applications, the external negative reference voltage is applied to the negative reference input ( $V_{REF(-)}$ ) of the Am6012. The voltage at ( $V_{REF(+)}$ ) pin tracks the voltage at ( $V_{REF(-)}$ ).  $I_{REF}$  flows from ground through  $I_{REF}$  into the ( $I_{REF(+)}$ ) input.

This connection produces high impedance at the  $(V_{REF(-)})$  input, thus isolating the signal source from the load. Again,  $R_{15}$  is normally used to cancel input bias current errors and is nominally equal to  $R_{REF}$ .

Figure 6. Positive Reference Connection

Figure 7. Negative Reference Connection

#### Am6012 Application Note

#### **BIPOLAR OPERATION**

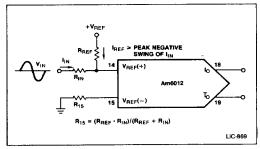

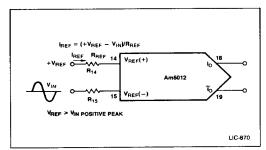

Figure 8 shows a low input impedance bipolar connection. The current into  $(V_{REF(+)})$  is  $I_{REF}$  plus  $I_{IN}$ .  $I_{REF}$  must be equal to or greater than the maximum negative value of  $I_{IN}$ , so the reference amplifier will not turn off. For a high-impedance connection (Figure 9)  $I_{RFF}$  is calculated from:

where  $\pm V_{REF}$  must be equal to or greater than the maximum positive value of  $V_{IN}$ . The  $I_{REF}$  current range is set at a minimum of 0.2mA and a maximum of 1.1mA. Fifty percent modulation is recommended to maintain speed and linearity (0.55mA  $\pm 0.5$ mA) over commercial temperature range.

Figure 8. Low Input Impedance Bipolar Reference

Figure 9. High-Input Impedance Bipolar Reference

#### REFERENCE AMPLIFIER COMPENSATION

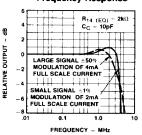

For AC reference applications, a minimum-value compensation capacitor ( $C_C$ ) is normally used. The value of this capacitor depends on the equivalent resistance seen at ( $V_{REF(+)}$ ). Table 1 gives the compensation capacitors required for different values of  $R_{REF}$ ; and Figure 10 shows the frequency response of the reference amplifier with  $R_{REF}=2K$  and  $C_C=10pF$ .

For the fastest response to a pulse, low values of R<sub>REF</sub> should be used resulting in a low C<sub>C</sub> value. When R<sub>REF</sub> is 800 ohms, C<sub>C</sub> is not required and a full-scale transition of 1 $\mu$ sec maximum and 500nsec typical is obtained. For fixed reference operation a 0.01 $\mu$ F capacitor should be used.

#### AC COUPLED MULTIPLICATION

Sometimes multiplying applications are more easily achieved by AC coupling, and a high impedance input is often required to avoid loading the high source impedance. Figure 11 uses the

**TABLE 1. MINIMUM SIZE COMPENSATION CAPACITOR**

| (I <sub>FS</sub> = 41 | nA, I <sub>REF</sub> = 1.0m.     | A) |

|-----------------------|----------------------------------|----|

| R <sub>14 (EQ)</sub>  | (k $\Omega$ ) C <sub>C</sub> (pl | F) |

| 10                    | 50                               |    |

| 5                     | 25                               |    |

| 2                     | 10                               |    |

| 1                     | 5                                |    |

| .5                    | 0                                |    |

$C_C$  pin as the input. This is possible because the  $C_C$  connection is 2VgE away from the ladder determining resistors internal to the Am6012 and gives wider bandwidth than using the reference amplifier.

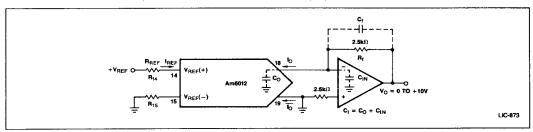

#### **VOLTAGE OUTPUTS USING Am6012**

The settling time for the Am6012 is specified for the current mode or the fastest operating mode. Many DAC applications require a current-to-voltage conversion. This can be achieved simply by connecting a low-value resistor directly to the output. If the output current is 4mA, a unipolar output would limit the resistor value to 1.25K ohms to ground because of the  $-5\mathrm{V}$  DAC output voltage compliance limitation. The output settling time is determined by the RC time constant produced by the DAC output capacitance of 20pF (plus stray capacitance) and the value of the load resistor. Settling to 0.01% ( $\pm1/2\mathrm{LSB}$ ) of full-scale would require approximately 300nsec, or nine time constants. An operational amplifier

Figure 10. Reference Amplifier Frequency Response

Figure 11. High-Impedance AC-Coupled Multiplication

is required if lower output impedance or larger output swings are desired, but some settling time will be lost because the output response is limited by the amplifier's slew rate and settling time. A feedback capacitor  $C_f$  (Figure 12) can compensate for the pole produced by the DAC output capacitance, op-amp input capacitance and the feedback resistor. Careful selection of this capacitor also optimizes the response time. Fastest operation is achieved by minimizing lead lengths, impedances and stray capacitances and bypassing the supplies to the DAC and operational amplifier.

The Am6012 has a maximum zero scale current of  $0.1\mu\text{A}$  over the full temperature range. This represents only 1/10LSB zero offset error. Therefore, the only error that needs to be corrected will be the operational amplifier offset voltage. A typical amplifier, such as the LF156, has an offset voltage (Vos) of 13mV over temperature and  $0.5\mu\text{V}/^{\circ}\text{C}$  per mV change in average temperature coefficient with Vos adjusted to zero. This will produce a total error of 1LSB over temperature, whereas if the LF156A were used only ¼LSB error would occur. In Figure 13 the Vos of the amplifier should be adjusted to zero with all of the bits turned OFF. One LSB is equal to 10/4096V = 2.44mV.

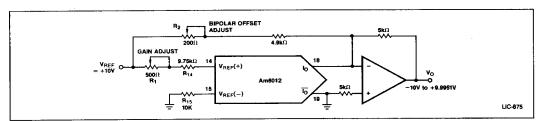

#### **UNIPOLAR OPERATION (Figure 13)**

#### Galn adjustment

Turn all the bits ON and adjust gain trimmer R<sub>1</sub> until the output is 9.9976V. This represents 1LSB less than the nominal 10V full-scale because the DAC outputs 4096 levels including zero so  $V_{FS}=4095/4096$  (10V) = 9.9976V.

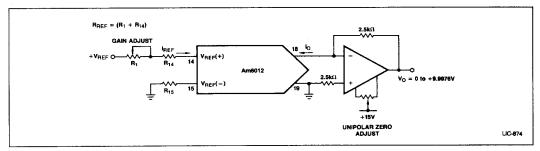

#### **BIPOLAR OPERATION (Figure 14)**

This configuration will provide a bipolar output voltage from -10.000V to 9.9951V for an offset binary digital input code.

#### Offset Adjustment

With all bits OFF, adjust offset trimmer  $\rm R_2$  to give -10.000V at the output.

#### Gain

Turn all the bits ON, and adjust gain trimmer  $R_1$  to give an output voltage of 9.9951V.

By using Figure 15 and Table 2, different input code formats and output polarities can be accommodated.

Figure 12. Voltage Output DAC

Figure 13. +10V Full-Scale Unipolar DAC

Figure 14. ±10V Full-Scale Bipolar DAC

#### Am6012 Application Note

Figure 15. Voltage Output Connection

TABLE 2. INPUT CODE FORMATS

| co                                                                    | DDE FORMAT                                                                                                                            | CONNECTIONS                                                    | OUTPUT SCALE                                                                                                              | MSI<br>B1             | _                          | <b>B</b> 3                 | B4                         | <b>B</b> 5                 | <b>B</b> 6                 | <b>B</b> 7                 | B8                         | В9                    | B10                        | B11                   | LSB<br>B12                 | I <sub>0</sub><br>(mA)                            | I <sub>0</sub><br>(mA)                                    | V <sub>OUT</sub>                                                  |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|-----------------------|----------------------------|-----------------------|----------------------------|---------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------|

| Straight binary; one polarity with true input code, true zero output. | a-c<br>b-g<br>R1 = R2 = 2.5K                                                                                                          | Positive full scale<br>Positive full scale - LSB<br>Zero scale | 1<br>1<br>0                                                                                                               | 1<br>1<br>0           | 1 1 0                      | 1 1 0                      | 1 1 0                      | 1 1 0                      | 1 1 0                      | 1<br>1<br>0                | 1<br>1<br>0                | 1<br>1<br>0           | 1 1 0                      | 0 0                   | 3.999<br>3.998<br>.000     | .000<br>.001<br>3.999                             | 9.9976<br>9.9951<br>.0000                                 |                                                                   |

| UNIPOLAR                                                              | Complementary binary; one polarity with complementary input code, true zero output.                                                   | a-g<br>b-c<br>R1 = R2 = 2.5K                                   | Positive full scale<br>Positive full scale - LSB<br>Zero scale                                                            | 0 0 1                 | 0 0 1                      | 0 0 1                      | 0 0 1                      | 0 0 1                      | 0 0 1                      | 0<br>0<br>1                | 0 0 1                      | 0 0 1                 | 0<br>0<br>1                | 0 0 1                 | 0 1 1                      | .000<br>.001<br>3.999                             | 3.999<br>3.998<br>.000                                    | 9.9976<br>9.9951<br>.0000                                         |

| SYM-                                                                  | Straight offset binary;<br>offset half scale,<br>symmetrical about zero,<br>no true zero output.                                      | a-c<br>b-d<br>f-g<br>R1 = R3 = 2.5K<br>R2 = 1.25K              | Positive full scale Positive full scale - LSB (+) Zero scale (-) Zero scale Negative full scale - LSB Negative full scale | 1<br>1<br>1<br>0<br>0 | 1<br>1<br>0<br>1<br>0      | 1<br>t<br>0<br>1<br>0      | 1<br>0<br>1<br>0           | 1<br>0<br>1<br>0<br>0      | 1<br>1<br>0<br>1<br>0      | 1<br>1<br>0<br>1<br>0      | 1<br>0<br>1<br>0<br>0      | 1<br>1<br>0<br>1<br>0 | 1<br>0<br>1<br>0           | 1<br>1<br>0<br>1<br>0 | 1<br>0<br>0<br>1<br>1      | 3.999<br>3.998<br>2.000<br>1.999<br>.001<br>.000  | .000<br>.001<br>1.999<br>2.000<br>3.998<br>3.999          | 9.9976<br>9.9927<br>.0024<br>0024<br>9.9927<br>9.9976             |

| METRICAL<br>OFFSET                                                    | 1's complement;<br>offset half scale,<br>symmetrical about zero,<br>no true zero output<br>MSB complemented<br>(need inverter at B1). | a-c<br>b-d<br>f-g<br>R1 = R3 = 2.5K<br>R2 = 1.25K              | Positive full scale Positive full scale – LSB (+) Zero scale (-) Zero scale Negative full scale – LSB Negative full scale | 0<br>0<br>0<br>1<br>1 | 1<br>0<br>1<br>0           | 1<br>0<br>1<br>0<br>0      | 1<br>1<br>0<br>1<br>0      | 1<br>0<br>1<br>0<br>0      | 1<br>0<br>1<br>0           | 1<br>0<br>1<br>0<br>0      | 1<br>1<br>0<br>1<br>0      | 1<br>0<br>1<br>0      | 1<br>0<br>1<br>0           | 1<br>0<br>1<br>0<br>0 | 1<br>0<br>0<br>1<br>1      | 3.999<br>3.998<br>2.000<br>1.999<br>.001<br>.000  | .000<br>.001<br>1.999<br>2.000<br>3.998<br>3.999          | 9.9976<br>9.9927<br>.0024<br>~.0024<br>~9.9927<br>~9.9976         |

| OFFSET<br>WITH                                                        | Offset binary,<br>offset half scale,<br>true zero output.                                                                             | e-a-c<br>b-g<br>R1 = R2 ≈ 5K                                   | Positive full scale Positive full scale - LSB + LSB Zero Scale - LSB Negative full scale + LSB Negative full scale        | 1<br>1<br>1<br>0<br>0 | 1<br>0<br>0<br>1<br>0      | 1<br>1<br>0<br>0<br>1<br>0 | 1<br>0<br>0<br>1<br>0      | 1<br>0<br>0<br>1<br>0      | 1<br>0<br>0<br>1<br>0      | 1<br>1<br>0<br>0<br>1<br>0 | 1<br>1<br>0<br>0<br>1<br>0 | 1<br>0<br>0<br>1<br>0 | 1<br>1<br>0<br>0<br>1<br>0 | 1<br>0<br>0<br>1<br>0 | 1<br>0<br>1<br>0<br>1<br>1 | 3.999<br>3.998<br>2.001<br>2.000<br>1.999<br>.001 | .000<br>.001<br>1.998<br>1.999<br>2.000<br>3.998<br>3.999 | 9.9951<br>9.9902<br>.0049<br>.000<br>0049<br>-9.9951<br>-10.000   |

| TRUE<br>ZERO                                                          | 2's complement;<br>offset half scale<br>true zero output<br>MSB complemented<br>(need inverter at B1).                                | e-a-c<br>b-g<br>R1 = R2 = 5K                                   | Positive full scale Positive full scale - LSB +1 LSB Zero scale -1 LSB Negative full scale + LSB Negative full scale      | 0<br>0<br>0<br>1<br>1 | 1<br>1<br>0<br>0<br>1<br>0 | 1<br>0<br>0<br>1<br>0      | 1<br>1<br>0<br>0<br>1<br>0 | 1<br>1<br>0<br>0<br>1<br>0 | 1<br>1<br>0<br>0<br>1<br>0 | 1<br>0<br>0<br>1<br>0      | 1<br>0<br>0<br>1<br>0      | 1<br>0<br>0<br>1<br>0 | 1<br>1<br>0<br>0<br>1<br>0 | 1<br>0<br>0<br>1<br>0 | 1<br>0<br>1<br>0<br>1<br>1 | 3.999<br>3.998<br>2.001<br>2.000<br>1.999<br>.001 | .000<br>.001<br>1.998<br>1.999<br>2.000<br>3.998<br>3.999 | 9.9951<br>9.9902<br>.0049<br>.000<br>-0.049<br>-9.9951<br>-10.000 |

#### TWO-QUADRANT MULTIPLICATION DAC

There are two types of two-quadrant multiplication: bipolar digital, where the digital code controls the output polarity; and bipolar analog, where the analog reference input controls output polarity.

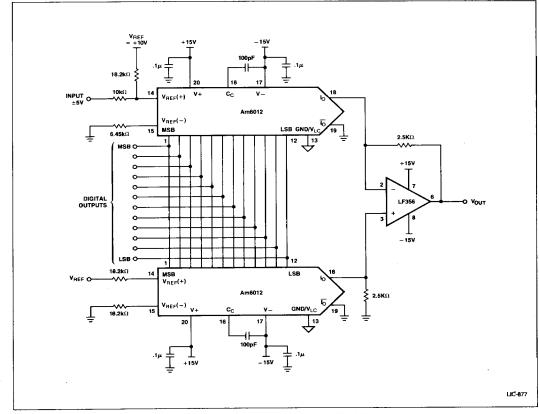

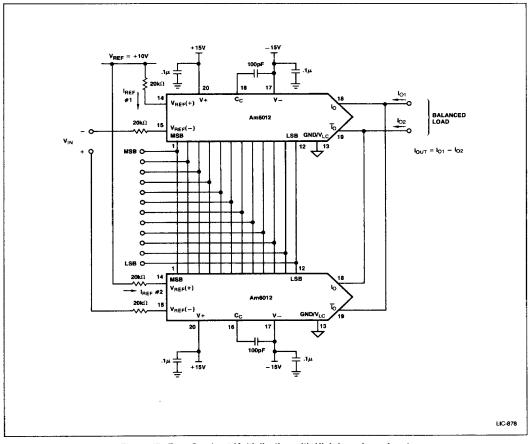

Figure 14 shows a bipotar digital two-quadrant multiplication with the output polarity controlled by an offset binary-coded input word. Two DACs are required for the bipolar analog method (Figure 16) because the Am6012 reference input cannot reverse the output polarity. A bipolar reference voltage is connected to the upper Am6012 and modulates the reference current by ±0.5mA around the quiescent current of 0.55mA. The lower Am6012 also has a reference current of 0.55mA, and both DACs have the same digital inputs. The lower Am6012 effectively subtracts out the quiescent 0.55mA of the upper Am6012 reference current at all digital input codes by differentially connecting them to an op-amp, thus the output voltage, VOUT, is a product of a digital input code and a bipolar analog reference voltage.

#### FOUR-QUADRANT MULTIPLICATION

By combining bipolar digital and bipolar analog (two-quadrant multiplication) the output analog polarity is controlled by the analog reference input or by the offset binary digital input code. In Figure 17 two Am6012s are connected to implement a four-quadrant multiplying DAC. The circuit shows that a differential

input signal can be accepted and differential output currents produced that can either be connected differentially to an op-amp to produce a voltage output or be used to drive balanced loads such as transformers, transducers and transmission lines.

#### USING THE Am6012 IN A/D CONVERTERS

Successive approximation is probably the method most widely used for implementing an ADC offering relatively fast conversion times with a low component count. Requiring 'n' comparisons for an 'n' bit conversion makes the technique capable of high speed.

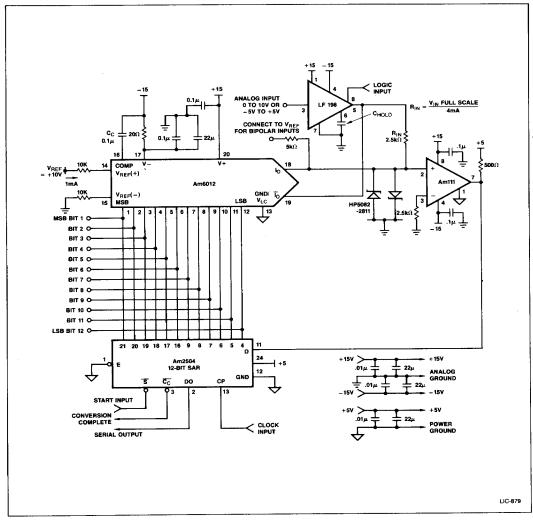

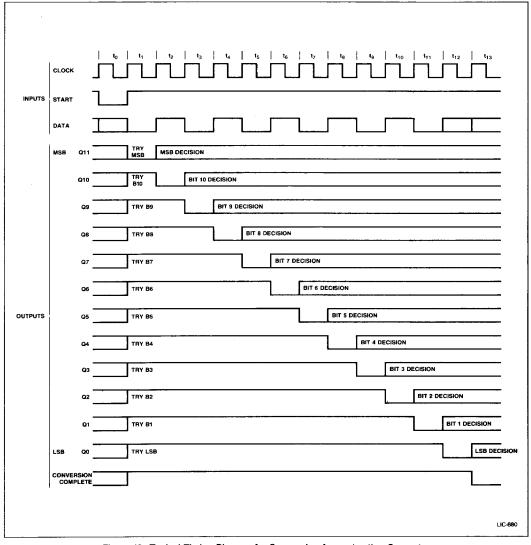

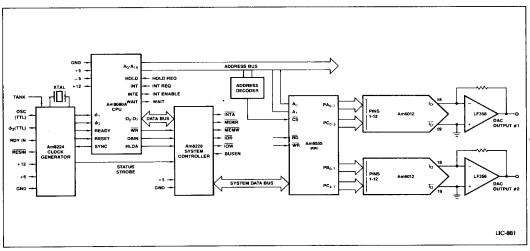

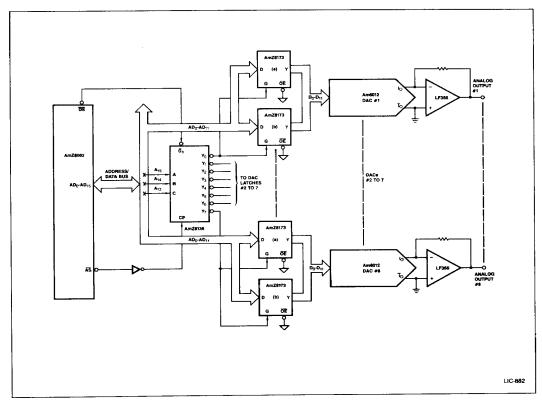

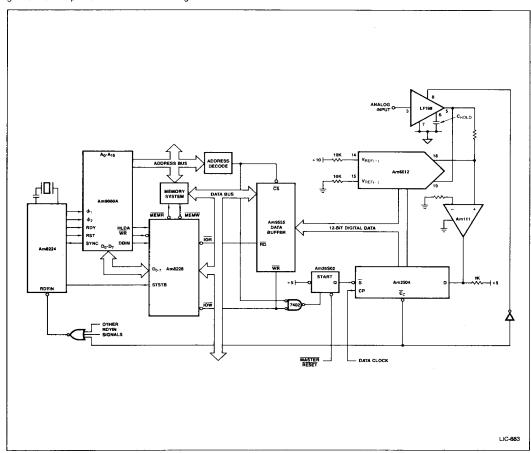

As illustrated in Figure 18, the most significant bit is turned ON first, and the DAC output is compared with the input. The bit is switched OFF or left ON, depending upon whether the input signal is smaller or larger than the DAC output signal. The remaining bits are successively switched ON and comparisons made until all respective bits are either left ON or switched OFF. Each time one bit is tried, the DAC is required to settle to within ±½LSB. The Am2504 Successive Approximation Register (SAR) contains the necessary A/D logic, and the timing diagram (Figure 19) relates to the Am2504. Holding the start input LOW for at least one clock period initiates the conversion. The MSB is set LOW and all of the other bits are set HIGH for the first trial. Each trial takes one clock period, proceeding from the most significant to the least.

Figure 16. Bipolar Analog Two-Quadrant Multiplication

Figure 17. Four-Quadrant Multiplication with High Impedance Input

The time required to complete a 12-bit successive approximation A/D conversion is determined by adding the duration of the 12 trials, the comparator decision delays and one clock cycle. Three dynamic considerations must be taken into account: DAC output current settling time to ±½LSB, the comparator propagation delay, and the SAR propagation delay and setup requirements.

For example, with 300nsec allowed for the DAC to settle to  $\pm 12$ LSB, and 300nsec for the comparator response time plus 50nsec SAR logic delay a complete conversion could result in 8.5 $\mu$ sec.

be equal to 2.5K, resulting in a time constant of 50nsec and a settling time of approximately 500nsec. Lowering the effective resistance at the summing node is a compromise between DAC settling time and comparator overdrive because the %LSB current is only  $0.5\mu A$  and, for an equivalent resistance of 500 ohms, would only result in a DAC output voltage corresponding to %LSB or 0.25mV, which is inadequate for most comparators. With  $R_{IN}$  of 2.5K this would result in %LSB of 1.25mV, which is an adequate overdrive for the Am111s (Figure 18), producing a response time of 200nsec. The propagation delay of the SAR is 50nsec. Hence, the total conversion time is  $1.5\mu sec$  for a full-scale signal range of 10V.

The input impedance of an ADC changes during the conversion process and can alter the performance of the input amplifier, or sample and hold amplifier if used. Because the comparison point can swing by a large amount, the input current can be modulated. The output impedance of the input amplifier is made LOW by the loop gain of the feedback amplifier. This gain reduces at high frequencies, and the output impedance rises to its open loop value, which is usually between 10 and 200 ohms.

Figure 18. Fast Precision Successive Approximation A/D Converter