# **Table of Contents**

| Sheet 1A                                     | Table of Contents                                                                                                                                                                                                        |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

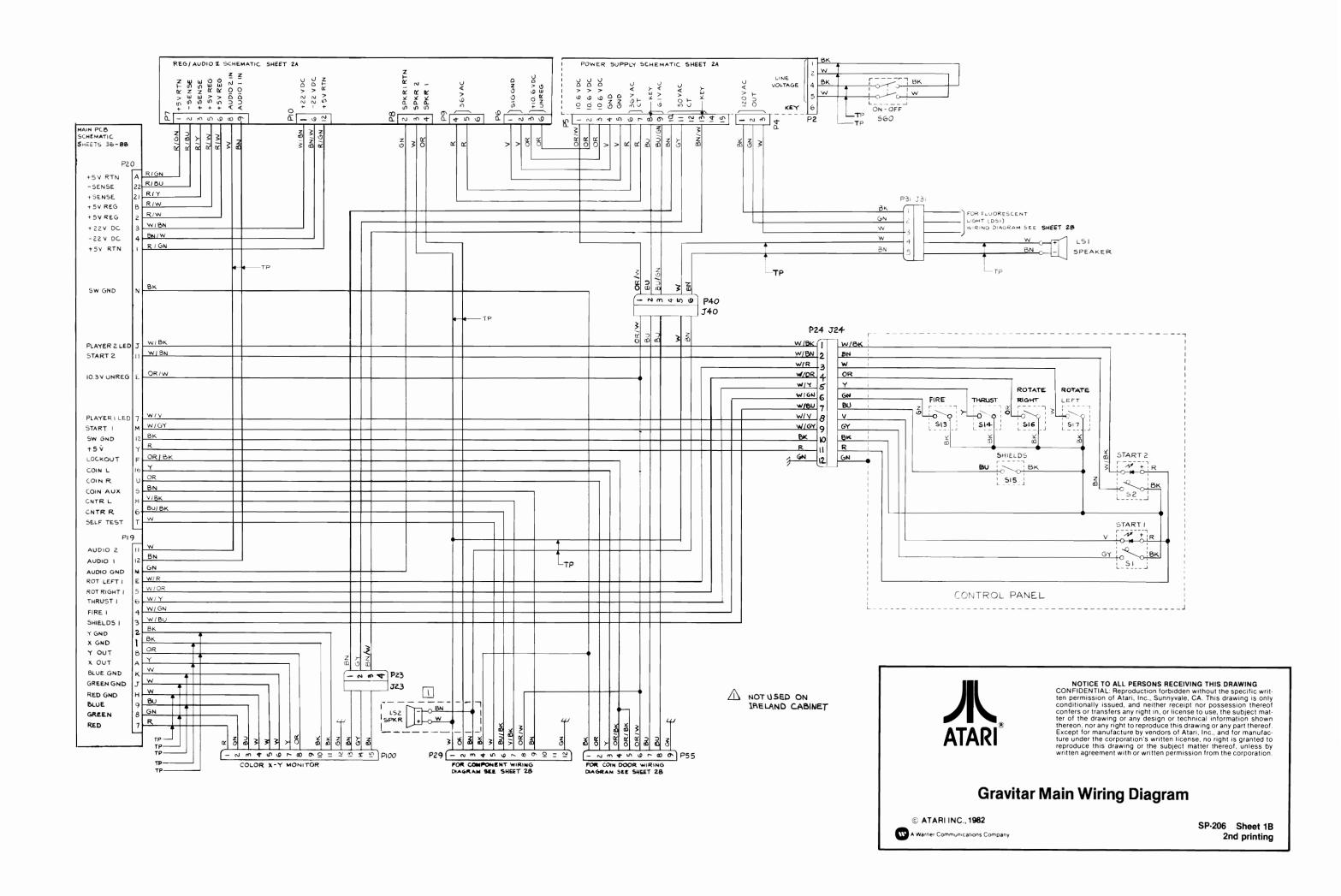

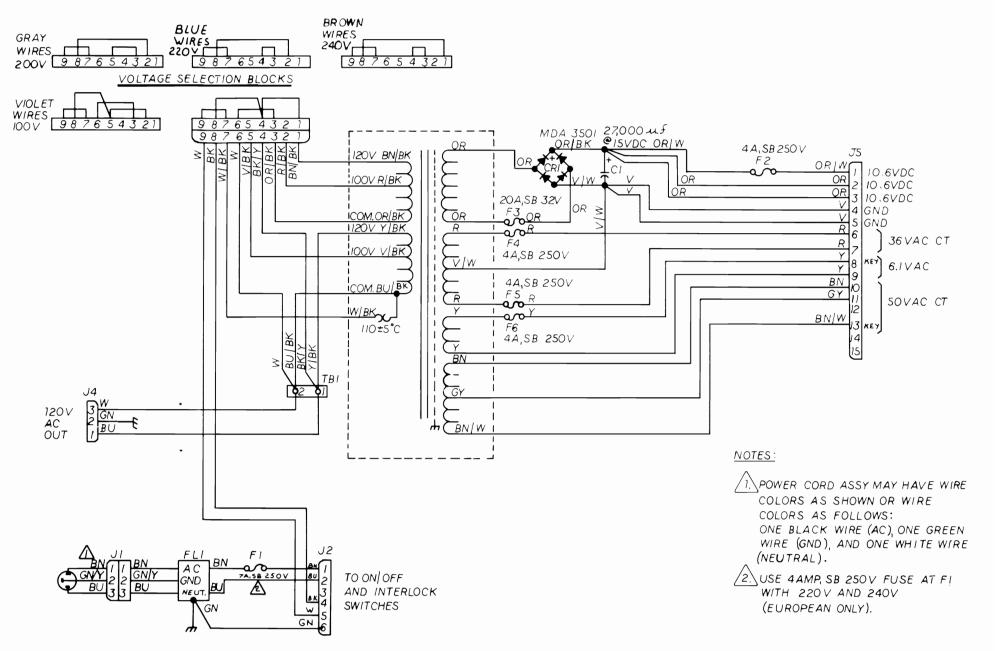

| Sheet 1B                                     | Gravitar Main Wiring Diagram (038585-01 C)                                                                                                                                                                               |

| Sheet 2A                                     | Color X-Y Power Supply Wiring Diagram (037394-01 B), Regulator/Audio II PCB Schematic Diagram (035435-02 F)                                                                                                              |

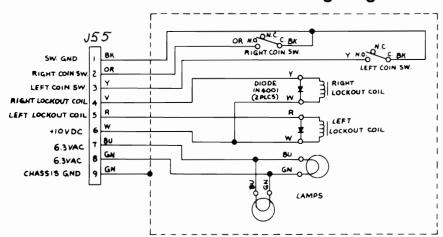

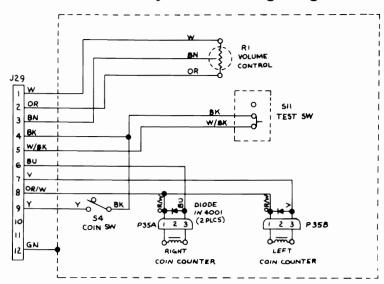

| Sheet 2B                                     | Coin-Door Wiring Diagram (037542-01 C), Utility Panel Wiring Diagram (038004-01 D), Fluorescent Light Wiring Diagram (035833-01 A)                                                                                       |

|                                              | Game PCB Schematics (038398-XX A), Sheets 3A-8B                                                                                                                                                                          |

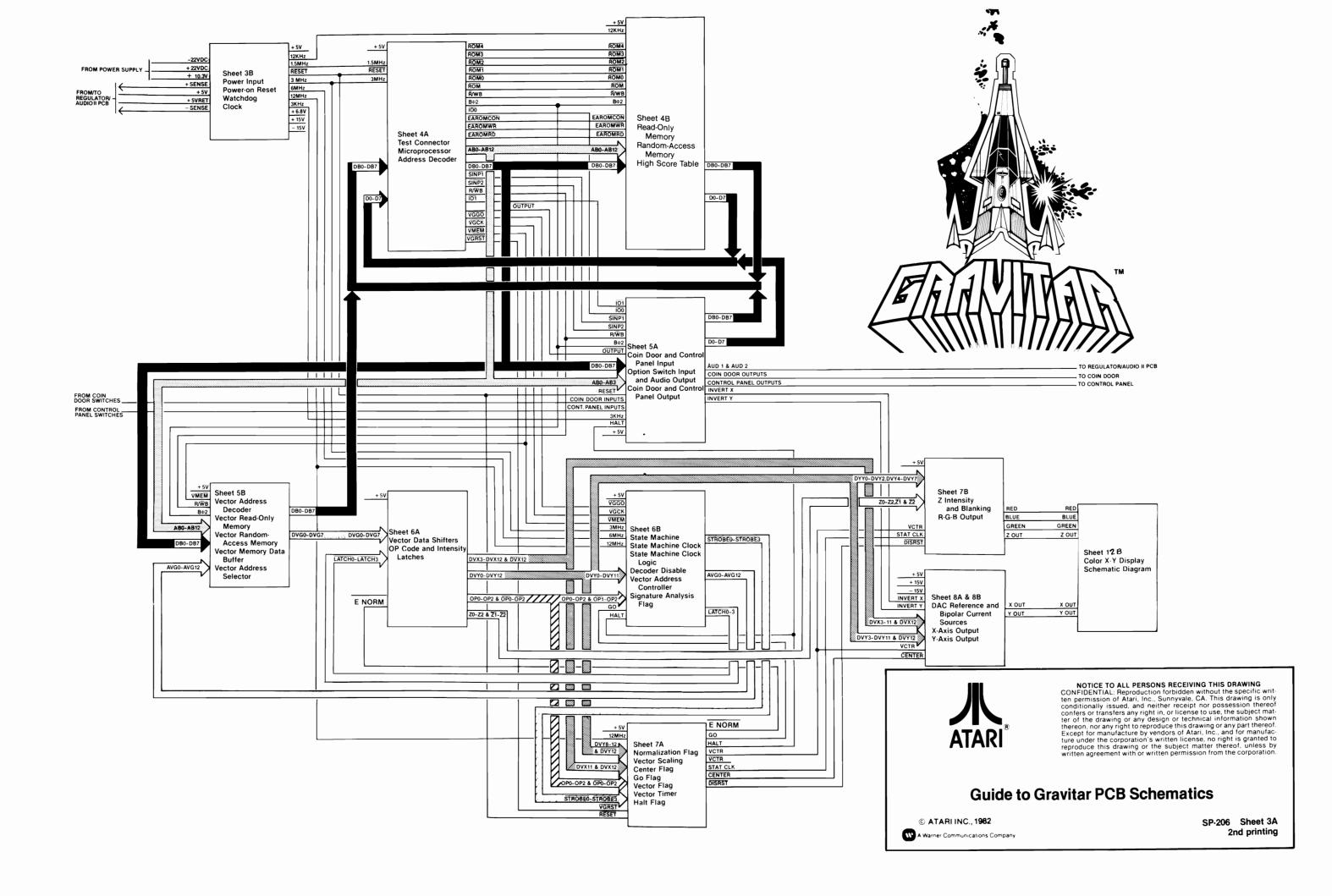

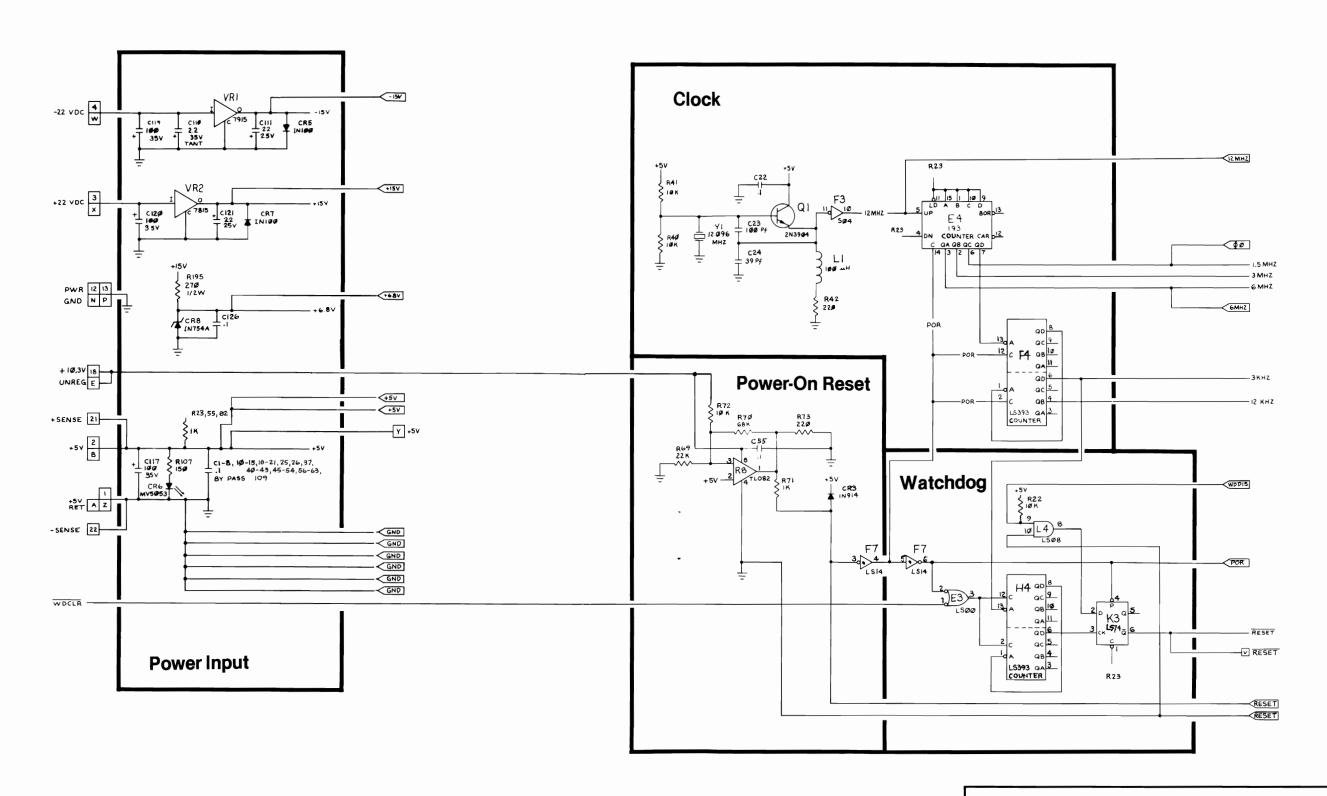

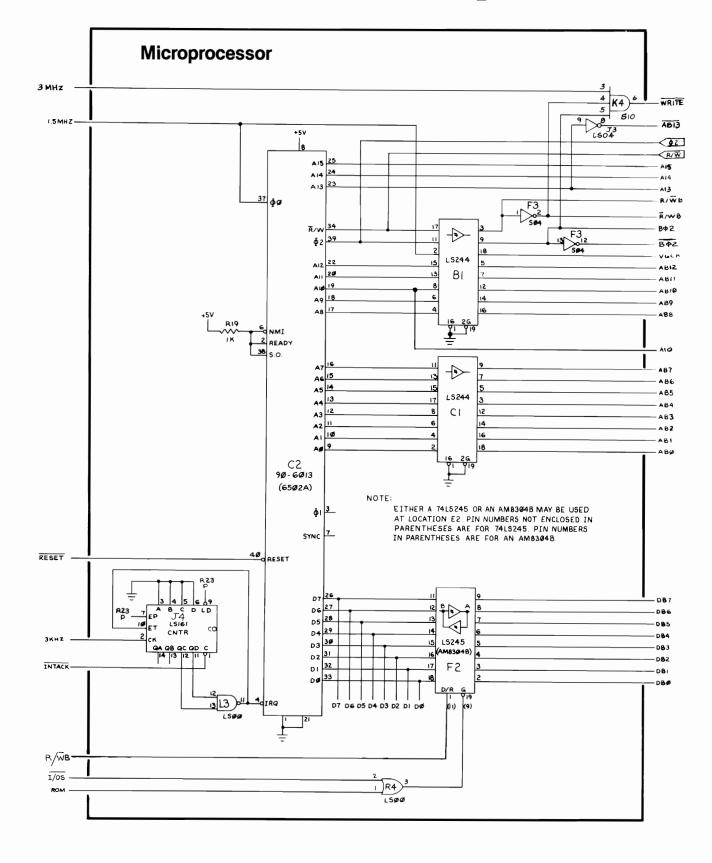

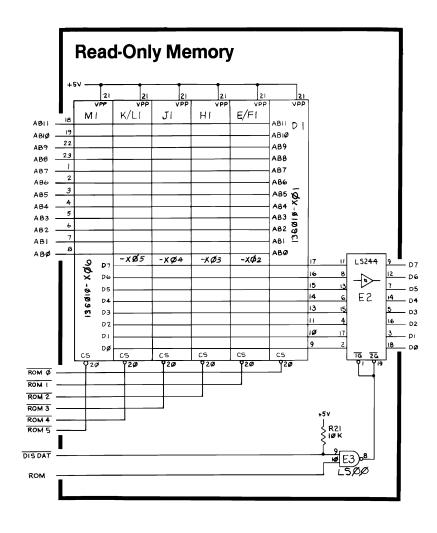

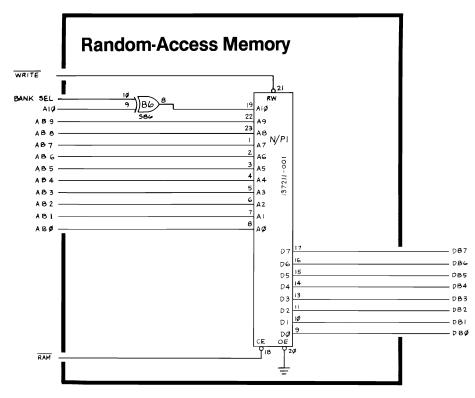

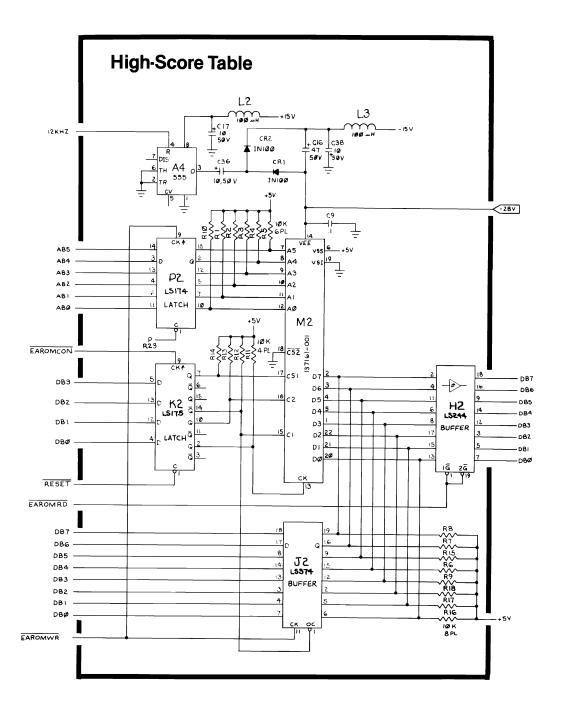

| Sheet 3A<br>Sheet 3B<br>Sheet 4A<br>Sheet 4B | Guide to Gravitar PCB Schematics (038398-XX A) Power Input, Clock, Power-On Reset, Watchdog Test Connector, Microprocessor, Timing Diagram, and Address Decoder Read-Only Memory, Random-Access Memory, High-Score Table |

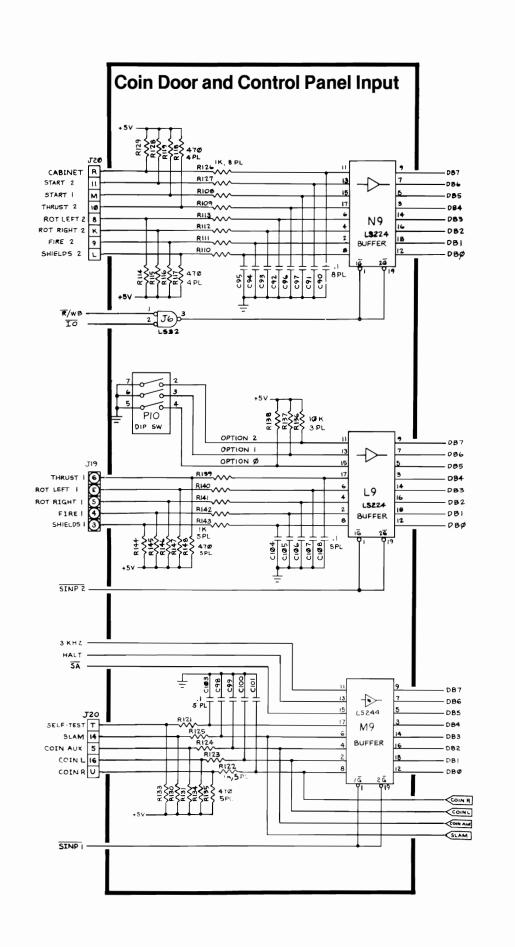

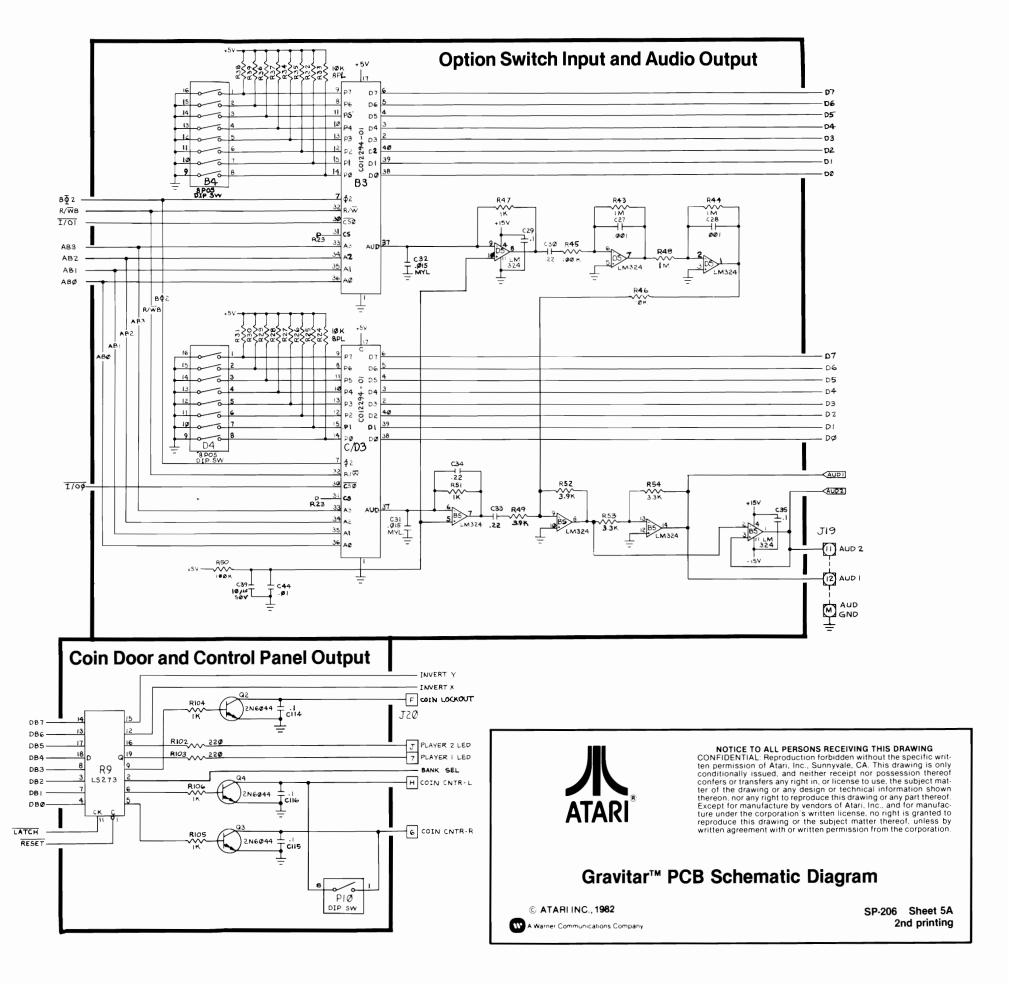

| Sheet 5A                                     | Coin Door and Control Panel Input, Option Switch Input and Audio Output, Coin Door and Control Panel Output                                                                                                              |

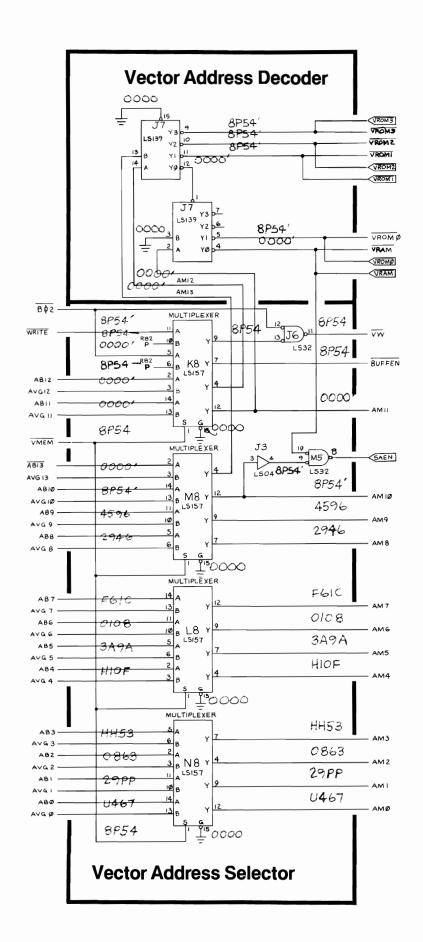

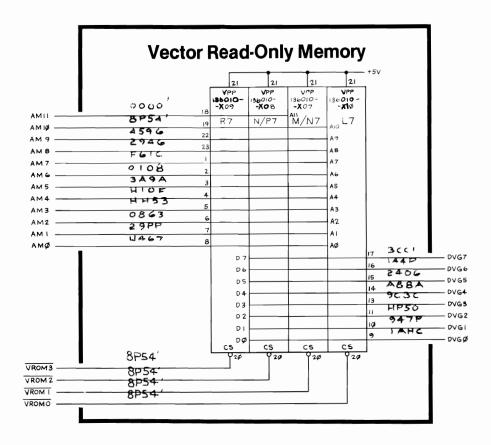

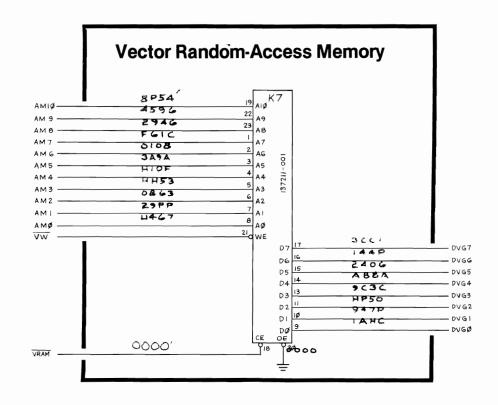

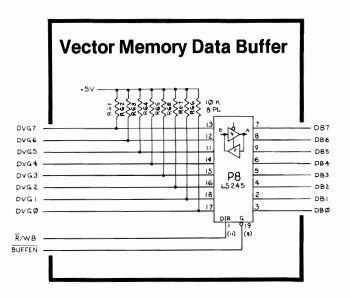

| Sheet 5B                                     | Vector Address Decoder, Vector Address Selector, Vector Read-Only Memory, Vector Random-Access Memory, Vector Memory Data Buffer                                                                                         |

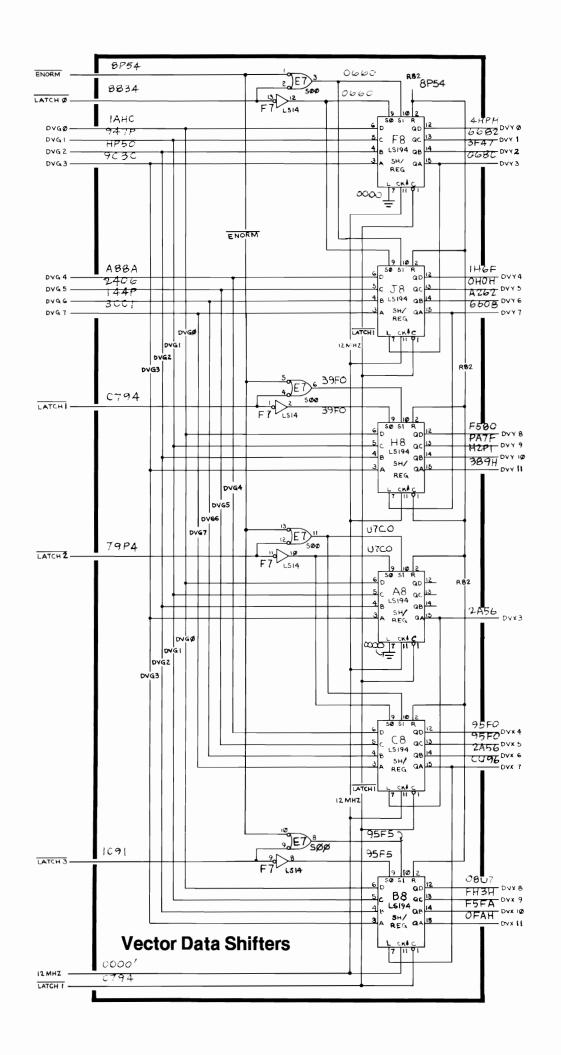

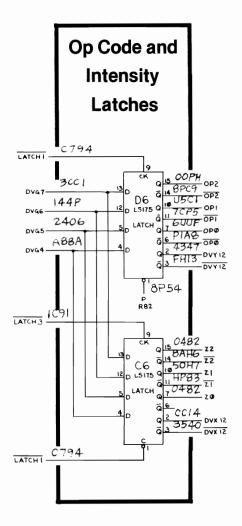

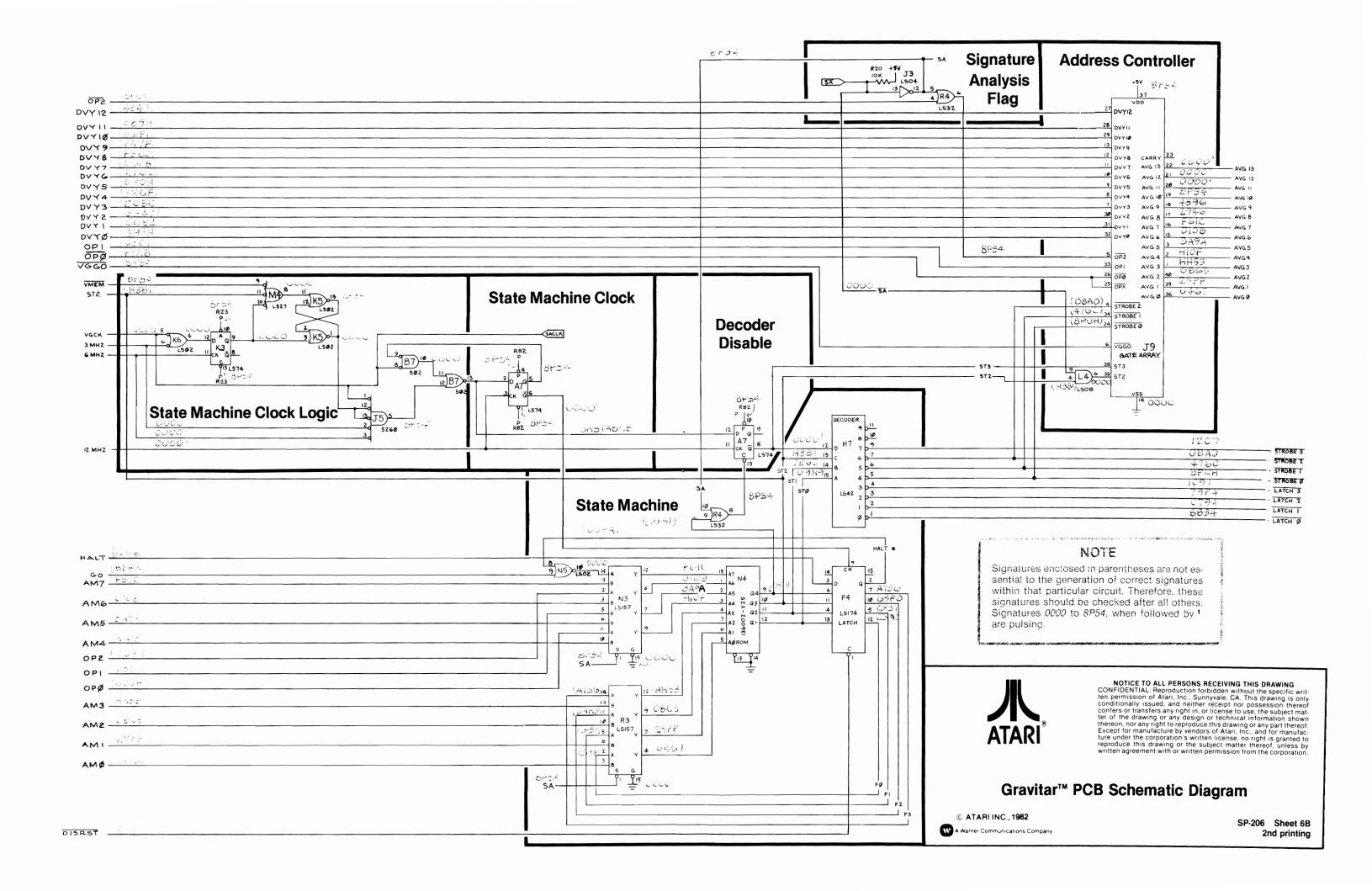

| Sheet 6A<br>Sheet 6B                         | Vector Data Shifters, Op Code and Intensity Latches State Machine Clock Logic, State Machine Clock, State Machine, Decoder Disable, Address Controller, Signature Analysis Flag                                          |

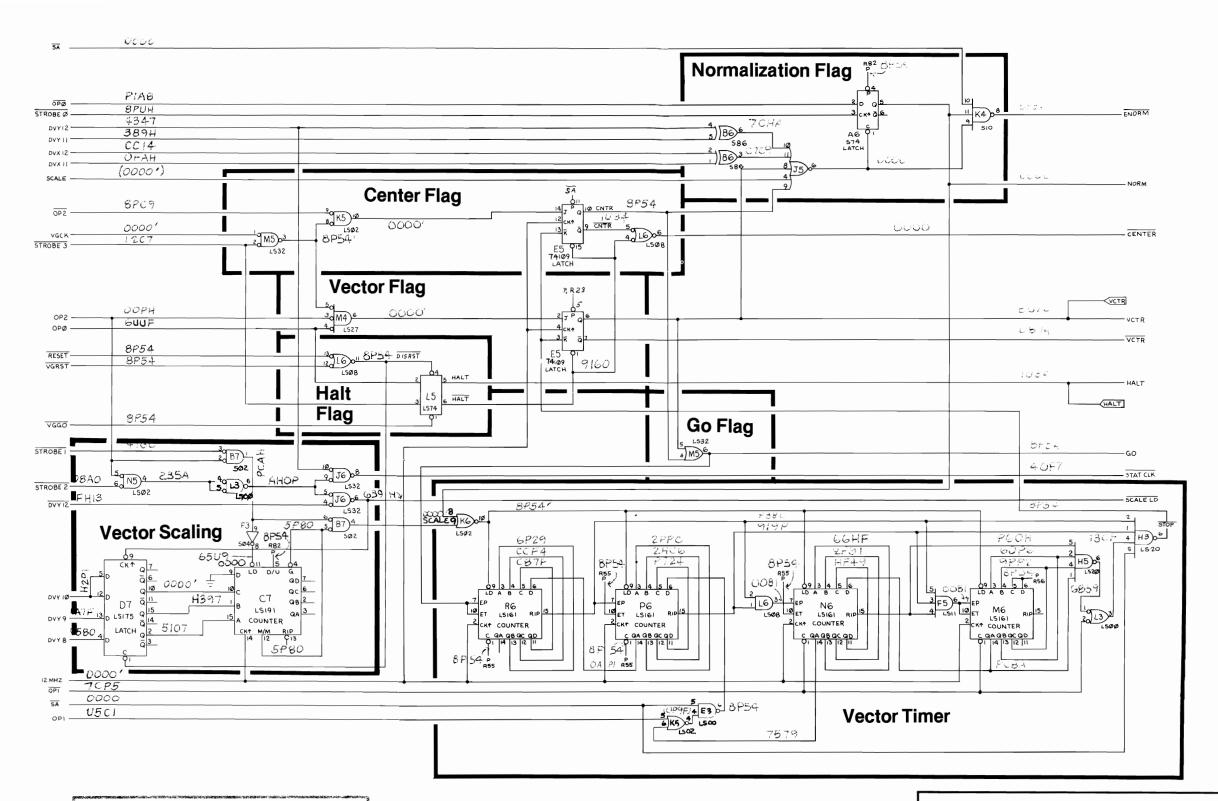

| Sheet 7A                                     | Normalization Flag, Center Flag, Vector Flag, Halt Flag, Go Flag, Vector Scaling, Vector Timer                                                                                                                           |

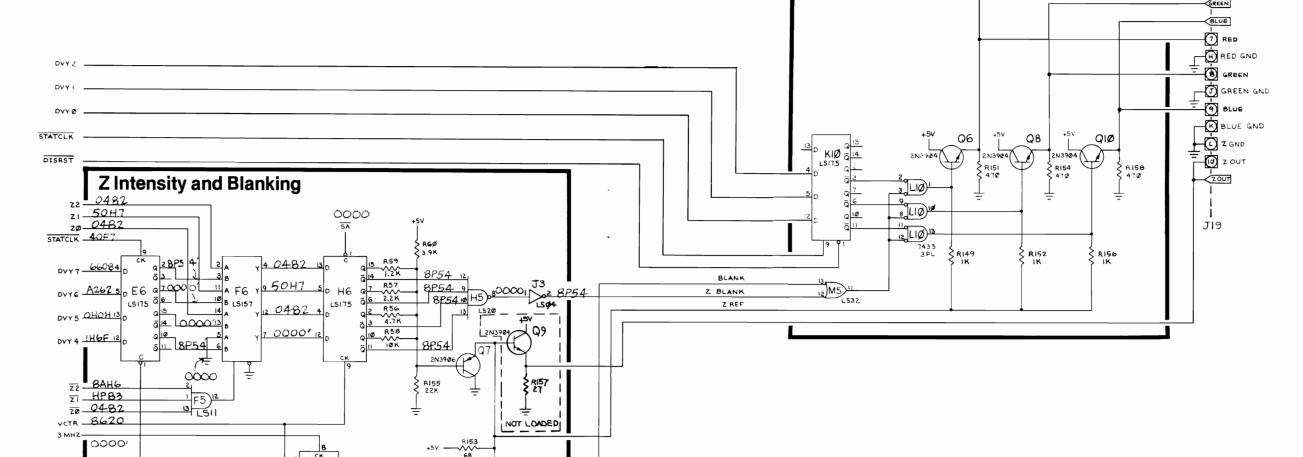

| Sheet 7B                                     | Z Intensity and Blanking, R-G-B Output                                                                                                                                                                                   |

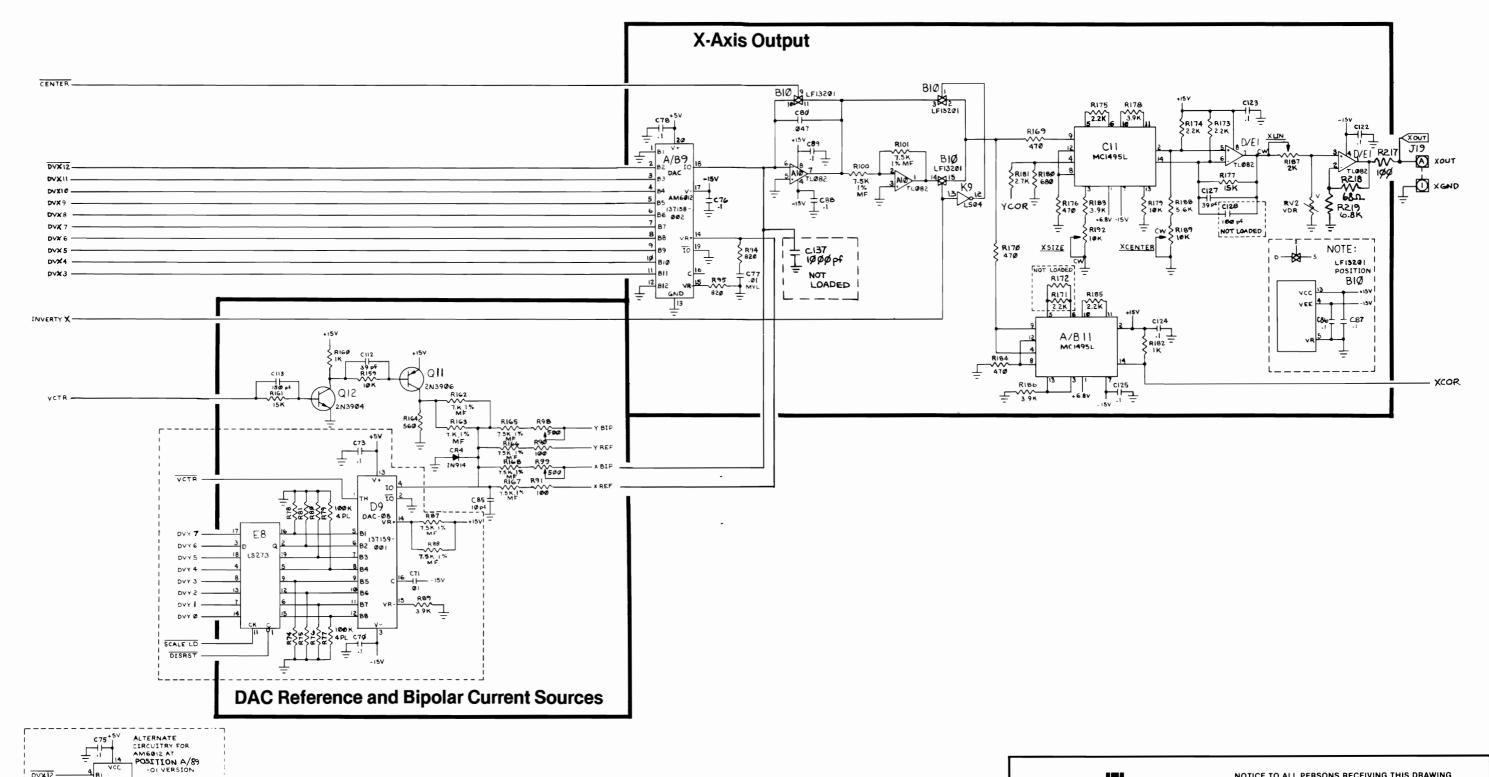

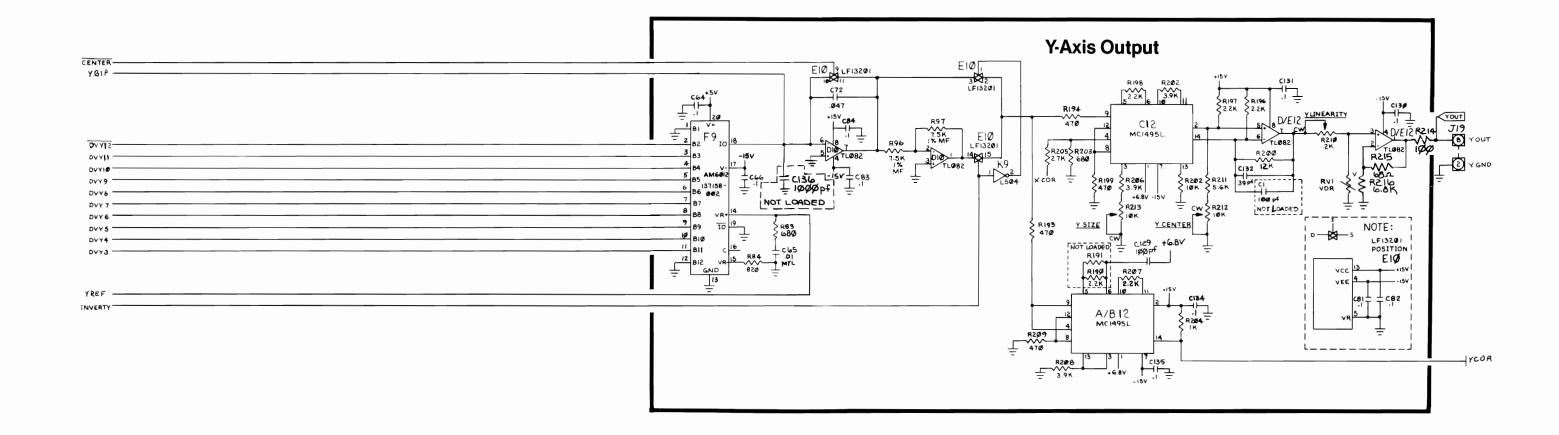

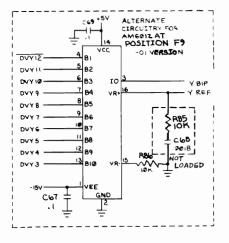

| Sheet 8A<br>Sheet 8B                         | DAC Reference and Bipolar Current Sources, X-Axis Output Y-Axis Output, Adjusting X- and Y-Axis Video Potentiometers                                                                                                     |

| Sheet on                                     | 1-Axis Output, Adjusting X- and 1-Axis video i oteritionieters                                                                                                                                                           |

| Sheet 9A<br>-10B                             | Gravitar PCB Signal Name Descriptions                                                                                                                                                                                    |

|                                              | Troubleshooting with the CAT Box:                                                                                                                                                                                        |

| Sheet 11A                                    | Gravitar Memory Map Troubleshooting with the Read/Write Controller A. CAT Box Preliminary Set-Up B. Checking the Address Lines C. Checking the Data Lines                                                                |

| Sheet 11B                                    | D. Checking the Bata Emes  D. Checking the RAM  E. Custom the Custom Audio I/O Chips  F. Checking the Player and Option Switch Inputs  G. Checking the Analog Vector-Generator                                           |

| Sheet 12A                                    | H. Checking the LED, Coin Counter, and Invert Outputs                                                                                                                                                                    |

|                                              | Troubleshooting with Signature Analysis  A. Checking the Address Lines and Address Decoders  B. Checking the Vector Generator                                                                                            |

| Sheet 12B                                    | Troubleshooting with Checksums Troubleshooting the Watchdog Circuit                                                                                                                                                      |

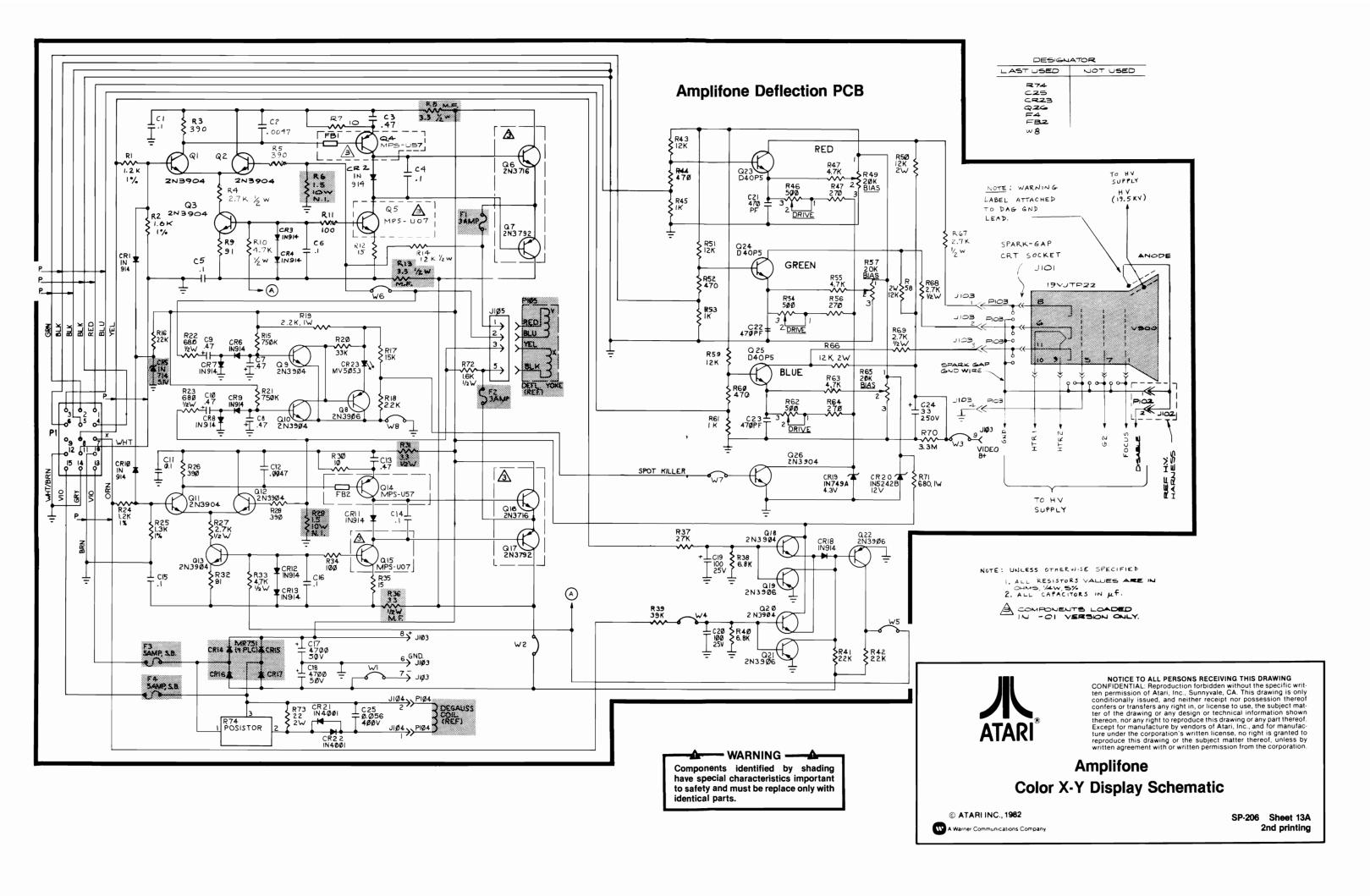

| Sheet 13A                                    | Amplifone Deflection PCB Schematic Diagram (201014-XX A)                                                                                                                                                                 |

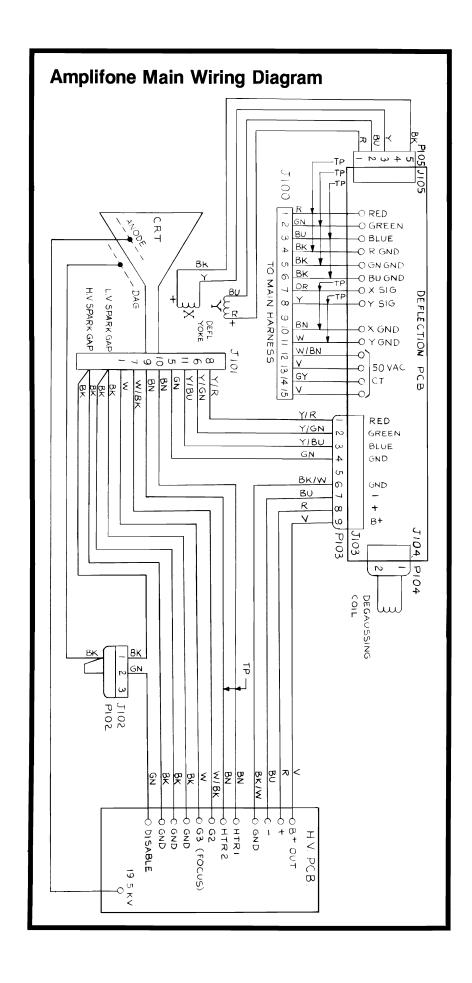

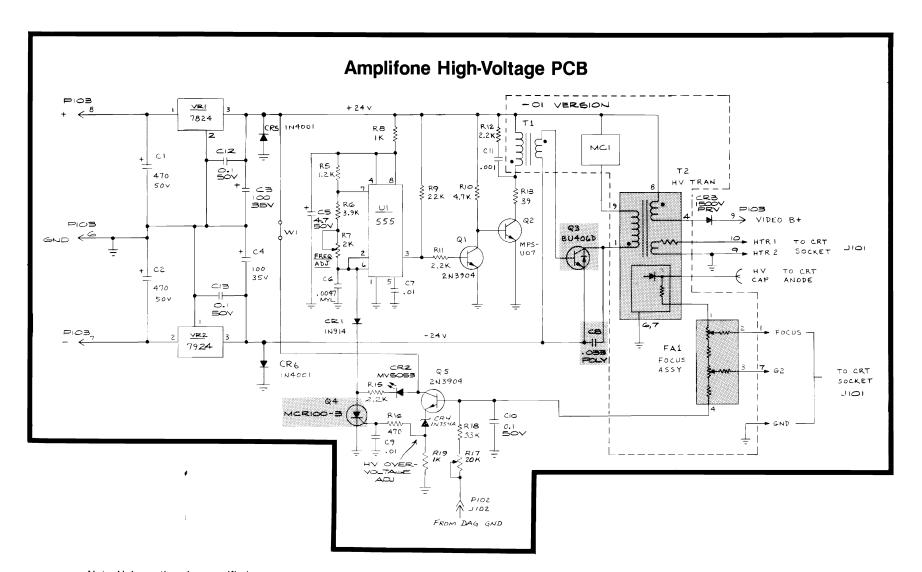

| Sheet 13B                                    | Amplifone Main Wiring Diagram (200000-01 B), Amplifone High-Voltage PCB Schematic Diagram (201012-XX A)                                                                                                                  |

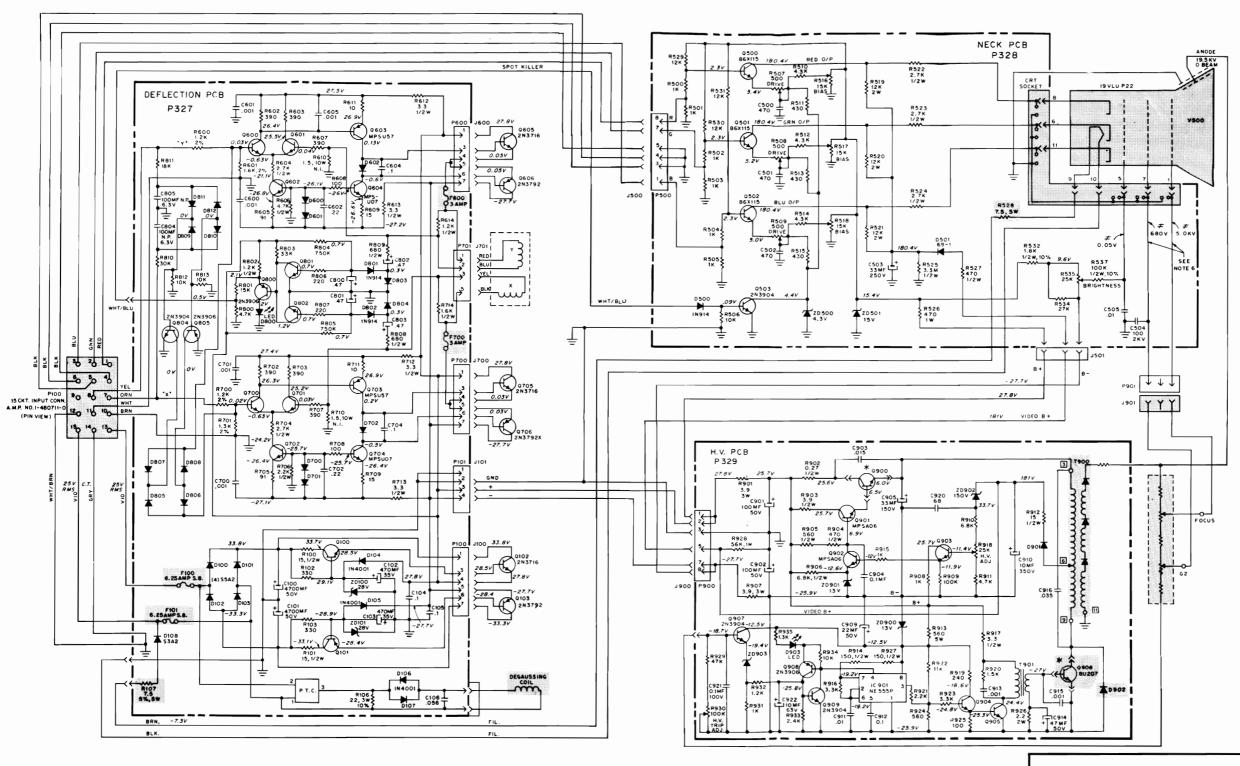

| Sheet 14A                                    | Wells-Gardner Color X-Y Display Schematic Diagram (92-053)                                                                                                                                                               |

**Schematic Package Supplement**

**Operation, Maintenance and Service Manual**

© ATARI, INC., 1982

SP-206 Sheet 1A 2nd printing

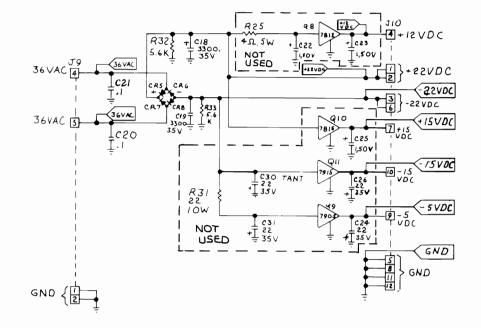

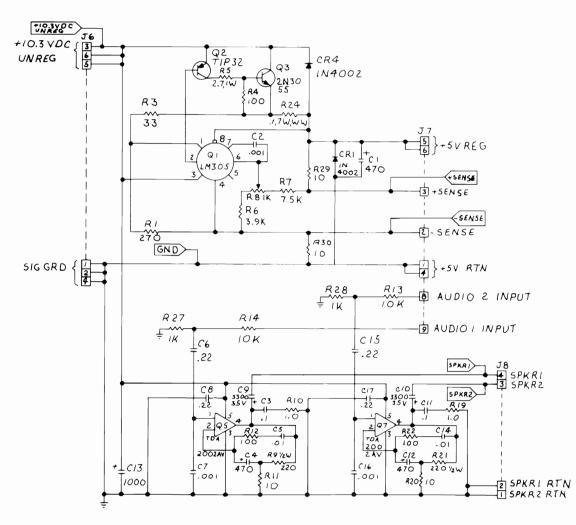

# Regulator/Audio II PCB Schematic Diagram

## **COLOR X-Y POWER SUPPLY DIAGRAM**

# NOTICE TO ALL PERSONS RECEIVING THIS DRAWING CONFIDENTIAL: Reproduction forbidden without the specific written permission of Atari, Inc., Sunnyvale, CA. This drawing is only

ten permission of Atari, Inc., Sunnyvale, CA. This drawing is only conditionally issued, and neither receipt nor possession thereof confers or transfers any right in, or license to use, the subject matter of the drawing or any design or technical information shown thereon, nor any right to reproduce this drawing or any part thereof. Except for manufacture by vendors of Atari, Inc., and for manufacture under the corporation's written license, no right is granted to reproduce this drawing or the subject matter thereof, unless by written agreement with or written permission from the corporation.

# Gravitar™ Power Supply and Reg./Audio II PCB

© ATARI INC., 1982

Warner Communications Company

SP-206 Sheet 2A 2nd printing

# **Coin Door Wiring Diagram**

# **Utility Panel Wiring Diagram**

# Fluorescent Light Wiring Diagram

NOTICE TO ALL PERSONS RECEIVING THIS DRAWING CONFIDENTIAL: Reproduction forbidden without the specific written permission of Atari, Inc., Sunnyvale, CA. This drawing is only conditionally issued, and neither receipt nor possession thereof confers or transfers any right in, or license to use, the subject matter of the drawing or any design or technical information shown thereon, nor any right to reproduce this drawing or any part thereof. Except for manufacture by vendors of Atari, Inc., and for manufacture under the corporation's written license, no right is granted to reproduce this drawing or the subject matter thereof, unless by written agreement with or written permission from the corporation.

# **Gravitar™ Game Wiring Interfaces**

© ATARI INC., 1982 A Warner Communications Company

SP-206 Sheet 2B 2nd printing

# **Test Connector**

ROMI

ROM

VMEM

I/05

1/00

RAM J

NOTICE TO ALL PERSONS RECEIVING THIS DRAWING CONFIDENTIAL: Reproduction forbidden without the specific written permission of Atari, Inc., Sunnyvale, CA. This drawing is only conditionally issued, and neither receipt nor possession thereof confers or transfers any right in, or license to use, the subject matter of the drawing or any design or technical information shown thereon, nor any right to reproduce this drawing or any part thereof. Except for manufacture by vendors of Atari, Inc., and for manufacture under the corporation's written license, no right is granted to reproduce this drawing or the subject matter thereof, unless by written agreement with or written permission from the corporation.

# Gravitar™ PCB Schematic Diagram

© ATARIINC., 1982

Warner Communications Company

SP-206 Sheet 4A 2nd printing

NOTICE TO ALL PERSONS RECEIVING THIS DRAWING CONFIDENTIAL: Reproduction forbidden without the specific written permission of Atari, Inc., Sunnyvale, CA. This drawing is only conditionally issued, and neither receipt nor possession thereof confers or transfers any right in, or license to use, the subject matter of the drawing or any design or technical information shown thereon, nor any right to reproduce this drawing or any part thereof. Except for manufacture by vendors of Atari, Inc., and for manufacture under the corporation's written license, no right is granted to reproduce this drawing or the subject matter thereof, unless by written agreement with or written permission from the corporation

# Gravitar™ PCB Schematic Diagram

© ATARI INC., 1982 A Warner Communications Company

SP-206 Sheet 4B 2nd printing

Signatures enclosed in parentheses are not essential to the generation of correct signatures within that particular circuit. Therefore, these signatures should be checked after all others. Signatures 0000 to 8P54, when followed by ' are pulsing.

NOTICE TO ALL PERSONS RECEIVING THIS DRAWING CONFIDENTIAL: Reproduction forbidden without the specific written permission of Atari, Inc., Sunnyvale, CA. This drawing is only conditionally issued, and neither receipt nor possession thereof confers or transfers any right in, or license to use, the subject matter of the drawing or any design or technical information shown thereon, nor any right to reproduce this drawing or any part thereof. Except for manufacture by vendors of Atari, Inc., and for manufacture under the corporation's written license, no right is granted to reproduce this drawing or the subject matter thereof, unless by written agreement with or written permission from the corporation.

# Gravitar™ PCB Schematic Diagram

© ATARI INC., 1982 W A Warner Communications Company

SP-206 Sheet 5B 2nd printing

Signatures enclosed in parentheses are not essential to the generation of correct signatures within that particular circuit. Therefore, these signatures should be checked after all others. Signatures 0000 to 8P54, when followed by ' are pulsing.

NOTICE TO ALL PERSONS RECEIVING THIS DRAWING CONFIDENTIAL: Reproduction forbidden without the specific written permission of Atari, Inc., Sunnyvale, CA. This drawing is only conditionally issued, and neither receipt nor possession thereof confers or transfers any right in, or license to use, the subject matter of the drawing or any design or technical information shown thereon, nor any right to reproduce this drawing or any part thereof. Except for manufacture by vendors of Atari, Inc., and for manufacture under the corporation's written license, no right is granted to reproduce this drawing or the subject matter thereof, unless by written agreement with or written permission from the corporation.

# **Gravitar™ PCB Schematic Diagram**

© ATARI INC., 1982 W A Warner Communications Company

SP-206 Sheet 6A 2nd printing

Signatures enclosed in parentheses are not essential to the generation of correct signatures within that particular circuit. Therefore, these signatures should be checked after all others. Signatures 0000 to 8P54, when followed by ' are pulsing.

NOTICE TO ALL PERSONS RECEIVING THIS DRAWING CONFIDENTIAL: Reproduction forbidden without the specific written permission of Atari, Inc., Sunnyvale, CA. This drawing is only conditionally issued, and neither receipt nor possession thereot confers or transfers any right in, or license to use, the subject matter of the drawing or any design or technical information shown thereon, nor any right to reproduce this drawing or any part thereof. Except for manufacture by vendors of Atari, Inc., and for manufacture under the corporation's written license, no right is granted to reproduce this drawing or the subject matter thereof, unless by written agreement with or written permission from the corporation.

# Gravitar™ PCB Schematic Diagram

© ATARI INC., 1982

SP-206 Sheet 7A 2nd printing

W A Warner Communications Company

Signatures enclosed in parentheses are not essential to the generation of correct signatures within that particular circuit. Therefore, these signatures should be checked after all others. Signatures 0000 to 8P54, when followed by 'are pulsing.

220 pf

AUHF

LSØ2

QG 12 2188

8P54

DISRST

**R-G-B Output**

NOTICE TO ALL PERSONS RECEIVING THIS DRAWING CONFIDENTIAL: Reproduction forbidden without the specific written permission of Atari, Inc., Sunnyvale, CA. This drawing is only conditionally issued, and neither receipt nor possession thereof confers or transfers any right in, or license to use, the subject matter of the drawing or any design or technical information shown thereon, nor any right to reproduce this drawing or any part thereof. Except for manufacture by vendors of Atari, Inc., and for manufacture under the corporation's written license, no right is granted to reproduce this drawing or the subject matter thereof, unless by written agreement with or written permission from the corporation.

# Gravitar™ PCB Schematic Diagram

© ATARI INC., 1982

A Warner Communications Company

SP-206 Sheet 7B 2nd printing

DVX12 DVXIO-DVX 9 DV**×**8 D**∨¥7** DVX6 DV**X** 5 DV**X4**

NOTICE TO ALL PERSONS RECEIVING THIS DRAWING CONFIDENTIAL: Reproduction forbidden without the specific written permission of Atari, Inc., Sunnyvale, CA. This drawing is only conditionally issued, and neither receipt nor possession thereof confers or transfers any right in, or license to use, the subject matter of the drawing or any design or technical information shown thereon, nor any right to reproduce this drawing or any part thereof. Except for manufacture by vendors of Atari, Inc., and for manufacture under the corporation's written license, no right is granted to reproduce this drawing or the subject matter thereof, unless by written agreement with or written permission from the corporation.

# Gravitar™ PCB Schematic Diagram

© ATARI INC., 1982 W A Warner Communications Company

SP-206 Sheet 8A 2nd printing

# Adjusting X- and Y-Axis Video Potentiometers

If you replace the main Gravitar PCB or the display, you may have to make the following adjustments:

- 1. Enter self-test and advance to diagonal crosshatch pattern (Screen 2).

- 2. Centering Pots: Adjust X CENTER (R189) and Y CENTER (R212) so that the crosshatch pattern is located at the middle of the screen.

- Size Pots: Adjust XSIZE (R192) and YSIZE (R213) so that the crosshatch pattern exactly covers the whole visible screen.

- 4. Linearity Pots: Adjust XLIN (R187) and YLIN (R210) so that the diagonal lines are straight. Since the LIN pots change the size of the displayed picture on the screen, you may have to readjust the SIZE pots in order to get the correct adjustment.

- Bipolar Pots: Advance to the self-test raster pattern (Screen 4). Adjust XBIP (R99) and YBIP (R98) for a 1-inch high horizontal raster in the center of the screen. Be sure the raster ends are square with the sides of the outer rectangle.

NOTICE TO ALL PERSONS RECEIVING THIS DRAWING CONFIDENTIAL: Reproduction forbidden without the specific written permission of Atari, Inc., Sunnyvale, CA. This drawing is only conditionally issued, and neither receipt nor possession thereof confers or transfers any right in, or license to use, the subject matter of the drawing or any design or technical information shown thereon, nor any right to reproduce this drawing or any part thereof. Except for manufacture by vendors of Atari, Inc., and for manufacture under the corporation's written license, no right is granted to reproduce this drawing or the subject matter thereof, unless by written agreement with or written permission from the corporation.

# Gravitar™ PCB Schematic Diagram

© ATARI INC., 1982

W A Warner Communications Company

SP-206 Sheet 8B 2nd printing

# **Descriptions of Gravitar PCB Signal Names**

#### A10, A13-A15

Address bits on Microprocessor Address Bus lines A10 and A13-A15 are generated by Microprocessor C2. Bits on lines A13-A15, together with those on AB11-AB12, are the input bits to Address Decoders R1-R2. A10 is exclusive-ORed with BANK SEL by gate B6 to produce the A10 input bit for Random-Access Memory N/P1.

#### AB0-AB12

Address bits on Buffered Microprocessor Address Bus lines AB0-AB12 are software-generated by Microprocessor C2 and buffered by B1 and C1. These signals are the input bits to Read-Only Memories D1, E/F1, H1, J1, K/L1, and M1; and to Random-Access Memory N/P1.

Address bits AB6-AB8 are the select input signals for Address Decoder P3.

Address bits AB11-AB12 and A13-A15 are the input bits for Address Decoders R1 and R2.

Address bits AB0-AB13 are applied with bits from AVG0-AVG12 to Vector Address Selectors K8, M8, L8, and N8 to produce the data on lines AM0-AM12.

Bits AB0-AB3 are control signals to custom audio chips B3 and C/D3 in the Option Switch Input and Audio Output circuit.

Bits AB0-AB5 are the input signals to latch P2 in the High-Score Table circuit where they are used to produce the A1-A5 address input for EAROM M2.

#### AB<sub>13</sub>

AB13 is from AB13, inverted by J3, and applied to Vector Address Selector M8. When VMEM is low, AB13 and AB12 select the specific Vector Memory Read-Only Memory.

#### AMO-AM13

Address bits on Multiplexed Address Bus lines AM0-AM13 are software-generated by Vector Address Selectors K8, L8, M8, and N8. When VMEM is low, the Multiplexed Address Bus is from Buffered Microprocessor Address Bus AB0 through AB12 and AB13. When VMEM is high, AM0-AM12 is from Vector-Generator Address Bus lines AVG0-AVG13.

Signals AM0-AM11 are the input address signals to Vector Read-Only Memories L7, M/N7, N/P7, R7 and to Vector Random-Access Memory K7. In addition, AM11-AM13 are the select input signals for Vector Address Decoder J7. AM0-AM7 are input signals for multiplexers N3 and R3 of the State Machine circuit.

#### **AUD 1-AUD 2**

The Audio 1 and Audio 2 signals are game PCB output signals that are generated by custom audio chips B3 and C/D3 of the Option Switch Input and Audio Output circuit. AUD 1 is the inverse of AUD 2. These signals are applied to the Audio/Regulator II PCB and ultimately drive speakers 1 and 2.

#### AVG0-AVG13

Address bits on Vector-Generator Address Bus lines AVG0-AVG13 are software-generated by Vector Address Controller J9. When VMEM is high, these signals are passed through the Vector Address Selectors on lines AM0-AM13 to the Vector Read-Only Memory and the Vector Random-Access Memory.

#### **BANK SEL**

The Bank Select signal is developed from data on line DB2. When latch R9 of the Coin Door and Control Panel Output circuit is clocked by LATCH, R9 latches the data on DB2 to pin 2 of R9, producing the BANK SEL signal. BANK SEL is exclusive-ORed with the address bit A10 by gate B6 to produce input address bit A10 for Random-Access Memory N/P1.

#### BLANK

Blank is an active high-level signal generated by counter M3 in the Z Intensity and Blanking circuit and ORed with Z BLANK by gate M5 of the R-G-B Output circuit. When high, BLANK turns off transistors Q6, Q8, and Q10, which kills the RED, GREEN, and BLUE output signals to the display.

#### BLUE

Blue is a game PCB output signal developed from the data on line DVY0. When the data bit on DVY0 is high and latch K10 of the R-G-B Output circuit is clocked by STATCLK, the data on DVY0 is inverted and latched to pin 11 of K10. If both BLANK and Z BLANK are low, this data bit is again inverted by gate L10 to turn on Q10. Transistor Q10 generates the BLUE signal for the display.

#### BUFFEN

Buffer Enable is an active low-level signal developed from \$\overline{B\phi2}\$ by Vector Address Selector K8. \$\overline{BUFFEN}\$ is the enable input signal for Vector Memory Data Buffer P8. When low, \$\overline{BUFFEN}\$ allows P8 to pass data.

#### **B**Φ2

The active high-level Phase 2 Clock signal is hardware-generated from the internal clock circuitry of Microprocessor C2, buffered by B1, and applied to AND gate K4. Gate K4 ANDs together B $\Phi$ 2,  $\overline{R}$ /WB, and 3 MHz to produce  $\overline{WRITE}$ . B $\Phi$ 2 is also used as the clock signal for custom audio chips B3 and C/D3 of the Option Switch Input and Audio Output circuit.

#### **B**Φ2

The active low-level Phase 2 Clock signal is generated at pin 12 of F3 by inverting BΦ2. BΦ2 is applied to Vector Address Selector K8 to produce BUFFEN.

#### CENTER

Center is an active-low level signal software-generated by gating CNTR with HALT by Center Flag gate L6. When low, CENTER closes switches E10 of the Y-Axis Output circuit and B10 of the X-Axis Output circuit to center the beam on the display.

#### CNTR

The active high-level Center Flag signal is software-generated by latch E5 of the Center Flag circuit. CNTR is set high when VGCK, STROBE3, and OP2 are low CNTR is applied to gate J5 of the Normalization Flag circuit to develop the clear signal for latch A6. CNTR is ORed with VCTR by GO Flag gate M5 to generate the GO signal.

#### CNTR

The active low-level Center Flag signal is software-generated by latch E5 of the Center Flag circuit. When clocked by the 12-MHZ signal, E5 latches STOP to pin 9 to produce CNTR. CNTR is gated with HALT by Center Flag gate L6 to generate CENTER.

#### COIN CNTR-L

Coin Counter Left is a game PCB output signal developed from the data bit on line DB1. When clocked by LATCH, latch R9 of the Coin Door and Control Panel Output circuit latches the data bit on DB1 to pin 6 of R9. From here, the signal is current amplified and inverted by Q4 and applied to the game Utility Panel to activate the Left Coin Counter.

#### COIN CNTR-R

Coin Counter Right is a game PCB output signal developed from the data bit on line DB0. When clocked by LATCH, latch R9 of the Coin Door and Control Panel Output circuit latches the data bit on DB0 to pin 5 of R9. From here, the signal is current amplified and inverted by Q3 and applied to the game Utility Panel to activate the Right Coin Counter.

#### COIN LOCKOUT

Coin Lockout is a game PCB output signal developed from the data on line DB3. When clocked by LATCH, latch R9 of the Coin Door and Control Panel Output circuit latches the data bit on DB3 to pin 9 of R9. From here, the signal is current amplified and inverted by Q2 and applied to the Right and Left Lockout Coils of the game Coin Door.

#### D0-D7

Microprocessor Data Bus lines D0-D7 form a bi-directional data bus between the Microprocessor, the Read-Only Memory, and the Option Switch Input circuits.

#### DRC DR7

Buffered Microprocessor Data Bus lines DB0-DB7 form a buffered bi-directional data bus between microprocessor data-bus buffer F2 and Vector Memory Data Buffer P8; Coin-Door and Control Panel Input circuit buffers L9, M9, and N9; High-Score Table latches K2 and J2; and High-Score Table buffer H2.

#### DIS DAT

Disable Data is an active <u>low-level</u> signal generated by test equipment connected to the <u>DIS DAT</u> test point. <u>DIS DAT</u> is ANDed with the ROM signal by gate E3 to produce the enable signal for buffer E2 of the Read-Only Memory circuit. When enabled, buffer E2 passes data from the selected Read-Only Memory to the Microprocessor Data Bus.

#### DISRST

Display Reset is an active low-level signal software-generated by gate L6 of the Halt Flag circuit. When either RESET or VGRST is low, DISRST is set low When low, DISRST clears State Machine latch P4, DAC Reference and Bipolar Current Sources latch E8, R-G-B Output latch K10, Vector Scaling latch D7, Z Intensity and Blanking latch E6 and counter M3. In addition, DISRST presets the HALT signal from latch L5 to the high level.

#### DVG0-DVG7

Data bits on Vector-Generator Data Bus lines DVG0-DVG7 are software-generated by the selected Vector Read-Only Memory or Vector Random-Access Memory. If Vector Memory Data Buffer P8 is enabled (BUFFEN is low) and the R/WB line is low, the data on lines DVG0-DVG7 is passed through P8 to the Buffered Microprocessor Data Bus to be read by the microprocessor. Otherwise, the data on DVG0-DVG7 is sent to the Vector Data Shifters and to the Op Code and Intensity Latches.

#### DVX3-DVX12, DVX12

Data bits on X-Axis Vector Data lines DVX3-DVX12 and  $\overline{DVX12}$  are software-generated by Vector Data Shifters A8, B8, C8, and by latch C6 of the Op Code and Intensity Latches circuit. DVX3-DVX11 and  $\overline{DVX12}$  are the input signals to digital-to-analog converter (DAC) A/B9 of the X-Axis Output circuit. The data carried on these lines represents the X-axis change from the current location of the display beam. If  $\overline{DVX12}$  is low, DAC A/B9 operates only in its

lower 512 positions, which means a negative direction of change on the display. If DVX12 is high, DAC A/B9 operates only in its upper 512 positions for a positive direction of change on the display.

In addition, DVX11 and DVX12 are exclusive-ORed by gate B6 of the Normalization Flag circuit.

#### DVY0-DVY12, DVY12

Data bits on Y-Axis Vector Data lines DVY0-DVY12 and DVY12 are software-generated by Vector Data Shifters F8, H8, J8, and by latch D6 of the Op Code and Intensity Latches circuit. DVY3-DVY11 and DVY12 are the input signals for digital-to-analog converter (DAC) F9 of the Y-Axis Output circuit. The data carried on these lines represents the Y-axis change from the current location of the display beam. If DVY12 is low, DAC F9 operates only in its lower 512 positions, which means a negative direction of change on the display. If DVY12 is high, DAC F9 operates only in its upper 512 positions for a positive direction of change on the display.

In addition, DVY0-DVY7 are applied to latch E8 in the DAC Reference and Bipolar <u>Current Sources circuit</u>. These signals, together with VCTR and <u>VCTR</u>, set the X REF and Y REF voltage levels (via DAC D9).

Lines DVY0-DVY2 carry data representing the eight different color signals for latch K10 of the R-G-B Output circuit.

Lines DVY4-DVY7 carry data representing the Z-intensity signals for latch E6 of the Z Intensity and Blanking circuit.

Data on DVY8-DVY10 are applied to latch D7 of the Vector Scaling circuit. The data carried on these lines represents the number (in binary) that the Vector Scaling circuit uses to divide into the vector drawing time. The vector drawing time n is divided by 2, where n equals the number represented on DVY8-DVY10.

In addition, DVY11 and DVY12 are exclusive-ORed by gate B6 of the Normalization Flag circuit.

#### EAROMCON

The Electrically-Alterable ROM Control signal is an active low-level signal software-generated by Address Decoder P3 at address 8900. EAROMCON is the clock signal for latch K2 in the High-Score Table circuit. EAROMCON allows K2 to pass data bits on lines DB0-DB3 to the control lines of EAROM M2.

#### FAROMRD

The Electrically-Alterable ROM Read Enable is an active low-level signal software-generated by Address Decoder R2 at address 7000. EAROMRD is the read-enable signal for buffer H2 of the High-Score Table circuit. EAROMRD allows the eight data bits from EAROM M2 to be passed through buffer H2 to the microprocessor data bus.

### **EAROMWR**

The Electrically-Alterable ROM Write Enable is an active low-level signal software-generated by Address Decoder P3 at address 8940. EAROMWR is the clock signal for latches J2 and P2 in the High-Score Table circuit. EAROMWR allows address bits on lines AB0-AB5 and data bits on lines DB0-DB7 to pass to the address and data input pins of EAROM M2.

NOTICE TO ALL PERSONS RECEIVING THIS DRAWING CONFIDENTIAL: Reproduction forbidden without the specific writen permission of Atari, Inc., Sunnyvale, CA. This drawing is only conditionally issued, and neither receipt nor possession thereof confers or transfers any right in, or license to use, the subject matter of the drawing or any design or technical information shown thereon, nor any right to reproduce this drawing or any part thereof. Except for manufacture by vendors of Atari, Inc., and for manufacture under the corporation's written license, no right is granted to reproduce this drawing or the subject matter thereof, unless by written agreement with or written permission from the corporation.

**Gravitar™ PCB Signal Name Descriptions**

© ATARI INC., 1982

SP-206 Sheet 9A 2nd printing

W A Warner Communications Company

# Description of Gravitar PCB Signal Names (continued)

#### **ENORM**

The active low-level Normalization Flag is software-generated by gate K4 of the Normalization Flag circuit. If OPO is high, SA is high, and the output from gate J5 is high, ENORM is set low when STROBEO goes high. ENORM is applied through gate E7 to the S1 input pins of Vector Data Shifters A8, B8, C8, F8, H8, and J8. ENORM multiples the rate of change of the X and Y vector data in the Vector Data Shifters (via shift left operations) at the same 2 factor specified by data on lines DVY8-DVY10. The n number is incremented at a 12-MHz rate until either DVX11 or DVY11 changes state, which then sets ENORM to the high level.

#### GO

The Go flag is an active high-level signal software-generated by gate M5 of the Go Flag circuit when either VCTR or CNTR are high. GO is gated with HALT\* by gate N5 of the State Machine circuit to produce the A7 input address bit for State Machine ROM N4.

GO is also used as the enable signal for Vector Timer R6. When GO is high, the Vector Timer starts its count. The Vector Timer counts to 256 if OP1 is high and OP1 is low If OP1 is low and OP1 is high, the Vector Timer counts to 16K.

#### **GREEN**

Green is a game PCB output signal developed from the data on line DVY1 in the R-G-B <u>Output</u> circuit. When DVY1 is high and latch K10 is clocked by STATCLK, the data bit on DVY1 is inverted and latched to pin 6 of K10. If both BLANK and Z BLANK are low, this data bit is again inverted by gate L10 to turn on Q8. Transistor Q8 generates the GREEN signal for the display.

#### HALT

The active high-level Halt Flag is software-generated by latch L5 of the Halt Flag circuit. HALT is applied through <u>buffer</u> M9 of the Coin Door and Control Panel Input circuit (when SINP1 is low) to permit Microprocessor C2 to read the status of HALT on line DB6. In addition, HALT is applied to latch P4 of the State Machine circuit to develop HALT\*.

#### HALT\*

The active high-level Delayed Halt Flag is software-generated by latch P4 of the State Machine circuit. HALT\* is generated when the HALT signal has been delayed by one pulse of inverted VGCK (1.5 MHz), which in turn has been delayed by one pulse of 12 MHz. HALT\* is ORed with GO by gate N5 of the State Machine circuit to produce the A7 input address bit for State Machine ROM N4.

#### HAL

The active low-level Halt Flag is software-generated by latch L5 of the Halt Flag circuit. HALT is the clear signal for Vector Flag latch E5 and Center Flag latch E5. In addition, HALT is ORed with CNTR by gate L6 of the Center Flag circuit to produce CENTER.

#### INTACK

Interrupt Acknowledge is an active low-level signal softwaregenerated from Address Decoder P3 at address 88C0. This signal is an acknowledgment from Microprocessor C2 that an interrupt request has been received. INTACK resets counter J4.

#### INVERT X

Invert X is an active high-level signal developed from the data bit on line DB6. When clocked by LATCH, latch R9 of the Coin Door and Control Panel Output circuit latches the data bit on DB6 to pin 12 of R9. When high, INVERT X closes switch B10 through inverter K9 in the X-Axis Output circuit. This inverts the X-axis vector instruction to the display.

#### INVERT Y

Invert Y is an active high-level signal developed from the data bit on line DB7. When clocked by LATCH, latch R9 of the Coin Door and Control Panel Output circuit latches DB7 to pin 15 of R9. When high, INVERT Y closes switch E10 through inverter K9 in the Y-Axis Output circuit. This inverts the Y-axis vector instruction to the display.

#### īō

The Input/Output signal is an active low-level signal software-generated by Address Decoder R2 during addresses 8000 through 8FFF.  $\overline{\text{IO}}$  is gated with  $\overline{\text{R}}/\text{WB}$  by gate J6 to produce the direction signal for bi-directional data buffer N9 of the Coin Door and Control Panel Input circuit.  $\overline{\text{IO}}$  determines the direction of data flow through buffer N9.

#### I/OS

$\overline{I/OS}$  is an active high-level signal software-generated from Address Decoder R2 during addresses 6000 through 6FFF. The  $\overline{I/OS}$  signal is ORed with the ROM signal by gate R4 to enable bi-directional data bus buffer F2 to pass data. When  $\overline{I/OS}$  is high, data buffer F2 is turned off, which allows custom audio chips B3 and C/D3 to pass data to the data bus.

#### 1/00

$\overline{I/OO}$  is an active low-level signal software-generated by Address Decoder R2 at address 6800.  $\overline{I/OO}$  is the chip-select enable for custom audio chip C/D3 in the Option Switch Input and Audio Output circuit.

#### 1/01

1/O1 is an active low-level signal software-generated by Address Decoder R2 at address 6000. 1/O1 is the chip-select enable for custom audio chip B3 in the Option Switch Input and Audio Output circuit.

#### LATCH

Latch is an active low-level signal generated by Address Decoder P3 at address 8800. LATCH is the clock signal for latch R9 in the Coin Door and Control Panel Output circuit. When low, LATCH allows the data bits on lines DB0-DB7 to pass through R9.

#### LATCHO

Latch 0 is an active low-level signal <u>software-generated</u> by decoder H7 of the State Machine circuit. <u>LATCH0</u> is applied through inverter F7 to the S0 input <u>pins of shift</u> registers F8 and J8 in the Vector Data Shifters circuit. <u>LATCH0</u> causes the data bits on lines DVG0-DVG7 to be latched by F8 and J8 to lines DVY0-DVY7 when F8 and J8 are clocked by the 12-MHz clock signal.

#### LATCH<sup>\*</sup>

Latch 1 is an active low-level signal <u>software-generated</u> by decoder H7 of the State Machine circuit. <u>LATCH1</u> is applied through inverter F7 to the S0 <u>input pin</u> of shift register H8 in the Vector Data Shifters circuit. <u>LATCH1</u> causes the data bits on lines DVG0-DVG3 to be latched by H8 to lines DVY8-DVY10 when H8 is clocked by the 12-MHz clock signal.

LATCH1 is also the clear signal for Vector Data Shifters A8, B8, C8, F8, J8, and for Op Code and Intensity Latch C6.

In addition, <u>LATCH1</u> is the clock signal for Op Code and Intensity Latch D6. When <u>LATCH1</u> goes low, the data bits on lines DVG4-DVG7 are latched by D6 to lines OP0-OP2, <u>OP0-OP2</u>, DVY12, and DVV12

#### LATCH2

Latch 2 is an active low-level signal software-generated by decoder H7 of the State Machine circuit. LATCH2 is applied through inverter F7 to the S0 input pins of shift registers A8 and C8 in the Vector Data Shifters circuit. LATCH2 causes the data bits on lines DVG0-DVG7 to be latched by A8 and C8 to lines DVX3-DVX7 when A8 is clocked by the 12-MHz clock signal.

#### LATCH3

Latch 3 is an active low-level signal software-generated by decoder H7 of the State Machine circuit. LATCH3 is applied through inverter F7 to the S0 input pin of shift register B8 in the Vector Data Shifters circuit. LATCH3 causes the data bits on lines DVG0-DVG3 to be latched by B8 to lines DVX8-DVX11 when B8 is clocked by the 12-MHz clock signal.

LATCH3 is also the clock signal for Op Code and Intensity Latch C6. When LATCH3 goes low, the data bits on lines DVG4-DVG7 are latched by C6 to lines Z0-Z2, Z1-Z2, DVX12, and DVX12.

#### NORM

The active high-level Normalization Flag is software-generated by latch A6 in the Normalization Flag circuit. If  $\overline{OP0}$  is high, NORM is set high when  $\overline{STROBE0}$  goes high. NORM is gated with SCALE by gate K5 in the Vector Timer circuit to produce the load-enable signal for Vector Timers M6, N6, P6, and R6. If the Vector Timers are enabled, NORM initiates the divide-by-2<sup>n</sup> operation of the vector drawing time. (The n factor is specified by the data on lines DVY8-DVY10 to Vector Scaling latch D7.)

#### **OPTION 0-OPTION 2**

The Option 0, Option 1, and Option 2 signals are hardware-generated by DIP switch P10. They are applied to switch input buffer L9 of the Coin Door and Control Panel Input circuit. When L9 is enabled by SINP2, OPTION 0-OPTION 2 are passed to Buffered Microprocessor Data Bus lines DB5-DB7.

#### OPO

The Op Code 0 signal is software-generated by latch D6 in the Op Code and Intensity Latches circuit. If the data on line DVG5 is high, OP0 is set high when D6 is clocked by LATCH1. OP0 is multiplexed with AM4 by N3 in the State Machine circuit to produce the A4 input address bit for State Machine ROM N4.

If OP0 is high, HALT from Halt Flag latch L5 is set high when L5 is clocked by STROBE3.

If OPO, OP2, STROBE3, and VGCK are all low, VCTR from Vector Flag latch E5 is set high when E5 is clocked by the 12-MHz clock signal.

#### OP0

The Complementary Op Code 0 signal is software-generated by latch D6 in the Op Code and Intensity Latches circuit. This signal is opposite in state to OP0. If  $\overline{OP0}$  is low, NORM from Normalization Flag latch A6 is set high when  $\overline{STROBE0}$  clocks A6.  $\overline{OP0}$  is also the  $\overline{OP0}$  and  $\overline{OPX}$  input signal for Vector Address Controller J9.

#### OP1

The Op Code 1 signal is software-generated by latch D6 in the Op Code and Intensity Latches circuit. If the <u>data on line DVG6</u> is high, OP1 is set high when D6 is clocked by <u>LATCH1</u>. OP1 is multiplexed with AM5 by N3 in the State Machine circuit to produce the A5 input address bit for State Machine ROM N4. In addition, OP1 is the OP1 signal for Vector Address Controller J9.

In the Vector Timer circuit, OP1 is gated by K5 and E3 to enable a 1 to be loaded into the D input pin of Vector Timer P6 (if NORM or SCALE is low).

#### O

The Complementary Op Code 1 signal is sofware-generated by latch D6 in the Op Code and Intensity Latches circuit. This signal is opposite in state to OP1.  $\overline{OP1}$  is the clear signal for Vector Timers N6 and M6. When  $\overline{OP1}$  goes low, the count from N6 and M6 is stopped, causing a lowered count from the Vector Timer circuit. This low count is used to draw short vectors on the display.  $\overline{OP1}$  is also gated with the outputs of the Vector Timers by gates L3 and H3 to set  $\overline{STOP}$  to the low level.

#### OI

The Op Code 2 signal is software-generated by latch D6 in the Op Code and Intensity Latches circuit. If the data on line DVG7 is high, OP2 is set high when D6 is clocked by LATCH1. OP2 is multiplexed with AM6 by N3 in the State Machine circuit to produce the A6 input address bit for State Machine ROM N4.

If OP2, OP0, STROBE3, and VGCK are all low, VCTR from Vector Flag latch E5 is set high when E5 is clocked by the 12-MHz clock signal.

When STROBE1 goes low, if OP2 is low, it is applied through gates B7 and F3 of the Vector Scaling circuit as the load signal for counter C7. This allows the data latched from DVY8-DVY10 by D7 to be loaded into counter C7. When STROBE1 goes high, counter C7 counts down until it reaches the minimum count. At the same time, the Vector Timer circuit does a divide-by-2 (shift right) operation for each count of C7. (This is caused by SCALE being at the high state.) When C7 reaches its minimum count, it sets pin 12 high, dropping SCALE to the low state.

If OP2 and DVY12 are low, SCALELD from gate J6 is set low when STROBE2 goes low This allows Vector Scaling latch D7 to latch the new data on DVY8-DVY10.

If OP2 and DVY12 are low, STATCLK from J6 is set low when STROBE2 goes low This allows latch E6 of the Z Intensity and Blanking circuit to latch the data on DVY4-DVY7.

#### OP2

The Complementary Op Code 2 signal is software-generated by latch D6 in the Op Code and Intensity Latches circuit. This signal is opposite in state to OP2. If  $\overline{OP2}$ ,  $\overline{STROBE3}$ , and VGCK are low, CNTR from Center Flag latch E5 is set high when E5 is clocked by the 12-MHz clock signal.  $\overline{OP2}$  is also ORed with SA by gate R4 to produce the  $\overline{OP2}$  input for Vector Address Controller J9.

NOTICE TO ALL PERSONS RECEIVING THIS DRAWING CONFIDENTIAL: Reproduction forbidden without the specific writen permission of Atari, Inc., Sunnyvale, CA. This drawing is only conditionally issued, and neither receipt nor possession thereof confers or transfers any right in, or license to use, the subject mater of the drawing or any design or technical information shown thereon, nor any right to reproduce this drawing or any part thereof. Except for manufacture by vendors of Atari, Inc., and for manufacture under the corporation's written license, no right is granted to reproduce this drawing or the subject matter thereof, unless by written agreement with or written permission from the corporation.

# Gravitar™ PCB Signal Name Descriptions

© ATARI INC., 1982

SP-206 Sheet 9B 2nd printing

A Warner Communications Company

# **Description of Gravitar PCB Signal Names** (continued)

#### **PLAYER 1 LED**

The Player 1 LED On signal is developed from the data bit on line DB4. When clocked by LATCH, latch R9 of the Coin Door and Control Panel Output circuit latches the data bit on line DB4 to pin 19 of R9. This signal is applied through R103 to light the Player 1 LED on the game Control Panel.

#### **PLAYER 2 LED**

The Player 2 LED On signal is developed from the data bit on line DB5. When clocked by LATCH, latch R9 of the Coin Door and Control Panel Output circuit latches the data bit on DB5 to pin 16 of R9. This signal is applied through R102 to light the Player 2 LED on the game Control Panel.

The active high-level Power-On Reset signal is hardware-generated at pin 4 of F7 in the Power-On Reset circuit. POR is the clock signal that starts the count of E4 of the Clock circuit.

#### POR

The active low-level Power-On Reset signal is hardware-gener ated at pin 6 of inverter F7 in the Power-On Reset circuit. POR is generated when the voltage at pin 3 of R8 is less than about 7 volts or when the RESET test point is shorted to ground. POR is developed into the RESET signal to protect Microprocessor C2.

#### RAM

The Random-Access Memory Enable is an active low-level signal software-generated by Address Decoder R2 during addresses 0000 through 07FF. RAM is the <u>chip</u>-enable signal for Random-Access Memory N/P1. When low, RAM allows data to be read from or written to N/P1, depending upon the state of WRITE.

### RED

Red is a game PCB output signal developed from the data on line DVY2 in the R-G-B Output circuit. When DVY2 is high and latch K10 is clocked by STATCLK, the data bit on DVY2 is inverted and latched to pin 3 of K10. If both BLANK and Z BLANK are low, this data bit is again inverted by gate L10 to turn on Q6. Transistor Q6 generates the RED signal for the display.

Reset is an active low-level signal generated at pin 6 of K3 from either the Watchdog circuit or the Power-On Reset circuit. The Power-On Reset circuit sets RESET to an active low level either when the RESET test point is shorted to ground or during the time that the power-supply voltages are reaching their stabilized, regu-lated levels. This ensures that the Microprocessor Address Bus is stabilized before the microprocessor begins operation.

The Watchdog circuit sets RESET to an active low level if the microprocessor fails to output address 0D00 before Watchdog counter H4 has reached its maximum count.

RESET is also the clear signal for latch R9 in the Coin Door and Control Panel Output circuit.

In addition, RESET is gated with VGRST by gate L6 in the Halt Flag circuit to produce DISRST.

#### **ROM**

The Read-Only Memory Enable is an active high-level signal software-generated from Address Decoder R1 during addresses 9000 through 9FFF. ROM is ORed with I/OS by gate R4 to enable bi-directional data bus buffer F2 to pass data.

In addition, ROM is ANDed with DIS DAT to enable data buffer

#### **ROMO**

Read-Only Memory Chip Select 0 is an active low-level signal software-generated by Address Decoder R1 at addresses 9000-9FFF. ROMO is the chip-select signal for ROM D1 of the Read-Only Memory circuit. When low, ROM0 allows ROM D1 to be addressed and to pass data to buffer E2.

Read-Only Memory Chip Select 1 is an active low-level signal software-generated by Address Decoder R1 at addresses A000-AFFF. ROM1 is the chip-select signal for ROM E/F1 of the Read-Only Memory circuit. When low, ROM1 allows ROM E/F1 to be addressed and to pass data to buffer E2.

Read-Only Memory Chip Select 2 is an active low-level signal software-generated by Address Decoder R1 at addresses B000-BFFF. ROM2 is the chip-select signal for ROM H1 of the Read-Only Memory circuit. When low, ROM2 allows ROM H1 to be addressed and to pass data to buffer E2.

Read-Only Memory Chip Select 3 is an active low-level signal software-generated by Address Decoder R1 at addresses C000-CFFF. ROM3 is the chip-select signal for ROM J1 of the Read-Only Memory circuit. When low, ROM3 allows ROM J1 to be addressed and to pass data to buffer E2.

#### ROM4

Read-Only Memory Chip Select 4 is an active low-level signal software-generated by Address Decoder R1 at addresses D000-DFFF. ROM4 is the chip-select signal for ROM K/L1 of the Read-Only Memory circuit. When low, ROM4 allows ROM K/L1 to be addressed and to pass data to buffer E2.

#### ROM5

Read-Only Memory Chip Select 5 is an active low-level signal software-generated by Address Decoder R1 at addresses E000-EFFF. ROM5 is the chip-select signal for ROM M1 of the Read-Only Memory circuit. When low, ROM5 allows ROM M1 to be addressed and to pass data to buffer E2.

#### $R/\overline{W}B$

The Buffered Read/Write Enable is generated by Microprocessor C2, buffered by B1, and applied as the read/write enable signal for custom audio chips B3 and C/D3 of the Option Switch Input and Audio Output circuit. In the high state, R/WB is the read enable for the custom audio chips; in the low state, it is the write enable for these chips.

The Buffered Read/Write Eanble is generated at pin 2 of F3 in the Microprocessor circuit by inverting R/WB. R/WB is ANDed with BΦ2 and 3 MHz by gate K4 to produce WRITE. R/WB is the direction signal for Vector Memory Data Buffer P8 and determines the direction of data flow through P8. In the high state, R/WB allows data to pass through P8 from the data bus to the vector generator data bus; in the low state, it allows data to pass in the reverse direction.

The active high-level Signature Analysis Flag signal is hardware-generated at pin 12 of inverter J3 when test point SA at pin 13 is grounded. SA is used to place the game PCB in the mode to generate signatures for reading by a Signature Analyzer or the ATARI CAT Box.

The active low-level Signature Analysis Flag is hardware-generated when test point SA at pin 13 of J3 is grounded. SA is used to place the game PCB in the mode to generate signatures for reading by a Signature Analyzer or the ATARI CAT Box.

Signature Analysis Clock is a test point at pin 8 of gate B7 in the State Machine Clock Logic circuit. SACLK is used to apply the clock signal from the Signature Analyzer or ATARI CAT Box for the reading of game PCB signatures.

#### SAEN

Signature Analysis Enable is a test point at pin 8 of gate M5 in the Vector Address Selector circuit. SAEN is generated by gating VRAM with the data bit on line AM10 by gates J3 and M5. SAEN is used to enable a Signature Analyzer or the ATARI CAT Box for the reading of game PCB signatures.

#### SCALE

Scale is an active high-level signal generated by gate B7 of the Vector Scaling circuit. When OP2 is high and counter C7 is counting down, SCALE is set high. SCALE is ORed with NORM by gate K5 of the Vector Timer circuit to produce the load signal for Vector Timers M6, N6, P6, and R6. When SCALE is high, the Vector Timers perform a load operation for each count of C7 (at a 12-NHz rate). This results in a vector drawing time divided by a factor of 2<sup>n</sup>, where n equals the total counts of C7. When C7 reaches its minimum count, SCALE is set low.

SCALE is gated with VCTR, CNTR, DVY11-DVY12, and DVX11-DVX12 of the Normalization Flag circuit to produce the clear signal for latch A6.

#### SCALELD

Scale Load is an active low-level signal software-generated by gates N5. L3, and L6 of the Vector Generator circuit. When STROBE2, OP2, and DVY12 are all low, SCALELD is set low SCALELD is the clock signal for Vector Scaling latch D7. When SCALELD goes high, the data on lines DVY8-DVY10 are latched to the output pins of D7.

#### SINP1

Switch Input 1 is an active low-level signal software-generated by Address Decoder R2 at address 7800. SINP1 is the direction signal for bi-directional data buffer M9 of the Coin Door and Control Panel Input circuit and determines the direction of data flow through buffer M9.

#### SINP2

Switch Input 2 is an active low-level signal software-generated by Address Decoder R2 at address 8000. SINP2 is the direction signal for bi-directional data buffer L9 of the Coin Door and Control Panel Input circuit and determines the direction of data flow through buffer L9.

#### STATCLK

State Clock is an active low-level signal software-generated by gates N5, L3, and J6 of the Vector Generator circuit. When STROBE2, OP2, and DVY12 are all low, STATCLK is set low STATCLK is the clock for latch K10 in the R-G-B Output circuit and latch E6 in the Z Intensity and Blanking circuit. When STATCLK goes high, the data bits on DVY0-DVY2 are latched by K10, and those on DVY4-DVY7 are latched by E6.

Stop is an active low-level signal generated by gate H3 of the Vector Timer circuit. STOP is set low when Vector Timers N6, M6, P6, and R6 have reached their maximum count. If STOP is low, VCTR from Vector Flag latch E5 and CNTR from Center Flag latch E5 are both set low when E5 is clocked by the 12-MHz clock signal.

#### STROBE0

Strobe 0 is an active low-level signal software-generated by State Machine decoder H7. STROBE0 is the clock signal for Normalization Flag latch A6. It is also the STROBEO input for Vector Address Controller J9.

#### STROBE1

Strobe 1 is an active low-level signal software-generated by State Machine decoder H7. If OP2 is low, when STROBE1 goes low, the data latched at the outputs of D7 in the Vector Scaling circuit are loaded into counter C7. When STROBE1 goes high, C7 begins counting down.

STROBE1 is the STROBE1 input for Vector Address Controller J9.

#### STROBE2

Strobe 2 is an active low-level signal software-generated by State Machine decoder H7. If OP2 and DVY12 are both low, SCALELD from gate J6 is set low when STROBE2 goes low If OP2 and DVY12 are both low, STATCLK is set low when STROBE2 goes

STROBE2 is the STROBE2 input for Vector Address Controller

#### STROBE3

Strobe 3 is an active low-level signal software-generated by State Machine decoder  $\underline{\mathsf{H7.}}$   $\underline{\mathsf{STROBE3}}$  is the clock signal for Halt Flag latch L5 and is the STROBE3 input for Vector Address Controller J9.

If OPO, OP2, OP2, and VGCK are all low, VCTR from Vector Flag latch E5 and CNTR from Center Flag latch E5 are both set high when STROBE3 goes low

State signals ST0-ST2 are active high-level signals that are software-generated by State Machine ROM N4. These signals, together with ST3, are decoded by H7 of the State Machine circuit to produce LATCH0-LATCH3 and STROBE0-STROBE3. ST2 is used to develop ST3 and is also the ST2 input for Vector Address Controller J9.

### NOTICE TO ALL PERSONS RECEIVING THIS DRAWING

NOTICE TO ALL PERSONS RECEIVING THIS DRAWING CONFIDENTIAL: Reproduction forbidden without the specific written permission of Atari, Inc., Sunnyvale, CA. This drawing is only conditionally issued, and neither receipt nor possession thereof confers or transfers any right in, or license to use, the subject matter of the drawing or any design or technical information shown thereon, nor any right to reproduce this drawing or any part thereof. Except for manufacture by vendors of Atari, Inc., and for manufacture under the corporation's written license, no right is granted to reproduce this drawing or the subject matter thereof, unless by reproduce this drawing or the subject matter thereof, unless by written agreement with or written permission from the corporation.

# Gravitar™ PCB Signal Name Descriptions

© ATARI INC., 1982

SP-206 Sheet 10A 2nd printing

W A Warner Communications Company

# Description of Gravitar PCB Signal Names (continued)

#### ST3

State signal ST3 is an active high-level signal hardware-generated by Decoder Disable latch A7. ST3 is opposite in state to VGCK, and is delayed by one pulse of the 12-MHz clock signal if the Q4 output from State Machine ROM N4 is low and VMEM is high. If the Q4 output from N4 is high, ST3 is high. When ST3 is high, State Machine decoder H7 is disabled. When ST3 is low, H7 decodes the data on lines ST0-ST2 to produce LATCH0-LATCH3 and STROBE0-STROBE3.

#### VCTR, VCTR

The Vector Flag signals are software-generated by Vector Flag latch E5. If OP0, OP2, STROBE3, and VGCK are low and HALT is high, VCTR is set high and VCTR is set low when E5 is clocked by the 12-MHz clock signal. VCTR is ORed with CNTR by gate M5 to set GO high.

SCALE, CNTR, DVY11-DVY12, and DVX11-DVX12 are gated with VCTR to produce the clear signal for Nomalization Flag latch A6.

In the Z Intensity and Blanking circuit, VCTR is the clock signal for latch H6 and the serial input signal for shift register M3.

VCTR and VCTR are used by the DAC Reference and Bipolar Current Sources circuit to set the X BIP, Y BIP, X REF, and Y REF levels

#### **VGCK**

The Vector Generator clock signal is generated at pin 18 of buffer B1 in the Microprocessor circuit. VGCK is derived from the 1.5 MHz clock signal and is applied to AND gate J5 of the State Machine Clock Logic circuit. VGCK is the basic timing signal of the State Machine circuit.

#### VGGO

The Vector Generator Go signal is an active low-level signal software-generated by Address Decoder P3 at address 8840. VGGO is the clear signal for latch L5 of the Halt Flag circuit. When low, VGGO sets HALT to the inactive low level.

#### VGRST

Vector Generator Reset is an active low-level signal softwaregenerated by Address Decoder P3 at address 8880. VGRST is ORed with RESET by gate L6 of the Halt Flag circuit to produce DISRST.

#### VMEM

The Vector Memory Select Enable is an active low-level signal software-generated by Address Decoder R1 during addresses 2000 through 5FFF. VMEM is the select-enable signal for Vector Address Selectors K8, L8, M8, and N8. When low, VMEM allows the Vector Address Selectors to produce VW, BUFFEN, and the AM0-AM12 multiplexed address bits. VMEM is also applied to gate K5 of the State Machine Clock Logic circuit where it is used to generate ST3.

#### VRAM

The Vector Random-Access Memory Chip Enable is an active low-level signal software-generated by Vector Address Decoder J7 at addresses 2000-27FF. When low, VRAM enables Vector Random-Access Memory K7 to be addressed to either receive or transmit data, depending upon the state of VW. VRAM is also used to produce the SAEN signal from M5 of the Vector Address Selector circuit.

#### VROM0

Vector Read-Only Memory Chip Select 0 is an active low-level signal software-generated by Vector Address Decoder J7 at addresses 2800-2FFF. VROM0 is the chip-select signal for ROM L7 of the Vector Read-Only Memory circuit. When low, VROM0 allows ROM L7 to be addressed and to pass data to the Vector Generator Data Bus.

#### VROM1

Vector Read-Only Memory Chip Select 1 is an active low-level signal software-generated by Vector Address Decoder J7 at addresses 3000-3FFF. VROM1 is the chip-select signal for ROM M/N7 of the Vector Read-Only Memory circuit. When low, VROM1 allows ROM M/N7 to be addressed and to pass data to the Vector Generator Data Bus.

#### VROM2

Vector Read-Only Memory Chip Select 2 is an active low-level signal software-generated by Vector Address Decoder J7 at addresses 4000-4FFF. VROM2 is the chip-select signal for ROM N/P7 of the Vector Read-Only Memory circuit. When low, VROM2 allows ROM N/P7 to be addressed and to pass data to the Vector Generator Data Bus.

#### VROM3

Vector Read-Only Memory Chip Select 3 is an active low-level signal software-generated by Vector Address Decoder J7 at addresses 5000-5FFF. VROM3 is the chip-select signal for ROM R7 of the Vector Read-Only Memory circuit. When low, VROM3 allows ROM R7 to be addressed and to pass data to the Vector Generator Data Bus.

### **₩**

The Vector Write Enable is an active low-level signal software-generated from Vector Address Selector K8, ANDed with  $\overline{B}\Phi 2$  by gate J6, and applied as the write-enable signal for Vector Random-Access Memory K7. When low,  $\overline{VW}$  allows data to be written to K7; when high,  $\overline{VW}$  permits data to be read from K7.

#### WDCLF

Watchdog Clear is an active low-level signal software-generated by Address Decoder P3 at address 8980. WDCLR is ORed with POR by gate E3 to clear the count of Watchdog counter H4.

#### WDDIS

Watchdog Disable is a test point at pin 9 of AND gate L4 in the Watchdog circuit. When WDDIS is grounded, RESET is prevented from going to an active low level (except when the RESET test point is grounded).

#### WRITE

Write Enable is an active low-level signal generated by gate K4 of the Microprocessor circuit. WRITE is used to enable Address Decoder P3 and Random-Access Memory N/P1. WRITE is also applied to pin 11 of K8 in the Vector Address Selector circuit to develop VW.

#### X R

The X-Axis Bipolar Current is set by R99 of the DAC Reference and Bipolar Current Sources circuit. This is the current source for pin 18 of X-axis digital-to-analog converter (DAC) A/B9 of the X-Axis Output circuit.

#### X OUT

X Output is a game PCB output signal generated by the X-Axis Output circuit. X OUT carries the horizontal beam deflection signal for the drawing of vectors on the display.

#### X REF

The X-Axis Voltage Reference is set by the DAC Reference and Bipolar Current Sources circuit. This is the reference voltage applied to pin 14 of X-axis digital-to-analog converter (DAC) A/B9 of the X-Axis Output circuit.

#### Y BIP

The Y-Axis Bipolar Current is set by R98 of the DAC Reference and Bipolar Current Sources circuit. This is the current source for pin 18 of Y-axis digital-to-analog converter (DAC) F9 of the Y-Axis Output circuit.

#### Y OUT

Y Output is a game PCB output signal generated by the Y-Axis Output circuit. Y OUT carries the vertical beam deflection signal for the drawing of vectors on the display.

#### Y RFF

The Y-Axis Voltage Reference is set by the DAC Reference and Bipolar Current Sources circuit. This is the reference voltage applied to pin 14 of Y-axis digital-to-analog converter (DAC) F9 of the Y-Axis Output circuit.

#### Z0-Z2, Z1-Z2

Z Intensity signals Z0-Z2 and  $\overline{Z1}$ - $\overline{Z2}$  are software-generated by latch C6 in the Op Code and Intensity Latches circuit. These signals are derived from the data on lines DVG51-DVG7 when C6 is clocked by  $\overline{LATCH3}$ . If the binary count carried by Z0-Z2 is not equal to 1, these signals are the input signals for latch F6 in the Z Intensity and Blanking circuit. If the binary count carried by Z0-Z2 is 1, Z Intensity signals Z0,  $\overline{Z1}$ , and  $\overline{Z2}$  are ANDed by gate F5 of the

Z Intensity and Blanking circuit to produce the select signal for latch F6. This select signal causes the latched data from E6 to be applied as the input signals for latch F6.

#### Z OU

Z Intensity Output is a game PCB output signal generated by the Z Intensity and Blanking circuit from either DVY4-DVY7 or Z0-Z2. The Q output signals from latch H6 are summed at the base of Q7. Transistors Q7 and Q9 buffer Z OUT before it is sent to the game display circuitry to control the display intensity.

#### 3 KHZ

The 3 kHz clock signal is generated at pin 6 of Clock counter F4 and is applied through switch input buffer M9 of the Coin Door and Control Panel Input circuit (when SINP1 is low). The 3 kHz clock is read by the microprocessor on data line DB7. This frequency is the time reference for the Microprocessor C2.

#### 12 KH7

The 12 kHz clock signal is generated at pin 4 of Clock counter F4 and is applied to reset A4 of the High-Score Table.

#### 3 MHZ

The 3 MHz clock signal is generated at pin 2 of Clock counter F4. The 3 MHz signal is ANDed with R/WB and BΦ2 by gate K4 to produce WRITE. It is also applied to AND gate J5 of the State Machine Clock Logic and to shift register M3 of the Z Intensity and Blanking circuit.

#### 6 MHZ

The 6 MHz clock signal is generated at pin 3 of Clock counter F4 and is applied to gate J5 of the State Machine Clock Logic circuit

#### 12 MHZ

The 12 MHz clock signal is generated at pin 10 of inverter F3 in the Clock circuit. This signal clocks the Vector Timer Shifters, the Vector Flag latch, and the Center Flag latch.

NOTICE TO ALL PERSONS RECEIVING THIS DRAWING CONFIDENTIAL: Reproduction forbidden without the specific written permission of Atari, Inc., Sunnyvale, CA. This drawing is only conditionally issued, and neither receipt nor possession thereof confers or transfers any right in, or license to use, the subject matter of the drawing or any design or technical information shown thereon, nor any right to reproduce this drawing or any part thereof. Except for manufacture by vendors of Atari, Inc., and for manufacture under the corporation's written license, no right is granted to reproduce this drawing or the subject matter thereof, unless by written agreement with or written permission from the corporation.

# **Gravitar™ PCB Signal Name Descriptions**

© ATARI INC., 1982

SP-206 Sheet 10B 2nd printing

M A Warner Communications Company

# **Gravitar Troubleshooting with the CAT Box**

### **Table of Contents**

| Gravit | ar Memory Map                                | Sheet 11A | G. Checking the Analog Vector-Genera-   |           |

|--------|----------------------------------------------|-----------|-----------------------------------------|-----------|

|        | eshooting with the Read/Write Con-           | Sheet 11A | tor                                     |           |

| Δ      | CAT Box Preliminary Set-Up                   | Sheet 11A | and Invert Outputs                      | Sheet 12A |

|        | Checking the Address Lines                   |           | Troubleshooting with Signature Analysis | Sheet 12A |

| C.     | Checking the Data Lines                      | Sheet 11A | A. Checking the Address Lines and Ad-   |           |

|        | Checking the RAM                             |           | dress Decoders                          | Sheet 12A |

|        | Checking the Custom Audio I/O                |           | B. Checking the Vector Generator        |           |

| _      | Chips                                        | Sheet 11B | Troubleshooting with Checksums          | Sheet 12B |

| F.     | Checking the Player and Option Switch Inputs | Sheet 11B | Toubleshooting the Watchdog Circuit     | Sheet 12B |

### **MEMORY MAP**

| HEXA-                                                                                              |                                 |                                 |                                 |                                      |                                      |                       | A                     | DDR                        | ESS                        | BUS                        | <u> </u>   |           |            |            |            |           | R/W                                        |             |                  |                  | DATA             | A BU             | s                |                  |                  | FUNCTION                                                                                        |

|----------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------|---------------------------------|--------------------------------------|--------------------------------------|-----------------------|-----------------------|----------------------------|----------------------------|----------------------------|------------|-----------|------------|------------|------------|-----------|--------------------------------------------|-------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|-------------------------------------------------------------------------------------------------|

| DECIMAL<br>ADDRESS                                                                                 | A15                             | A14                             | A13                             | A12                                  | A11                                  | A10                   | <b>A9</b>             | A8                         | <b>A</b> 7                 | <b>A6</b>                  | <b>A</b> 5 | <b>A4</b> | <b>A</b> 3 | <b>A</b> 2 | <b>A</b> 1 | A0        | 1 ''''                                     | D7          | D6               | D5               | D4               | D3               | D2               | D1               | D0               | 1 1011011011                                                                                    |

| E000-EFFF<br>D000-DFFF<br>C000-CFFF<br>B000-BFFF<br>A000-AFFF<br>9000-9FFF                         | 1<br>1<br>1<br>1<br>1           | 1<br>1<br>1<br>0<br>0           | 1<br>0<br>0<br>1<br>1           | 1<br>0<br>1<br>0                     | A A A A A                            | A A A A A             | A A A A A             | A A A A A                  | A A A A A                  | A A A A A                  | A A A A A  | A A A A A | A A A A A  | A A A A A  | A A A A A  | A A A A A | R<br>R<br>R<br>R<br>R                      | D D D D     | D<br>D<br>D<br>D | ROM 5<br>ROM 4<br>ROM 3<br>ROM 2<br>ROM 1<br>ROM 0                                              |

| 8800                                                                                               | 1                               | 0                               | 0                               | 0                                    | 1                                    |                       |                       |                            |                            |                            |            |           |            |            |            |           | R                                          | D           | D                | D                | D                | D                | D                | D                | D                | CABINET 1<br>START 2<br>START 1<br>THRUST 2<br>ROT LEFT 2<br>ROT RIGHT 2<br>FIRE 2<br>SHIELDS 2 |

| 89C0<br>8980<br>8940<br>8900<br>88C0<br>8880<br>8840                                               | 1<br>1<br>1<br>1<br>1<br>1      | 0<br>0<br>0<br>0<br>0           | 0<br>0<br>0<br>0<br>0           | 0<br>0<br>0<br>0<br>0                | 1<br>1<br>1<br>1<br>1<br>1           | 0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0 | 1<br>1<br>1<br>1<br>0<br>0 | 1<br>1<br>0<br>0<br>1<br>1 | 1<br>0<br>1<br>0<br>1<br>0 | Α          | Α         | Α          | Α          | Α          | Α         | \$ \$ \$ \$ \$ \$ \$ \$ \$                 | D           | D                | D                | D                | D<br>D           | D<br>D           | D<br>D           | D<br>D           | SPARE WT<br>WDCLR<br>EAROMWR<br>EAROMCON<br>INTACK<br>VGRST<br>VGGO                             |

| 8800                                                                                               | 1                               | 0                               | 0                               | 0                                    | 1                                    | 0                     | 0                     | 0                          | 0                          | 0                          |            |           |            |            |            |           | w                                          | D           | D                | D                | D                | D                | D                | D                | D                | INVERT Y INVERT X PLAYER 2 LED PLAYER 1 LED COIN LOCKOUT BANK SEL COIN CNTR-L COIN CNTR-R       |

| 8000                                                                                               | 1                               | 0                               | 0                               | 0                                    | 0                                    |                       |                       |                            |                            |                            |            |           |            |            |            |           | R                                          | D           | D                | D                | D                | D                | D                | D                | D                | OPTION 2 OPTION 1 OPTION 0 THRUST 1 ROT LEFT 1 ROT RIGHT 1 FIRE 1 SHIELDS 1                     |

| 7800                                                                                               | 0                               | 1                               | 1                               | 1                                    | 1                                    |                       |                       |                            |                            |                            |            |           |            |            |            |           | R                                          | D           | D                | D                | D                |                  | D                | D                | D                | 3 KHZ HALT SA SELF-TEST COIN-AUX COIN L COIN R                                                  |

| 7000<br>6800<br>6000<br>5000-5FFF<br>4000-4FFF<br>3000-3FFF<br>2800-2FFF<br>2000-27FF<br>0000-07FF | 0<br>0<br>0<br>0<br>0<br>0<br>0 | 1<br>1<br>1<br>1<br>1<br>0<br>0 | 1<br>1<br>0<br>0<br>1<br>1<br>1 | 1<br>0<br>0<br>1<br>0<br>1<br>0<br>0 | 0<br>1<br>0<br>A<br>A<br>A<br>1<br>0 | A A A A A             | A A A A A             | A A A A A                  | A A A A A                  | A A A A A                  | A A A A A  | A A A A A | A A A A A  | A A A A A  | A A A A A  | A A A A A | R<br>R/W<br>R<br>R<br>R<br>R<br>R/W<br>R/W | D D D D D D |                  | D D D D D D D    | D D D D D D D    | D D D D D D D    | D D D D D D      | D D D D D D      | D D D D D D D    | EAROMRD I/O0 I/O1 VROM 3 VROM 2 VROM 1 VROM 0 VRAM RAM                                          |

# Troubleshooting with the Read/Write Controller

### A. CAT Box Preliminary Set-Up

- Remove the electrical power from the game and the CAT Box.

- Remove the wiring harness from the game PCB.

- 3. Remove the game PCB from the game cabinet.

- Remove Microprocessor C2 from the game PCB.

- Connect the harness from the game to the game PCB. (Use extender cables, if available.)

- Connect together the Φ0 and Φ2 test points on the game PCB with the shortest possible jumper.

- . Connect the WDDIS test point to ground.

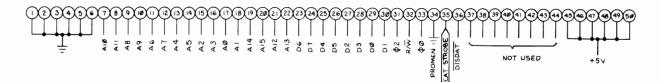

- Connect the CAT Box flex cable to the game PCB edge test connector.

- 9. Apply power to the game and to the CAT Box.

- 10. Set CAT Box switches as indicated:

- a. TESTER SELF-TEST: OFF

- b. TESTER MODE: R/W

- 11. Press TESTER RESET.

- 12. Connect the DATA PROBE to the CAT Box.

- Connect the DATA PROBE ground clip to a game PCB ground test point.

### **B.** Checking the Address Lines

- Perform the CAT Box preliminary set-up.

- 2. Set CAT Box switches as indicated:

- a. BYTES: 1

- b. PULSE MODE: UNLATCHED

- c. R/W MODE: (OFF)

- d. R/W: READ

- Key in the address pattern given in Table 1 (use AAAA to start) with the CAT Box keyboard.

- Set R/W MODE to STATIC.

- Probe the IC-pin with the DATA PROBE and check that the 1 or 0 LED indicated in Table 1 lights up. Repeat this step for each address line listed in Table 1.

- 6. Repeat parts 2-c through 5 using address 5555 in part 3.

Table 1 Address Lines

| LOGIC STATE<br>FOR<br>ADDRESS AAAA | IC-PIN                        | LOGIC STATE<br>FOR<br>ADDRESS 5555 |

|------------------------------------|-------------------------------|------------------------------------|

| 1 0                                | R2-14<br>R2-13                | 0                                  |

| 1                                  | R2-12                         | 0                                  |

| 0                                  | B1-5                          | 1                                  |

| 1                                  | B1-7                          | 0                                  |

| 0                                  | B1-12                         | 1                                  |

| 1                                  | B1-14                         | 0                                  |

| 0<br>1<br>0<br>1                   | B1-16<br>C1-9<br>C1-7<br>C1-5 | 0<br>1<br>0                        |

| 0                                  | C1-3                          | 1                                  |

| 1                                  | C1-12                         | 0                                  |

| 0                                  | C1-14                         | 1                                  |

| 1                                  | C1-16                         | 0                                  |

| 0                                  | C1-18                         | 1                                  |

### C. Checking the Data Lines

- 1. Perform the CAT Box preliminary set-up.

- 2. Set CAT Box switches as indicated:

- a. BYTES:1

- b. R/W MODE: (OFF)

- c. R/W: WRITE

- Key in address 0000 with the keyboard.

- 4. Press DATA SET.

- 5. Key in data AA with the keyboard.

- 6. Set R/W MODE to PULSE and then to STATIC.

- Probe the IC-pin with the DATA PROBE and check that the 1 or 0 LED indicated in Table 2 lights up. Repeat this check for each IC-pin in Table 2.

- 8. Repeat parts 4 through 7 using data 55 in part 5.

Continued on sheet 11B

#### NOTICE TO ALL PERSONS RECEIVING THIS DRAWING

NOTICE TO ALL PERSONS RECEIVING HIS DRAWING CONFIDENTIAL: Reproduction forbidden without the specific written permission of Atari, Inc., Sunnyvale, CA. This drawing is only conditionally issued, and neither receipt nor possession thereof confers or transfers any right in, or license to use, the subject matter of the drawing or any design or technical information shown thereon, nor any right to reproduce this drawing or any part thereof. Except for manufacture by vendors of Atari, Inc., and for manufacture under the corporation's written license, no right is granted to reproduce this drawing or the subject matter thereof, unless by written agreement with or written permission from the corporation.

# Gravitar™ PCB Troubleshooting

© ATARI INC., 1982

SP-206 Sheet 11A 2nd printing

Table 2 Data Lines

| LOGIC STATE<br>FOR<br>ADDRESS AAAA | IC-PIN | LOGIC STATE<br>FOR<br>ADDRESS 5555 |

|------------------------------------|--------|------------------------------------|

| 1                                  | F2-11  | 0                                  |

| 0                                  | F2-12  | 1                                  |

| 1                                  | F2-13  | 0                                  |

| 0                                  | F2-14  | 1                                  |

| 1                                  | F2-15  | 0                                  |

| 0                                  | F2-16  | 1                                  |