# 9100 Series

## 9100A-017 Vector Output I/O Module Service Manual

### LIMITED WARRANTY

John Fluke Mfg. Co., Inc. (Fluke) warrants your 9100A-017 Vector Output I/O Module to be free from defects in material and workmanship under normal use and service for one (1) year from the date of shipment. Software and firmware products are provided "AS IS." We do not warrant that software or firmware products will be error free, operated without interruption or that all errors will be corrected. This warranty extends to you if you are the original purchaser and does not apply to fuses, batteries, or any product which, in our sole opinion, has been subject to misuse, alteration, or abnormal conditions of operation or handling.

To obtain warranty service, contact a Fluke Service Center or send the product, with the description of the difficulty, postage prepaid, to the nearest Fluke Service Center. Fluke assumes no risk for damage in transit.

Fluke will, at our option, repair or replace the defective product free of charge. However, if we determine that the failure was caused by misuse, alteration, or abnormal condition of operation or handling, you will be billed for the repair. The repaired product will be returned to you, transportation prepaid.

THIS WARRANTY IS EXCLUSIVE AND IS IN LIEU OF ALL OTHER WARRANTIES, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE OR USE. FLUKE WILL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES OR LOSS WHETHER IN CONTRACT, TORT, OR OTHERWISE.

#### Table of Contents

| SECTION | TITLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PAGE                                                                                                                                                                                                                                                                                    |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | Introduction and Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 1-1                                                                                                                                                                                                                                                                                   |

|         | INTRODUCTION1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                         |

|         | Theory of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 2-1                                                                                                                                                                                                                                                                                   |

|         | VECTOR OUTPUT I/O MODULE OVERVIEW INPUT SECTION THEORY OF OPERATION  Mainframe to Bus Interface Functional Block  MAINFRAME ADDRESSING OF THE MODULE  CUSTOM CHIP SELECTION  Custom Chip Functional Block  Clock and Enable Mux Functional Block  CLOCK AND ENABLE MUX OPERATION  General Control Latch Functional Block  CONTROL REGISTER  DATA COMPARISON INPUTS  FUSE DETECTION  DATA COMPARISON AND GENERAL INTERRUPTS  DATA COMPARISON AND GENERAL INTERRUPTS  DATA COMPARE EQUAL OUTPUT PIN  OPERATION OF GENERAL CONTROL LATCH BLOCK  Connector Code Functional Block  Input Protection Functional Block  OUTPUT SECTION THEORY OF OPERATION  Main PCA to Top PCA Interface Functional Block  OUTPUT Control Functional Block  Output Control Functional Block  CHIP COUNTER OPERATION  SSLOGIC (Start/Stop Logic) Functional Block  SIGNAL POLARITY/CONTROL REGISTER  DRIVE CLOCK SELECTION  HANDSHAKE SYNCHRONIZATION  VECTOR DRIVE COMPLETE LOGIC  Vector Address Functional Block | . 2-1<br>. 2-5<br>. 2-5<br>. 2-5<br>. 2-6<br>. 2-8<br>. 2-9<br>. 2-11<br>. 2-12<br>. 2-12<br>. 2-13<br>. 2-13<br>. 2-13<br>. 2-16<br>. 2-16<br>. 2-16<br>. 2-16<br>. 2-17<br>. 2-18<br>. 2-20<br>. 2-20<br>. 2-21<br>. 2-22<br>. 2-22<br>. 2-22<br>. 2-22<br>. 2-22<br>. 2-23<br>. 2-25 |

|         | Vector Pattern RAM Functional Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 2-26<br>. 2-27<br>. 2-28                                                                                                                                                                                                                                                              |

|         | Drive Status Functional Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                         |

| SECTION | TITLE                                                                                                                                                     | PAGE                            |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 3       | Maintenance                                                                                                                                               | 3-1                             |

|         | INTRODUCTION  CHANGING THE VECTOR OUTPUT I/O MODULE FUSE  CLEANING  VECTOR OUTPUT I/O MODULE SELF TEST  DISASSEMBLY  TROUBLESHOOTING  General Information | 3-1<br>3-2<br>3-2<br>3-2<br>3-3 |

| 4       | List of Replaceable Parts                                                                                                                                 | 4-1                             |

|         | INTRODUCTION                                                                                                                                              | 4-3                             |

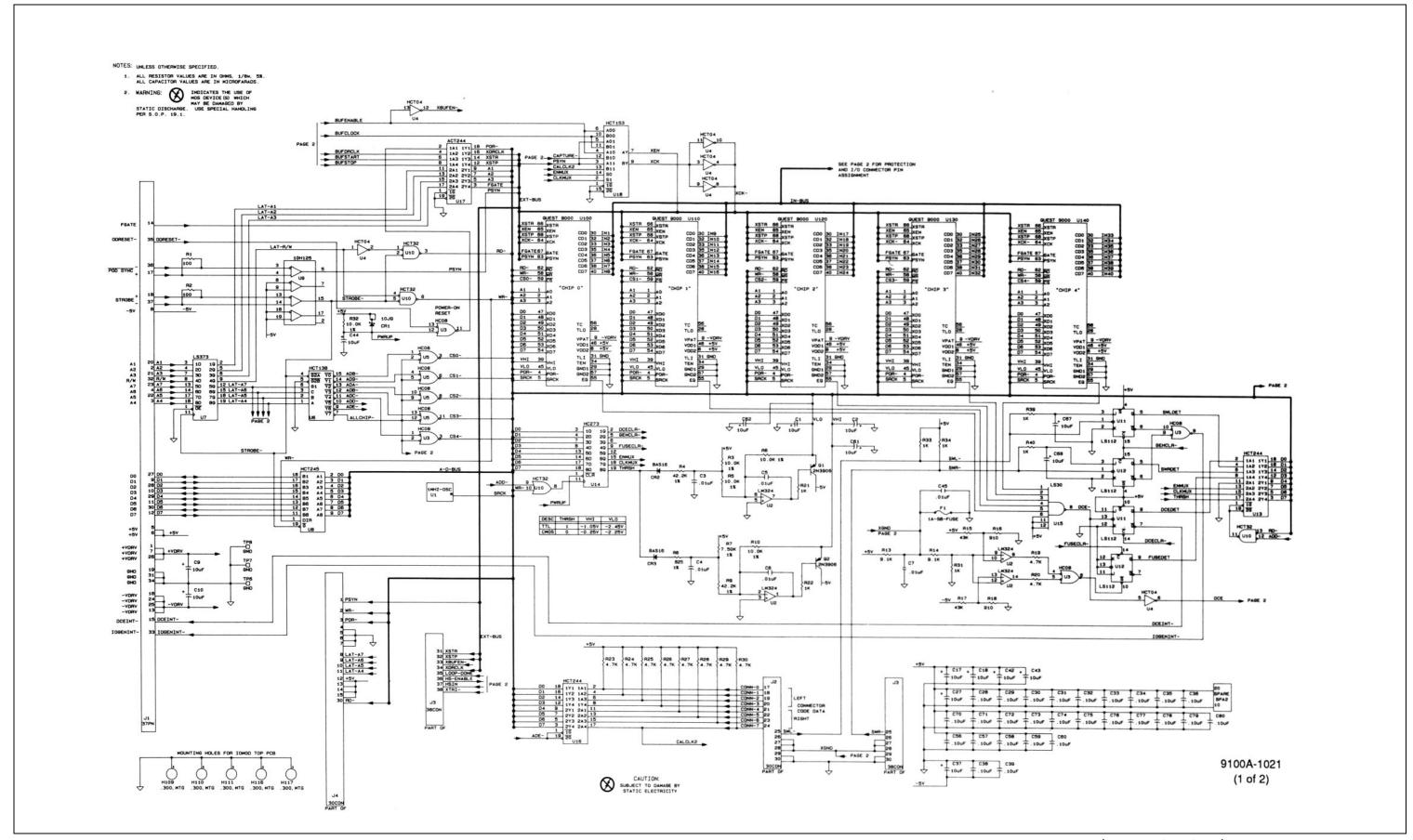

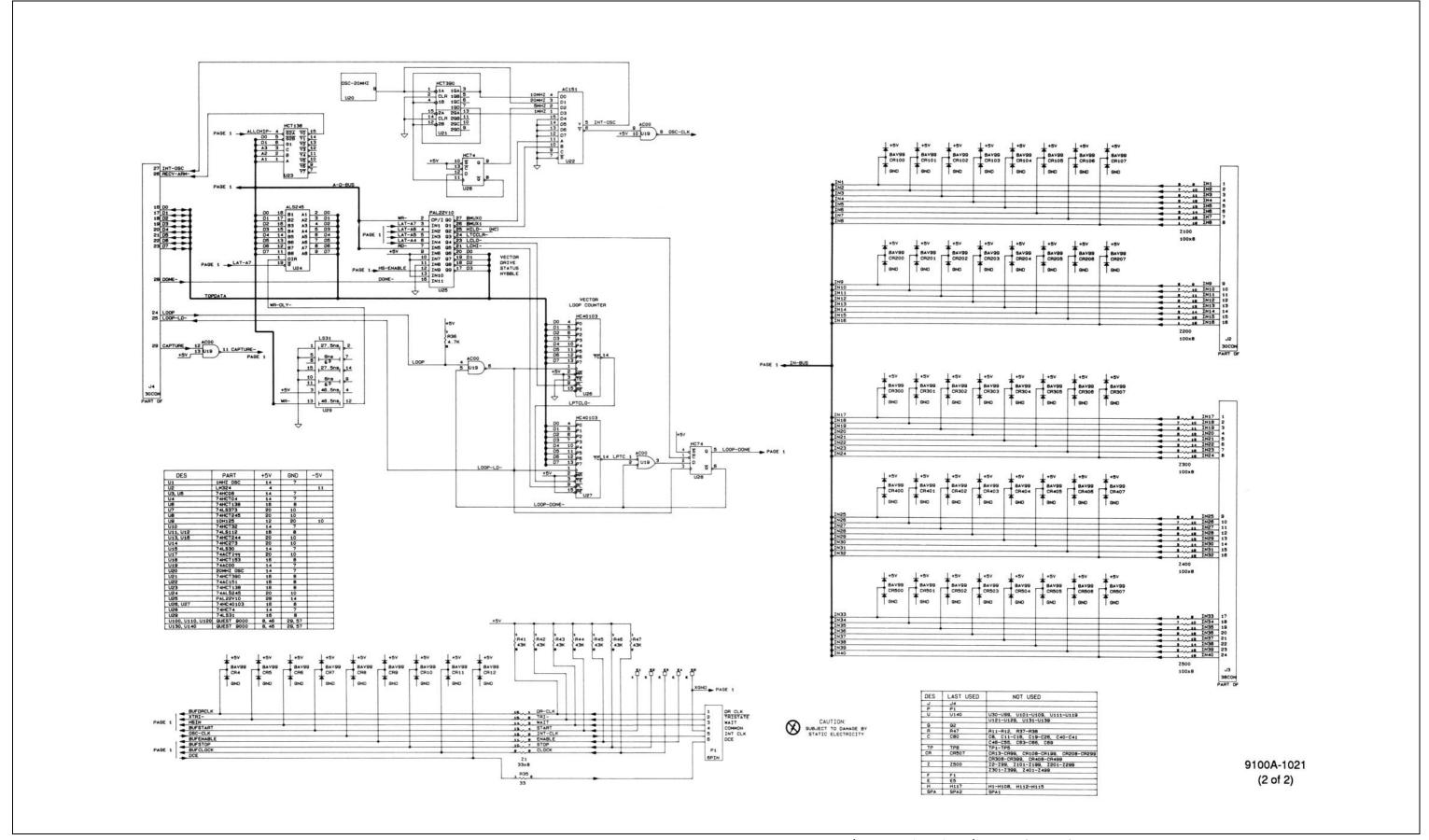

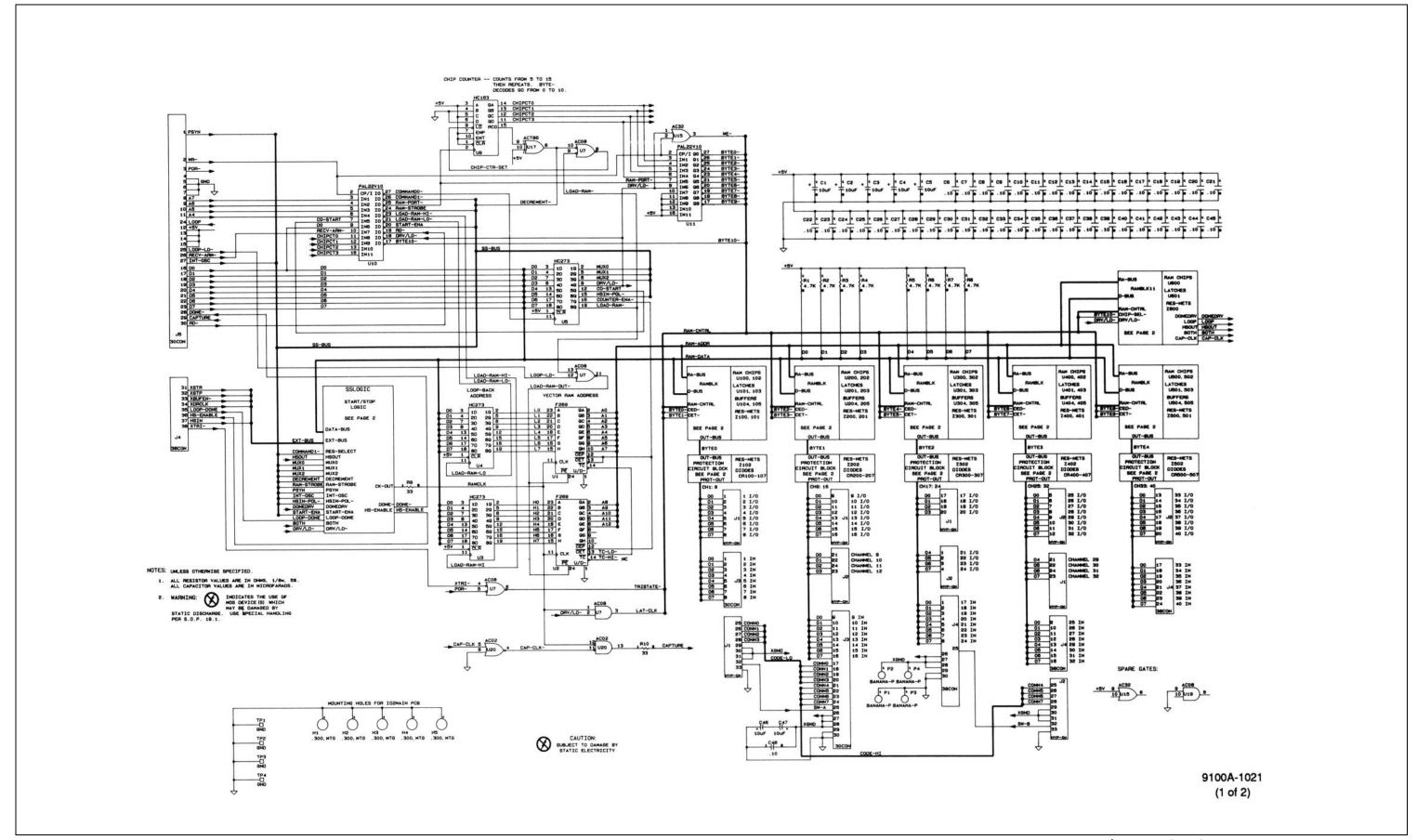

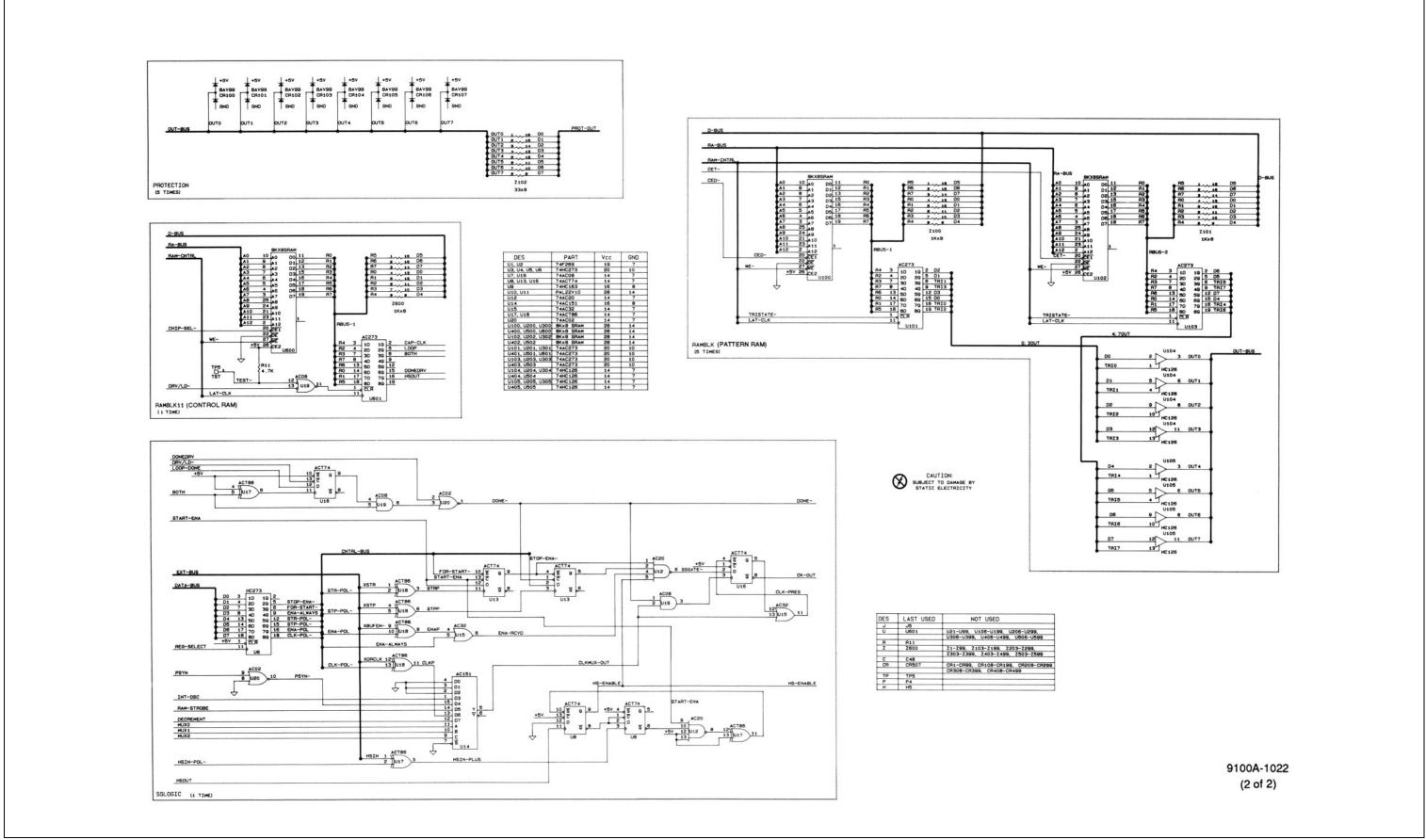

| 5       | Schematic Diagrams                                                                                                                                        | 5-1                             |

#### List of Tables

| TABLE | TITLE                                                     | PAGE |

|-------|-----------------------------------------------------------|------|

| LADUE | 11111                                                     | FAGE |

| 1-1.  | Vector Output I/O Module Specifications                   | 1-1  |

| 2-1.  | Custom Chip Pin Description                               | 2-11 |

| 2-2.  | Clock and Enable Mux Truth Table                          | 2-12 |

| 2-3.  | VHI and VLO for TTL and CMOS Logic Levels                 | 2-15 |

| 2-4.  | Dip-Clip and Calibration Module Configuration Codes       | 2-17 |

| 2-5.  | Connector Code Examples                                   | 2-18 |

| 2-6.  | Vector I/O Module Output Section Address Map              | 2-19 |

| 2-7.  | U25 Drive Register 2 Bit Description (Write @ \$D0X21)    | 2-20 |

| 2-8.  | U5 Register Bit Description (Write @ \$D0X01)             | 2-21 |

| 2-9.  | U6 Register Bit Description (Write @ \$D0X11)             | 2-23 |

| 2-10. | U25 ID/Status Register Bit Description (Read @ \$D0X01) . | 2-29 |

| 4-1.  | 9100A-017 Vector I/O Final Assembly                       | 4-5  |

| 4-2.  | Al Main PCA                                               | 4-8  |

| 4-3.  | A2 Top PCA                                                | 4-10 |

| 4-4.  | Module Revision Information                               | 2-12 |

#### List of Figures

| FIGURE | TITLE                                      | PAGE |

|--------|--------------------------------------------|------|

| 2-1.   | Input Section Functional Block Diagram     |      |

| 2-2.   | Output Section Functional Block Diagram    | 2-4  |

| 2-3.   | Input Section Address Decoding Summary     | 2-7  |

| 2-4.   | Address Decoding Example                   | 2-8  |

| 2-5.   | Hot-Bit Decoding Examples                  | 2-9  |

| 2-6.   | Bus Interface Timing Diagram               | 2-10 |

| 2-7.   | I/O Module Control and Interrupt Registers | 2-14 |

| 2-8.   | Custom Chip Voltage Level Detection        | 2-15 |

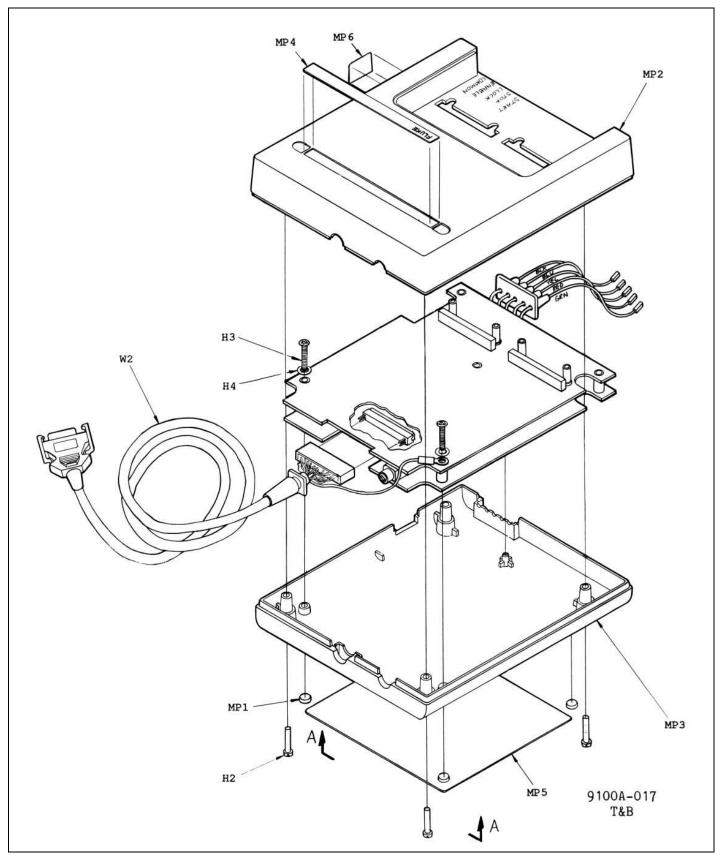

| 4-1.   | 9100A-017 Final Assembly                   | 4-6  |

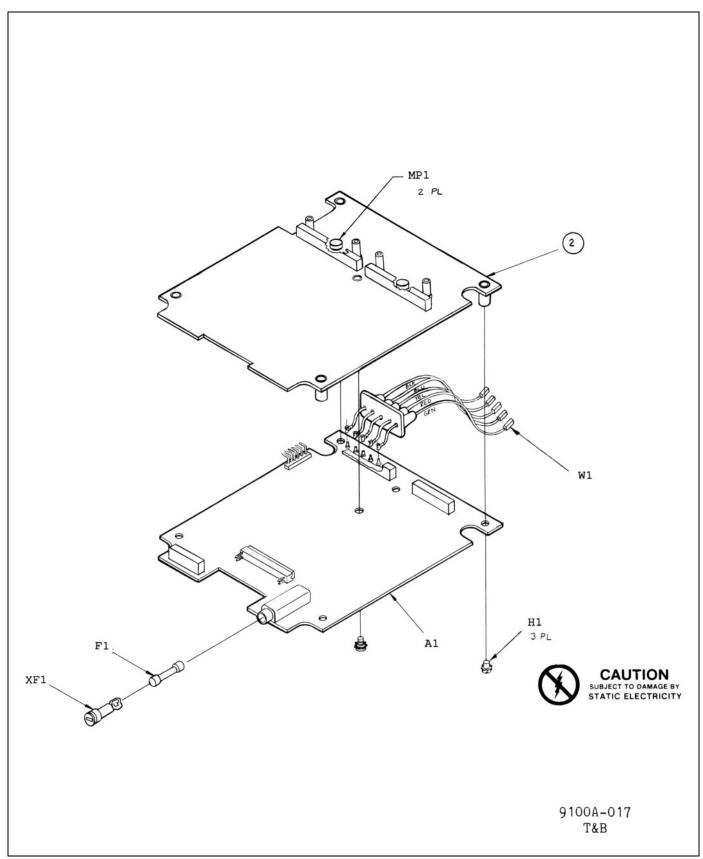

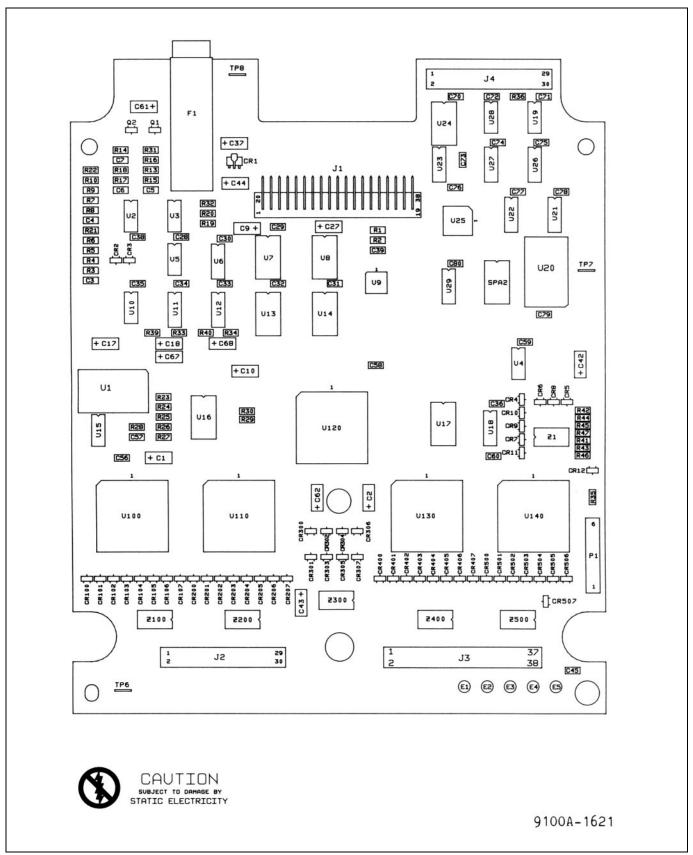

| 4-2.   | Al Main PCA                                | 4-9  |

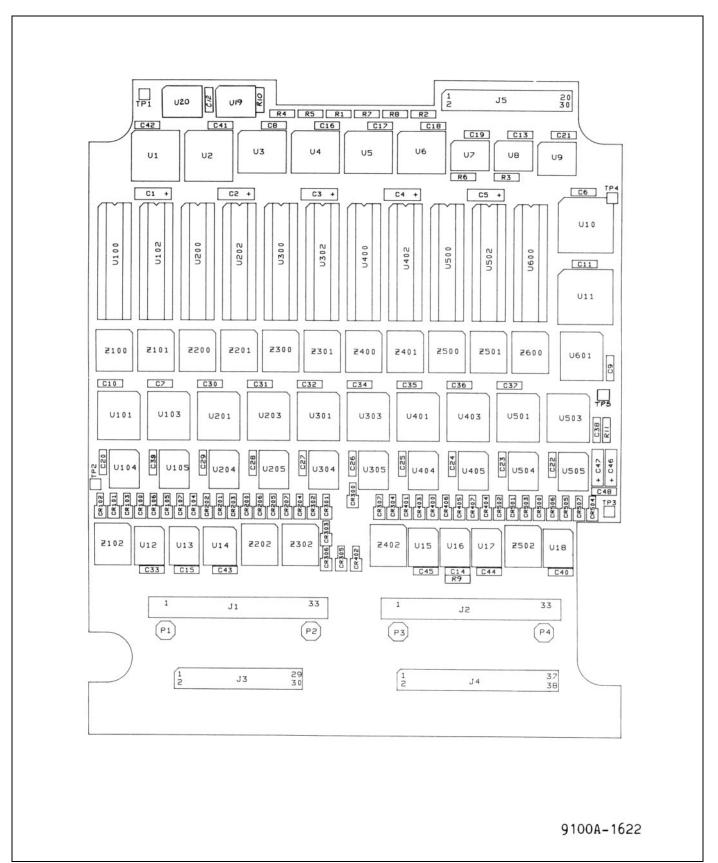

| 4-3.   | A2 Top PCA                                 | 4-11 |

## Section 1 Introduction and Specifications

#### INTRODUCTION

This manual presents service information for the 9100A-017 Vector Output I/O Module. Included are a theory of operation, general maintenance procedures, performance tests, troubleshooting information, a list of replacement parts, and schematic diagrams.

#### **SPECIFICATIONS**

Table 1-1 contains the specifications for the Vector Output I/O Module.

NOTE

Output specifications for Table 1-1 were obtained using the Y9100-102 Card Edge Interface Module into 10 LSTTL loads. Results may vary depending on the impedance, length, and shielding of the connector used. (Output timing is measured at 50% of signal amplitude.)

Table 1-1. Vector Output I/O Module Specifications

## VECTOR OUTPUT I/O MODULE OUTPUT (into 10 LSTTL loads with card edge connector attached): Maximum Vector Pattern (4 Modules) ......... 8192 vectors, 160 channels wide. Vector Looping ...... Up to 65536 repetitions of one vector set. Output Logic Levels: High ..... 3.7V minimum (6.0 mA source). Low ...... 0.4V maximum (6.0 mA sink). ppm). DR CLK (external clock) ...... 25 MHz maximum. (This frequency maximum may be exceeded in some cases based upon application and hardware interfacing.) Clock to Vector Out (tdel): INT CLK Out to Vector Out Delay ...... 37 ns typical, 45 ns maximum. DR CLK In to Vector Out Delay ...... 50 ns typical, 58 ns maximum.

#### Table 1-1. Vector Output I/O Module Specifications (cont.)

| WAIT (Handshake) Setup Time (twsu)                                                 | 42.5 ns maximum (35 ns typical) from WAIT acknowledgement until next clock cycle drives vector. If the setup time is not met, the next clock drives out the vector. Minimum WAIT pulse width is 10 ns.                                                                                                    |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Single Module Channel to Channel Skew*  Module to Module Channel Skew*  TRISTATE-: |                                                                                                                                                                                                                                                                                                           |

| Activation (txout)                                                                 | Output source/sink released 25 ns maximum (20 ns typical) after TRISTATE- goes low. Minimum TRISTATE- pulse width is 10 ns.                                                                                                                                                                               |

| Recovery (txsu)                                                                    | TRISTATE- must go high no later than 5 ns after the rising edge of the INT CLK or no later than 10 ns after the programmed edge of DR CLK for the vector to be output by that clock, otherwise that vector is only driven internally and the output is held tri-stated, effectively skipping that vector. |

| Output Series Termination                                                          | 33 Ohms                                                                                                                                                                                                                                                                                                   |

| INT CLK                                                                            | Capture Clock clocks 42.5 ns ±5 ns after the falling edge of INT CLK.                                                                                                                                                                                                                                     |

| DR CLK                                                                             | Capture Clock clocks 55 ns<br>±10 ns after non-clocking edge<br>of DR CLK (approximate 50% duty<br>cycle).                                                                                                                                                                                                |

| START, STOP, and ENABLE: START, STOP Pulse Width                                   | 10 ns minimum.                                                                                                                                                                                                                                                                                            |

| START Setup Time                                                                   | 30 ns minimum.<br>25 ns minimum.                                                                                                                                                                                                                                                                          |

<sup>\*</sup> Skew measurement assumes equal loading. Differences in capacitance may affect results.

<sup>\*\*</sup> Capture clock may be adjusted in approximate 15 ns steps by using the setoffset command (see the 9100 Series TL/1 Reference Manual).

Table 1-1. Vector Output I/O Module Specifications (cont.)

DR CLK START Setup Time ...... 20 ns minimum. STOP Setup Time ...... 20 ns minimum. ENABLE Setup Time ...... 15 ns minimum. ENABLE Hold Time ...... 35 ns minimum. Input Impedance: DR CLK ...... 40 kilohm minimum, 35 pF maximum. TRISTATE- ..... 40 kilohm minimum, 80 pF maximum. WAIT ..... 40 kilohm minimum, 50 pF maximum. VECTOR OUTPUT I/O MODULE INPUT: Input Impedance ...... 50 kilohm minimum, 90 kilohm typical; 100 pF maximum, 65 pF typical.\* Operating Voltage Range ..... -0.5V to +5.5V (all lines). Input/Output Protection ...... +10V/-5V for one minute maximum, one line only (all lines).

#### Input Thresholds:

| <br>  TTL<br> | CMOS |                         |

|---------------|------|-------------------------|

| <br>  5.0V    | 5.0V | \                       |

|               |      | >- Guaranteed HIGH      |

| 2.6V          | 3.4V | <                       |

| j             |      | >- HIGH or INVALID      |

| 2.1V          | 2.9V | <                       |

| j             |      | >- Guaranteed INVALID   |

| 1.0V          | 1.2V | <                       |

| j             |      | >- LOW or INVALID       |

| 0.6V          | 0.8V | <                       |

|               |      | <br>  >- Guaranteed LOW |

| 0.0v          | 0.0V | /                       |

|               |      |                         |

CLOCK, START, STOP, and ENABLE Inputs:

Thresholds:

<sup>\*</sup> Input capacitance includes the Y9100A-102 Card Edge Interface Module.

Table 1-1. Vector Output I/O Module Specifications (cont.)

```

Transition Counter:

Maximum Frequency ...... 10 MHz minimum.

Maximum Count (Transition Mode) ...... 8388608 (23 bits) counts

(+ overflow).

Frequency Accuracy (Frequency Mode) .... ±250 ppm ±2 Hz.

Stop Counter:

Maximum Frequency ..... 10 MHz.

Maximum Count ...... 65535 clocks.

Maximum Frequency ..... 10 MHz.

Minimum Pulse Width ..... 50 ns.

Timing for Synchronous Measurements:

Maximum Frequency of Clock ...... 10 MHz.

Maximum Frequency of Data ..... 5 MHz.

Data Hold Time ...... 30 ns minimum.

Minimum Pulse Width

(Start/Stop/Enable/Clock) ..... 50 ns.

Start Edge Setup Time

(before clock edge, for clock to

be recognized) ..... 0 ns minimum.

Stop Edge Setup Time

(before clock edge, for clock

edge to not be recognized) ..... 5 ns minimum.

Enable Setup Time

(before clock edge, for clock

edge to be recognized) ..... 0 ns minimum.

Enable Hold Time

(after clock edge, for clock

edge to be recognized) ...... 10 ns minimum.

Data Timing for Asynchronous Measurements:

Maximum Frequency ..... 10 MHz.

Minimum Pulse Width (HIGH or LOW) ..... 50 ns.

Minimum Pulse Width (tri-state) ...... 150 ns.

Data Compare Equal:

Minimum Pulse Width of

Data and Enable ..... 75 ns.

PHYSICAL SPECIFICATIONS

Operating Temperature:

5 to 27°C, 95% RH maximum (non-condensing).

27 to 40°C, RH decreasing linearly from 95% to 50% (non-condensing).

Storage/Shipping Temperature:

20 to 60^{\circ}C, 8% to 80% RH (non-condensing).

```

#### VECTOR OUTPUT I/O MODULE OVERVIEW

The 9100A-017 Vector Output I/O Module adds 40 lines of input and high-speed output capability to the 9100A/9105A mainframe. Up to four Vector Output I/O Modules may be connected to the mainframe for a maximum of 160 channels of vector output and stimulus measurement. Any number of the 160 channels may be used simultaneously.

The Vector Output I/O Module has the same input measurement capabilities as the 9100A-003 Parallel I/O Module. The Vector Output I/O Module is capable of generating cyclic redundancy checks (CRCs), measuring frequency or taking event counts, and recording logic level histories. The input measurements can be synchronized to the 9100A/9105A microprocessor-specific Pod, to external events (using the module external START, STOP, ENABLE, and CLOCK lines), to a software strobe, or to a free-running clock. The input section may also be synchronized to the output section by using the Capture Clock (a user-programmable clock generated during vector driving). The module also has a programmable "breakpoint" capability. The input thresholds may be set to either "TTL" and "CMOS" levels.

The Vector Output I/O Module can drive vector patterns synchronized to a user-supplied external clock (at up to 25 MHz), to a user-selectable internal clock at 1, 5, 10, or 20 MHz, to a software strobe, or to the Pod. The output can be latched to a level (either high or low) on any of the module's lines to test devices using either a "writeword" or "writepin" command. Each pin can be driven either high or low, or be tri-stated. An external input is available to provide handshaking synchronization with the UUT. All 40 outputs can be simultaneously tri-stated by an external signal.

The Vector Output I/O Module consists of two assemblies: the Main PCA (9100A-4021) and the Top PCA (9100A-4022).

The Main PCA provides the interface to the mainframe, and is used for input measurements. The Main PCA includes the inputs for the external synchronization lines START, STOP, ENABLE, and CLOCK. It also contains some support circuitry for vector driving, including:

- o bus interfacing circuitry for the Top PCA.

- o vector drive internal clock control.

- o vector loop control circuitry.

#### 2/Theory of Operation

- o vector drive status register.

- o six-pin jack for control signals for vector driving.

The Top PCA is used primarily for vector output, although it also provides the 40-channel input signals, Clip Module Connector Code, and ready button signals to the input section on the Main PCA. It also generates the Capture Clock (available as an input sync mode).

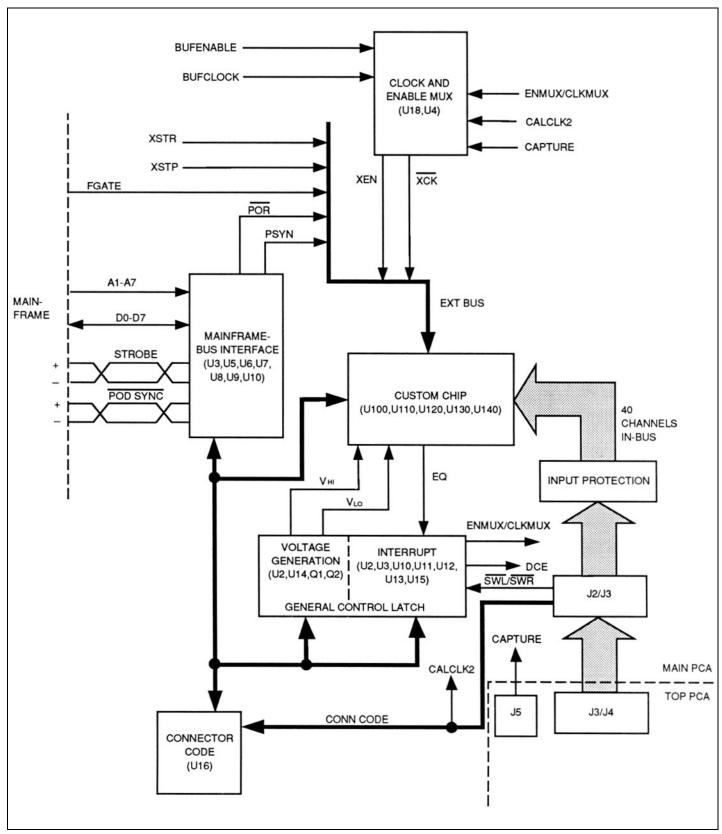

The input section of the Vector Output I/O Module consists of the following six functional blocks (See Figure 2-1):

- o Mainframe to Bus Interface Functional Block.

- o Custom Chip Functional Block.

- o Clock and Enable Mux Functional Block.

- o General Control Latch Functional Block.

- o Connector Code Functional Block.

- o Input Protection Functional Block.

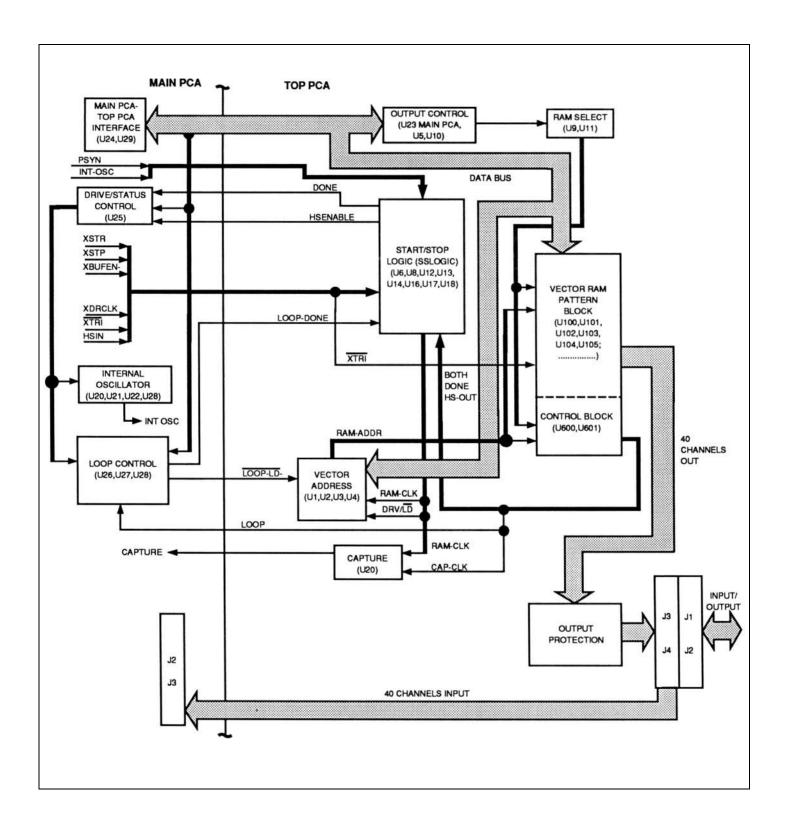

The output section consists of the following twelve functional blocks (See Figure 2-2):

- o Main PCA to Top PCA Interface Functional Block.

- o Internal Oscillator Control Functional Block.

- o Output Control Functional Block.

- o RAM Select Functional Block.

- o SSLOGIC (Start/Stop Logic) Functional Block.

- o Vector Address Functional Block.

- o Vector Pattern RAM Functional Block.

- o Vector Control RAM Functional Block.

- o Loop Control Functional Block.

- o Capture Clock Functional Block.

- o Drive Status Functional Block.

- o Output Protection Functional Block.

Figure 2-1. Input Section Functional Block Diagram

Figure 2-2. Output Section Functional Block Diagram

#### INPUT SECTION THEORY OF OPERATION

#### NOTE

All of the input section circuitry is located on the Main PCA unless otherwise indicated.

#### Mainframe to Bus Interface Functional Block

The bus interface block connects the 9100A/9105A mainframe microprocessor bus to the Vector Output I/O Module. The module is a memory-mapped device, with all control performed by writing to the module memory space. The control bus enters the module on connector J1 and consists of the following lines:

- o Seven address lines, Al through A7.

- o Eight data lines, D0 through D7.

- o Two differential strobe lines, STROBE+ and STROBE-.

- o One control line, R/W-.

The two mainframe strobe signals, STROBE+ and STROBE-, are translated by U9 into the module STROBE- signal. STROBE- is the key signal that qualifies all of the bus activities and is used by U7 to latch the addresses and R/W-, and to enable the data bus buffer. The STROBE- signal, in conjunction with the latched version of the R/W-, generates the read strobe (RD-) and the write strobe (WR-). The STROBE- signal and the decoder U6 provide address decoding by generating signals AD8-through ADE- and ALLCHIP-. Signals AD8- through ADC- and ALLCHIP- are input to AND Gates U3 and U5 to provide the custom chip selects CS0-through CS4-. Signals ADD- and ADE- are used as register select lines.

(The mainframe STROBE- signal has already had some amount of address decoding. STROBE- for any particular module is only active on accesses to addresses DXXXX, with address bit 0 = 1, and with the proper "hot bit" identifying the module. See the heading, "Mainframe Addressing of the Module", further on in this section for more information on hot-bit decoding).

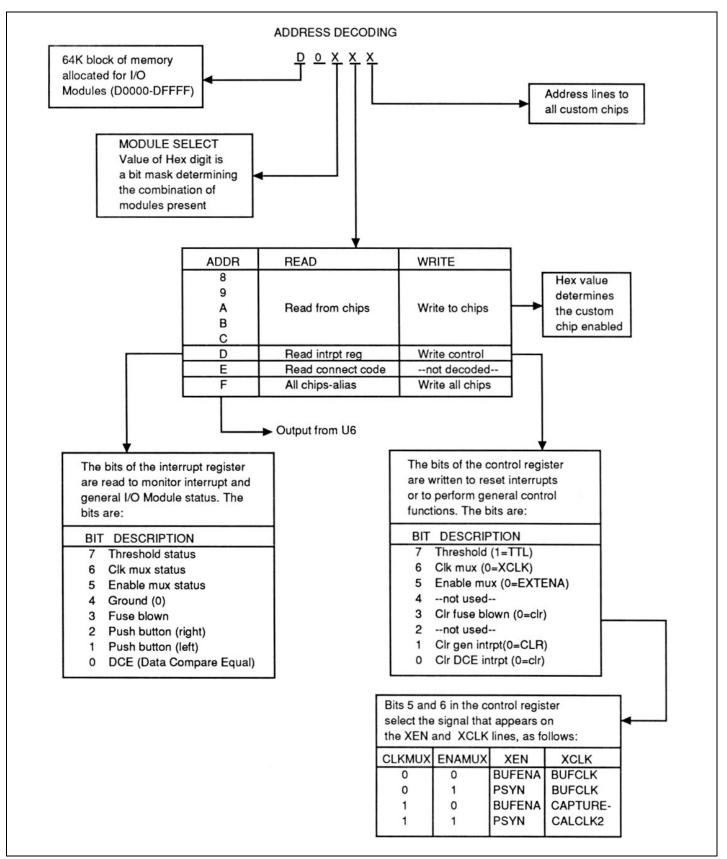

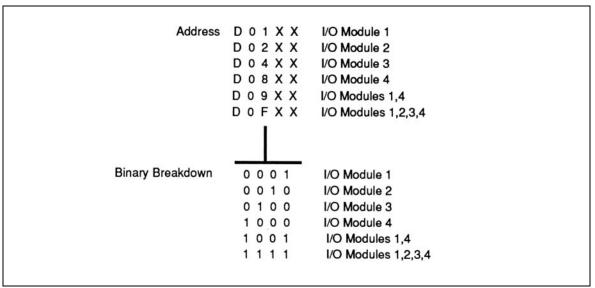

#### MAINFRAME ADDRESSING OF THE MODULE

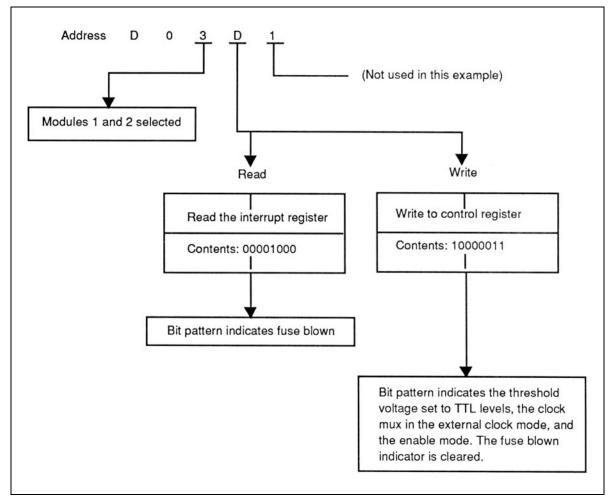

Memory reserved for module control occupies the mainframe addresses \$D0000 through \$DFFFF. Out of this 64K-byte block, four modules can be addressed. Lower Data Strobe (LDS-) on the mainframe qualifies all module addresses; thus address bit 0 is effectively a 1. Addresses within this space using Upper Data Strobe (UDS-) are unused. Figure 2-3 shows a summary of module input section address decoding. Figure 2-4 provides an addressing example.

Each of the four modules is controlled via "hot-bit decoding" of the mainframe address lines A8 through All. This method of decoding allows any combination of modules to be addressed simultaneously. Figure 2-5

#### 2/Theory of Operation

shows the third least significant digit of the 5-digit hex module address broken down into binary format. The position of the set bit(s) determines the module(s) to be addressed.

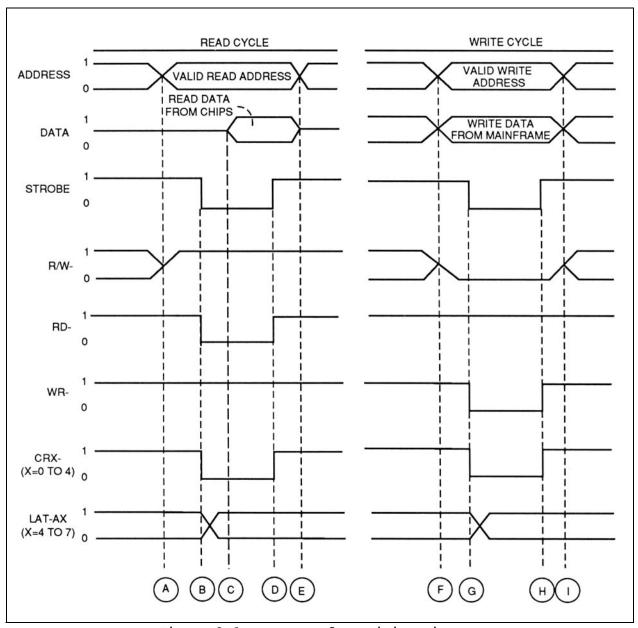

The Vector Output I/O Module bus interface timing diagram (Figure 2-6) shows the signals contained in the bus interface block during a read and write cycle. Each transition point (indicated by the letters A through I) designates the following actions:

- A. The address appears on the bus. R/W- goes high, signifying a read cycle.

- B. STROBE- goes low, allowing RD- and CSX- to go active. Data bus transceiver U8 turns on, driving data from the module to the mainframe. Addresses and R/W- are latched by U7 and are guaranteed valid.

- C. Valid read data appears on the data bus.

- D. STROBE-, RD-, and CSX- return high. Read data is guaranteed valid at this point.

- E. End of the read cycle.

- F. The address appears on the bus. R/W- goes low, signifying a write cycle.

- G. STROBE- goes low, allowing WR- and CSX- to go active. Data bus transceiver U8 turns on, receiving data from the mainframe to the module. Addresses and R/W- are guaranteed valid.

- H. STROBE-, WR-, and CSX- return high. Write data is latched into the module registers.

- I. End of the write cycle.

#### CUSTOM CHIP SELECTION

The Bus Interface also decodes address lines A1 through A7 from the mainframe to determine which custom chips are enabled. As the address signals enter the Main PCA through J1, the address lines are latched by U7 (the latch signal is STROBE-). Address lines A7 through A4 are used as address inputs for the decoder (U6). The outputs of U6 are gated to determine which custom chip is enabled. Any one of the five custom chips can be addressed, or all five of the chips can be addressed simultaneously (no other combination of the custom chips can be addressed within a module).

For example, to select custom chip U100, the input at U7-13 (A7) from the address bus of the mainframe must be at logic high and U7-18 (A4), U7-17 (A5), and U7-14 (A6) must be at logic low. When STROBE- occurs, U7 latches the logic levels on these pins. On the output lines of U7, LAT-A7 is set at logic high, and LAT-A4, LIT-A5, and LAT-A6 are logic

Figure 2-3. Input Section Address Decoding Summary

Figure 2-4. Address Decoding Example

low. U6 decodes the latched address lines and sets output line AD8- low. The logic low on AD8- is gated through U5 and sets up a logic low on CS0-, thereby enabling custom chip U100. To select custom chip U100 on Module 3, the address \$D0481\$ is used.

A custom chip may be addressed individually, or all custom chips may be addressed simultaneously. Address bits A4 through A7 determine the custom chip selection. To address all chips, an address in the form \$DXXFX must be used (X means don't care). This address causes the ALLCHIP- signal (U6-7) to go active, which when gated through U5 and U3, makes all five chip selects CSO- through CS4- active.

#### Custom Chip Functional Block

The custom chips each contain eight channels of data acquisition. Each channel performs 16-bit Cyclic Redundancy Checking (CRC), 23-bit (with overflow) transition counting, 3-bit asynchronous level history recording, 3-bit synchronous level history recording, and 1-bit data comparison. The custom chips are used for module control, and are

Figure 2-5. Hot-Bit Decoding Examples

connected to the data bus via U8. Eleven internal registers control each custom chip. These registers are in turn controlled by address lines A1 through A3 and the R/W- line.

The pin-out of the custom chip is shown in Table 2-1.

#### Clock and Enable Mux Functional Block

The Clock and Enable Mux block is located on the Main PCA and is shown in the Input Section Functional Block Diagram, Figure 2-1. Two ICs make up this block: the 74HCT153 Dual 4:1 Multiplexer (U18) and the 74HCT04 Hex Inverter (U4). This block selects one of three sources for the XCK-signal, and one of two sources for the XEN signal.

CLOCK AND ENABLE MUX OPERATION

#### Inputs

The Clock and Enable Mux block clock sources include BUFCLOCK, CAPTURE-, and CALCLK2. BUFCLOCK originates from the CLOCK external synchronization line. CAPTURE- is a user-programmable clock generated on the Top PCA by the output section during vector driving. CAPTURE is routed to the Main PCA through J4-29 where it is inverted by U19 and sent to U18-12. CALCLK2, which is generated during calibration, enters the Main PCA on J2-24 and is routed to U18-13.

The POD SYNC signal, which enters the module as a differential ECL signal, is converted by U9 into the TTL level signal PSYN. This signal enters the EXT-BUS and is directly applied to the custom chips as a clocking source, to U18 as an enabling signal, and to the Top PCA through J4 pin 1 as a vector output clock source.

Figure 2-6. Bus Interface Timing Diagram

The Clock and Enable Mux block enable sources include BUFENABLE, a signal that originates from the external ENABLE synchronization line, and PSYN (described in the previous paragraph).

The CALCLK2 signal enters the Main PCA through the Connector Code block. Channels 1 through 39 are tied together and to CALCLK2 when the Calibration Module is plugged in. CALCLK2 is an input to U18-13. The ENMUX and CLKMUX signals are generated by the Control Register (U14-15 and U14-16, respectively) and are control inputs to U18. U18 generates outputs XEN and XCK. Table 2-2 shows which signals appear on the outputs of the multiplexer for all four states of the control inputs.

Table 2-1. Custom Chip Pin Description

| PIN     | TYPE         | FUNCTION                             |  |

|---------|--------------|--------------------------------------|--|

| A0-A2   | Input        | Address Lines                        |  |

| POR-    | Input        | Power-On Reset                       |  |

| SRCK    | Input        | 1 MHz Serial-To-Parallel             |  |

|         |              | Conversion Clock                     |  |

| VDD1    | Input        | Positive Voltage Supply              |  |

| VDD2    | Input        | Positive Voltage Supply              |  |

| GND1    | Input        | Logic Common                         |  |

| GND2    | Input        | Logic Common                         |  |

| XD0-XD7 | Input/Output | Microprocessor Data Bus              |  |

| EQ      | Output       | Equal (Data Comparison Equal) Output |  |

| TC      | Output       | Test Clock Output                    |  |

| WR-     | Input        | Write Enable                         |  |

| RD-     | Input        | Read Enable                          |  |

| CS-     | Input        | Chip Select                          |  |

| VPAT    | Input        | Negative Supply for DRV Outputs      |  |

| TEN     | Input        | Test Mode Enable                     |  |

| XSTP    | Input        | External Stop                        |  |

| GATE    | Input        | Frequency Gate                       |  |

| XSTR    | Input        | External Start                       |  |

| XEN     | Input        | External Enable                      |  |

| XCK     | Input        | External Clock                       |  |

| PSYN    | Input        | Pod Sync Clock                       |  |

| VLO     | Input        | Logic Low Threshold Reference        |  |

|         |              | Voltage for Inputs CD0-CD7           |  |

| VHI     | Input        | Logic High Threshold Reference       |  |

|         |              | Voltage for Inputs CD0-CD7           |  |

| CD0-CD7 | Input*       | Channel Inputs                       |  |

| TLI     | Input        | Test Channel Comparator Input        |  |

| TLO     | Output       | Test Channel Comparator Output       |  |

<sup>\*</sup> CDn inputs have an internal resistor network to control the voltage at which they will float (the "invalid" voltage). This voltage is approximately 1.6 V, through an effective resistance of >50 kilohms.

#### Outputs

The Clock and Enable MUX block outputs the XEN and XCK- signals to the EXT-BUS. These two control signals are sent to each custom chip. Three parallel inverters invert the XCK signal from U18-9, and ensure a fast rise time into the relatively high capacitance XCK- line.

#### General Control Latch Functional Block

The General Control Latch Block, located on the Main PCA, varies input thresholds, clears fault conditions, and controls the Clock and Enable Multiplexer. Figure 2-1 shows the block's functional relationship on the

Table 2-2. Clock and Enable Mux Truth Table

| Contr  | ol In  | Output    | ts       |

|--------|--------|-----------|----------|

| CLKMUX | ENAMUX | XEN       | хск      |

| _      | •      |           |          |

| 0      | 0      | BUFENABLE | BUFCLOCK |

| 0      | 1      | PSYN      | BUFCLOCK |

| 1      | 0      | BUFENABLE | CAPTURE- |

| 1      | 1      | PSYN      | CALCLK2  |

block diagram. The ICs in this block include: a 74HC273 8-Bit Latch (U14), an LM324 Quad Op-Amp (U2), two 2N3906 PNP transistors (Q1, Q2), a 74HC08 Quad 2-Input AND Gate (U3), a 74LS30 8-Input NAND Gate (U15), two 74LS112 Dual JK Negative-Edge-Triggered Flip-Flops (U11, U12), a 74HCT32 Quad 2-Input OR Gate (U10), and a 74HCT244 Octal Buffer (U13).

#### CONTROL REGISTER

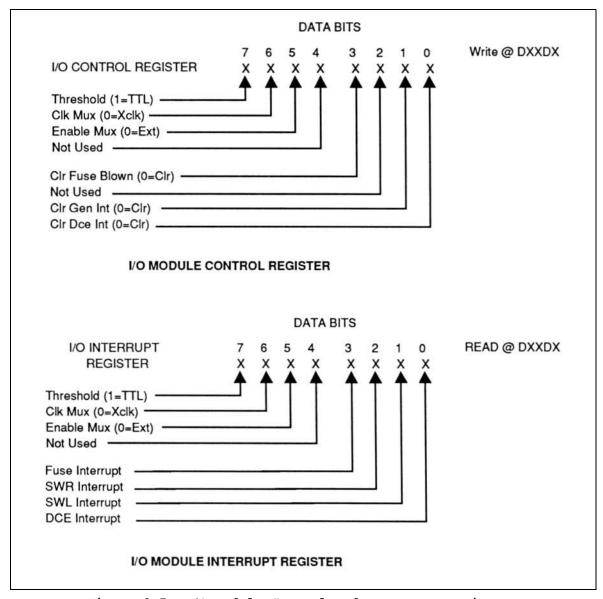

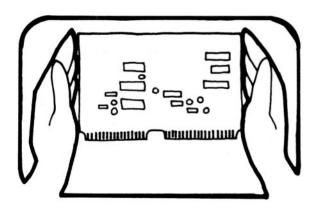

Data lines from the A-D-BUS to U14 produce the DCECLR- (Data Compare Equal Clear), GENCLR- (General Clear), FUSECLR- (Fuse Clear), ENMUX (Enable Multiplex), CLKMUX (Clock Multiplex), and THRSH (Threshold) signals. U14 is accessed by a write to \$DXXDX, where the ADD- and WR-signals latch data into U14. The Control Register (U14) is cleared by a PWRUP (Power Up) signal held low by C44 to ensure a proper reset. See Figure 2-7 for the Control Register bit position.

The J2 and J3 connectors provide the input to the General Control Latch block for detection of Clip and Calibration Modules. J2-25 and J3-25 are the input pins to a detection circuit that provides SWLDET (the left-hand or A Switch Detect) and SWRDET (the right-hand or B Switch Detect) signals to generate an interrupt. The mainframe reads the interrupt register (U13) to determine the reason for an interrupt. See Figure 2-7 for the interrupt register bit positions.

#### DATA COMPARISON INPUTS

All 40 lines of the module are compared to programmable data registers and are qualified by programmable "don't care" registers. The comparison is done inside the custom chip(s) between the data on the input lines and the registers, eight lines per chip. The EQ outputs (pin 55 of the custom chip) are gated together by U15, and, when they are all high (i.e., a comparison for all five chips has been detected), an interrupt is generated and is input to the interrupt register (U13).

#### FUSE DETECTION

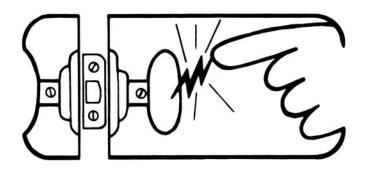

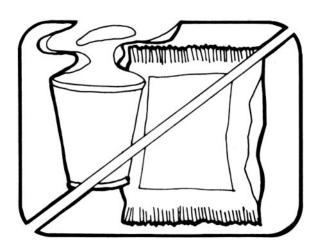

The FUSEDET (Fuse Detect) signal is part of the Multi-Detection area of the General Control Latch Block. A 1A slow-blow ground fuse located on

the module Main PCA protects the ground line. The FUSEDET signal becomes an input to the interrupt register (U13-8), along with the other detection signals.

#### DATA COMPARISON AND GENERAL INTERRUPTS

The General Control Latch block outputs detection and interrupt signals for any problems or special operations of the module. An external DCE pin is also available for use as a "hardware interrupt".

The following two interrupts are produced by the General Control Latch block:

- o DCEINT- (Data Compare Equal Interrupt).

- o IOGENINT- (I/O General Interrupt).

#### The Data Compare Interrupt

DCEINT- is generated by the module when the programmed data compare registers match the input data. The DCEINT- signal originates from the EQ pin of each custom chip. The EQ signals are gated to form a DCE-signal. The DCE- signal triggers a J-K flip-flop to produce the DCEDET and DCEINT- signals.

#### The I/O General Interrupt

IOGENINT- is an interrupt generated by the module when either pushbutton on a clip module is pressed. The interrupt register on the module must be read to determine the cause. In the case of a button push, two J-K flip-flops output the SWLDET (A side) and SWRDET (B side) signals. These signals are gated to produce the IOGENINT- signal.

#### DATA COMPARE EQUAL OUTPUT PIN

DCE output pin P1-6 can be used to trigger a logic analyzer or oscilloscope. Buffers and protection circuitry safeguard the DCE signal output.

#### OPERATION OF GENERAL CONTROL LATCH BLOCK

The General Control Latch block is divided into three areas. These areas produce voltages for module operation and contain circuitry that generates detection for a blown fuse. The functional block contains the following areas:

- o Threshold Voltage Detection.

- o Multi-Detection and Interrupt.

- o Fuse Blown Detection.

Threshold Voltage Generation

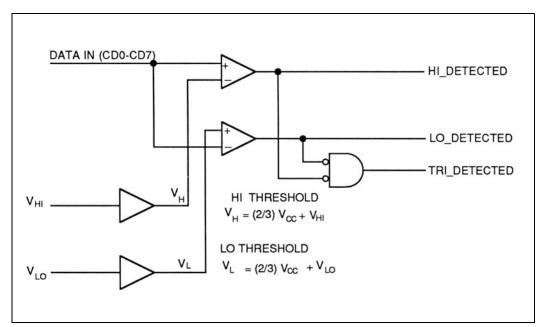

Threshold Voltage Generation produces the threshold voltages necessary for the custom chips to classify input logic levels. Data bit 7 of the command register (U14) determines the level of the threshold, with a 1 selecting TTL, and a 0 for CMOS.

Figure 2-7. I/O Module Control and Interrupt Registers

The threshold (THRSH) signal output of U14-19 controls the circuitry that produces a low voltage level (VLO) and a high voltage level (VHI). These voltage levels are used by the custom chip pins 39 and 45 to define the logic low, invalid, and logic high voltage ranges. A logic high out U14-19 designates a TTL logic level and a logic low a CMOS logic level. The THRSH signal controls resistor dividers that create the VHI and VLO signals. Two parts of op amp U2 and transistors Q1 and Q2

together provide a regulated output with high current sinking capability. Typical current seen by these regulators can vary from 10 to 40~mA. The approximate VHI and VLO levels generated are listed in Table 2-3.

Table 2-3. VHI and VLO for TTL and CMOS Logic Levels

| DESC        | THRSH | VHI              | ATO |

|-------------|-------|------------------|-----|

| TTL<br>CMOS | 1     | -1.05V<br>-0.25V |     |

A voltage level-detection system in the custom chip uses data inputs, VHI, and VLO voltage levels to detect a high voltage input, a low voltage input, or a tri-state condition. See Figure 2-8 for an illustration of the detection circuitry contained in the custom chip.

#### NOTE

The actual input thresholds for the high and low comparators are computed from the formulas shown in Figure 2-8.

Figure 2-8. Custom Chip Voltage Level Detection

#### Multi-Detection and Interrupt

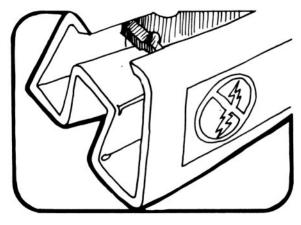

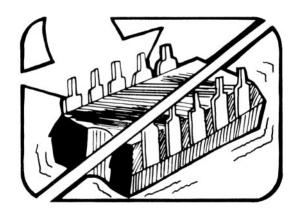

The Vector Output I/O Module accepts different sizes of clip modules. A detection system within the module informs the mainframe as to the size of the clip that has been installed on the module. Clip modules are available in a half-size module and a full-size module. The half-size module plugs into one connector (either J1 or J2 on the Top PCA), and

#### 2/Theory of Operation

the full-size module plugs into both connectors (both J1 and J2 on the Top PCA). Together, the clip(s) plugged into both J1 and J2 of the Top PCA generate an 8-bit code that can be decoded by the mainframe to identify the size of the installed clip module(s).

#### Fuse Blown Detection

Detection of blown fuses is performed by two LM324 Op-Amps (U2) and one part of U3 configured as a window detector. If the XGND signal exceeds a +100 millivolt window, U3-6 will go low, forcing the FUSEDET line to go high. When the interrupt register is read (READ 0 \$DXXDX), a 1 in bit 3 indicates the fuse is blown. This blown fuse indication is cleared by writing to the I/O Command Register (WRITE 0 \$DXXDX) with a data value that has bit 3 = 0.

#### Connector Code Functional Block

The components associated with the Connector Code block are the 74 HCT 244 Octal Buffer/Line Driver (U16) and part of the J2 and J3 connectors. This block is located on the Main PCA as indicated on the functional block diagram shown in Figure 2-1.

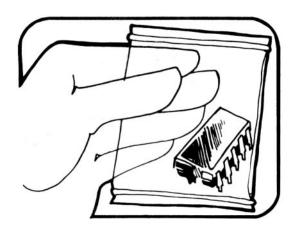

The mainframe determines which Clip Module the user has installed by reading and decoding connector codes encoded in each Clip Module. To read the code, the mainframe performs a read at \$DXXE1. This operation generates the ADE- signal, which in turn enables U16, placing the code on the data bus. Of the eight bits read, the lower four bits refer to the "A side", and the upper four bits refer to the "B side". Thus, differentiation is possible for 16 different conditions on each side of the module. Clips that use up an entire module use an 8-bit code. The most significant nybble of these codes is 1110. A list of these codes is shown in Table 2-4. For example, to determine the connector codes on module 3, a Read 0 \$D04E1 should be performed. Table 2-5 presents some examples of codes and their interpretation.

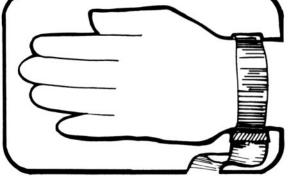

#### Input Protection Functional Block

The input protection circuit clamps overvoltage, undervoltage, and static conditions before they reach the custom chip. The signals from the I/O lines enter the Main PCA through connectors J2 and J3. Each line passes through a 100 ohm current-limiting resistor. The lines are then routed to the custom chip inputs. Also attached to the lines are BAV99 diode packs; one diode is tied to +5 volts and the other is tied to ground to clamp any input above +5 volts or below ground.

#### OUTPUT SECTION THEORY OF OPERATION

NOTE

All the output section circuitry is located on the Top PCA unless otherwise indicated.

Table 2-4. Dip-Clip and Calibration Module Configuration Codes

| 4-BIT CODE                                                                                                                                             | MEANING                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000                                                                                                                                                   | 14-Pin Clip                                                                                                                                                                                                             |

| 0001                                                                                                                                                   | 16-Pin Clip                                                                                                                                                                                                             |

| 0010                                                                                                                                                   | 18-Pin Clip                                                                                                                                                                                                             |

| 0011                                                                                                                                                   | 20-Pin Clip                                                                                                                                                                                                             |

| 0100                                                                                                                                                   | 24-Pin Clip                                                                                                                                                                                                             |

| 0101                                                                                                                                                   | (reserved)                                                                                                                                                                                                              |

| 0110                                                                                                                                                   | Used as most significant byte of calibration header                                                                                                                                                                     |

| 0111                                                                                                                                                   | (reserved)                                                                                                                                                                                                              |

| 1000                                                                                                                                                   | (reserved)                                                                                                                                                                                                              |

| 1001                                                                                                                                                   | (reserved)                                                                                                                                                                                                              |

| 1010                                                                                                                                                   | (reserved)                                                                                                                                                                                                              |

| 1011                                                                                                                                                   | (reserved)                                                                                                                                                                                                              |

| 1100                                                                                                                                                   | (reserved)                                                                                                                                                                                                              |

| 1101                                                                                                                                                   | 20-Pin Flying Lead Set                                                                                                                                                                                                  |

| 1110                                                                                                                                                   | Full width connector, use other 4 bits for ID                                                                                                                                                                           |

| 1111                                                                                                                                                   | No Clip Installed                                                                                                                                                                                                       |

|                                                                                                                                                        |                                                                                                                                                                                                                         |

| 8-BIT CODE<br>7654 3210                                                                                                                                | MEANING                                                                                                                                                                                                                 |

| 7654 3210                                                                                                                                              |                                                                                                                                                                                                                         |

| <b>7654 3210</b> 1110 0000                                                                                                                             | 28-Pin Clip                                                                                                                                                                                                             |

| 7654 3210<br>1110 0000<br>1110 0001                                                                                                                    | 28-Pin Clip<br>40-Pin Clip                                                                                                                                                                                              |

| 7654 3210<br>1110 0000<br>1110 0001<br>1110 0010                                                                                                       | 28-Pin Clip<br>40-Pin Clip<br>Calibration Header                                                                                                                                                                        |

| 7654 3210<br>1110 0000<br>1110 0001<br>1110 0010<br>0110 0010                                                                                          | 28-Pin Clip<br>40-Pin Clip<br>Calibration Header<br>Calibration Header                                                                                                                                                  |

| 7654 3210<br>1110 0000<br>1110 0001<br>1110 0010                                                                                                       | 28-Pin Clip<br>40-Pin Clip<br>Calibration Header<br>Calibration Header<br>(reserved)                                                                                                                                    |

| 7654 3210<br>1110 0000<br>1110 0001<br>1110 0010<br>0110 0010<br>1110 0011<br>1110 0100                                                                | 28-Pin Clip 40-Pin Clip Calibration Header Calibration Header (reserved) (reserved)                                                                                                                                     |

| 7654 3210  1110 0000 1110 0001 1110 0010 0110 0010 1110 0101 1110 0100 1110 0101                                                                       | 28-Pin Clip 40-Pin Clip Calibration Header Calibration Header (reserved) (reserved) (reserved)                                                                                                                          |

| 7654 3210<br>1110 0000<br>1110 0001<br>1110 0010<br>0110 0010<br>1110 0011<br>1110 0100                                                                | 28-Pin Clip 40-Pin Clip Calibration Header Calibration Header (reserved) (reserved)                                                                                                                                     |

| 7654 3210  1110 0000 1110 0001 1110 0010 0110 0010 1110 0101 1110 0101 1110 0101                                                                       | 28-Pin Clip 40-Pin Clip Calibration Header Calibration Header (reserved) (reserved) (reserved) (reserved)                                                                                                               |

| 7654 3210  1110 0000 1110 0001 1110 0010 0110 0010 1110 0101 1110 0101 1110 0110 1110 0111                                                             | 28-Pin Clip 40-Pin Clip Calibration Header Calibration Header (reserved) (reserved) (reserved) (reserved) (reserved)                                                                                                    |

| 7654 3210  1110 0000 1110 0001 1110 0010 0110 0010 1110 0101 1110 0101 1110 0110 1110 0111 1110 1000                                                   | 28-Pin Clip 40-Pin Clip Calibration Header Calibration Header (reserved) (reserved) (reserved) (reserved) (reserved) (reserved) (reserved)                                                                              |

| 7654 3210  1110 0000 1110 0001 1110 0010 0110 0011 1110 0100 1110 0101 1110 0110 1110 0111 1110 1000 1110 1001                                         | 28-Pin Clip 40-Pin Clip Calibration Header Calibration Header (reserved) (reserved) (reserved) (reserved) (reserved) (reserved) (reserved) (reserved)                                                                   |

| 7654 3210  1110 0000 1110 0001 1110 0010 0110 0010 1110 0101 1110 0101 1110 0110 1110 0111 1110 1000 1110 1001 1110 1001                               | 28-Pin Clip 40-Pin Clip Calibration Header Calibration Header (reserved) (reserved) (reserved) (reserved) (reserved) (reserved) (reserved) (reserved) (reserved)                                                        |

| 7654 3210  1110 0000 1110 0001 1110 0010 0110 0010 1110 0101 1110 0101 1110 0110 1110 1011 1110 1000 1110 1001 1110 1001 1110 1010                     | 28-Pin Clip 40-Pin Clip Calibration Header Calibration Header (reserved)                                  |

| 7654 3210  1110 0000 1110 0001 1110 0010 0110 0010 1110 0101 1110 0101 1110 0110 1110 1010 1110 1000 1110 1001 1110 1000 1110 1010 1110 1010 1110 1010 | 28-Pin Clip 40-Pin Clip Calibration Header Calibration Header (reserved) |

#### Main PCA to Top PCA Interface Functional Block

Communication from the Main PCA to the Top PCA operates similarly to the mainframe to Bus Interface Functional Block (as described earlier in the input section). The latched address lines LAT-A4 through LAT-A7 are routed to the Top PCA through J4 (Main PCA) to J5 (Top PCA). The STROBE-

Table 2-5. Connector Code Examples

| alin on B gido 20 nin alin on A gido       |

|--------------------------------------------|

| clip on B side, 20-pin clip on A side      |

| -pin clip on B side, no clip on A side     |

| -pin clip installed                        |

| -pin clip on B side, 24-pin clip on A side |

| clips installed                            |

|                                            |

qualified RD- and WR- are also available to the output section. However, there is a separate data bus for the output section that is selected when LAT-A7 is low.

Two ICs are required to perform the data bus interfacing: a 74ALS245 Octal 3-State Transceiver (U24) and the 74LS31 delay elements (U29). Both devices are located on the Main PCA.

The TOPDATA Bus (used by the output section) is isolated from A-D-BUS (used by the input section) by U24. If a read or write access is made to any address of the output section (A7 = 0), LAT-A7 remains low, thereby providing an enable signal to U24 pin 19 (G-). The WR- signal determines the direction of data travel. If WR- is high, the data passes from the TOPDATA bus to A-D-BUS for a read. If WR- is low, the data passes in the other direction for a write.

Some register control signals (such as COMMANDO- and COMMANDO- for U5 and U6 of the Top PCA) use the rising edge of WR- to latch data. Since the WR- signal also controls the direction of the TOPDATA bus through }U24, U29 provides a nominal 46.5 ns delay to the direction control signal (WR-DLY-) on U24. This insures that, during accesses to the output section, the data bus is held in the correct direction by U24 while the rising edge of RD- or WR- latches the data.

#### ADDRESSING

All addresses with A7 low are reserved for the output section. Since A3 through A1 only go to the custom chips for use as addresses and STROBEis only active for addresses with LDS- active (address bit 0 = 1), the address space is effectively limited to \$DOX01 through \$DOX71.

Table 2-6 lists the output section addresses and the signals (or registers) that are affected by accessing the address for both reads and writes.

Performing a write to \$DOX01 causes the COMMANDO- output of U10 (Top PCA) to toggle, thereby latching the data on the bus into the U5 register. (See the heading, "Output Control Functional Block", further on in this section for more information.) When a read is performed at this address, the Vector Drive Status Nybble is returned from U25 (Main PCA). (See the heading, "Drive Status Functional Block", further on in this section and Table 2-10 for more information.)

Table 2-6. Vector I/O Module Output Section Address Map

| ADDRESS | WRITE                              | READ                       |

|---------|------------------------------------|----------------------------|

| \$DOX01 | COMMANDO-                          | Vector Drive Status Nybble |

| \$DOX11 | COMMAND1-                          |                            |

| \$DOX21 | Drive Register 2 (U25)             |                            |

| \$DOX31 | Loop Counter Load (LCLO- or LCHI-) |                            |

| \$DOX41 | RAM-PORT-                          | RAM-PORT-                  |

| \$D0X51 | RAM-STROBE                         |                            |

| \$DOX61 | LOAD-RAM-HI-                       |                            |

| \$DOX71 | LOAD-RAM-LO-                       |                            |

Performing a write to \$DOX11 toggles the COMMAND1- output of U10 (Top PCA), thereby latching the data on the bus into the U6 register. Performing a read at this address has no effect. See the Table 2-9 for more information.

Performing a write to \$DOX21 selects U25 (Main PCA) by address decoding and latches the data on the bus into Drive Register 2 on U25. Performing a read at this address has no effect. See the headings, "Internal Oscillator Control Functional Block", the "Loop Control Functional Block", and Table 2-7 for more information.

Performing a write to \$DOX31 toggles either LCLO- or LCHI- of U25 (Main PCA), depending on the state of bit 3 of Drive Register 2 on U25, thereby loading the least significant byte (LSB) or most significant byte (MSB) of the loop count into U26 or U27. Performing a read at this address has no effect. See the heading, "Loop Control Functional Block", and Table 2-7 for more information.

Performing a read or a write to \$DOX41 toggles the RAM-PORT- output of U10 (Top PCA), thereby incrementing the chip counter U9 and updating which SRAM is selected by U11. The actual data returned by a read is disregarded.

Performing a write to DOX51 toggles the RAM-STROBE output of U10 (Top PCA). This output can be used as a software-controlled clock for driving vectors. Performing a read at this address has no effect.

Performing a write to \$DOX61 toggles the LOAD-RAM-HI- output of U10 (Top PCA), thereby latching the data on the bus into the upper byte register U3 of the Loop-Back Address. Performing a read at this address has no effect.

Performing a write to \$DOX71 toggles the LOAD-RAM-LO- output of U10 (Top PCA), thereby latching the data on the bus into the lower byte register U4 of the Loop-Back Address. Performing a read at this address has no effect.

#### Internal Oscillator Control Functional Block

The Vector Output I/O Module contains a 1, 5, 10, and 20MHz internal clock source that is available for vector driving. The desired clock can be selected by writing to Drive Register 2 (U25) of the Main PCA (\$DOX21) and specifying bits 1 and 0.

The Internal Oscillator Control Functional Block consists of a 20 MHz Oscillator (U20), a 70HCT390 Dual Decade Ripple Counter (U21), a 74HC74 D-Type Flip-Flop (U28), and a 74AC151 8-Input Multiplexer (U22), all located on the Main PCA.

Writing to U25 (\$DOX21) using bit 1 and bit 0 selects the frequency of the internal clock. Outputs BMUX1 and BMUX0 from U25 to U22 control the selection of one of four clocks (see Table 2-7). These clocks are 20 MHz (obtained directly from the 20 MHz Oscillator U20), 10 MHz (obtained from U21 by dividing the 20 MHz clock by two), 5 MHz (obtained by dividing the 10 MHz clock by two using U28), and 1 MHz (obtained by dividing the 10 MHz clock by ten using U21). The Y output of U22 pin 5 goes directly to the Top PCA and is used by the SSLOGIC Functional Block as one vector driving clock source. The Y- output from U22 pin 6 is inverted by U19. This inversion gives OSC-CLK the same phase as the INT-OSC output and delays it slightly to reduce the clock to vector-out skew before being routed to the P1 pin 5 INT OSC output.

Table 2-7. U25 Drive Register 2 Bit Description (Write @ \$D0X21)

| віт     | SIGNAL   |           | 1          | 0       |  |

|---------|----------|-----------|------------|---------|--|

| 7,6,5,4 |          |           |            |         |  |

| 3       | LCHI-/LC | LO-       | LCHI-      | LCLO-   |  |

| 2       | LTCCLR-  |           | NO LTCCLR- | LTCCLR- |  |

| 1       | BMUX1*   |           |            |         |  |

| 0       | BMUX0*   |           |            |         |  |

| *BMUX1  | *BMUX0   | FREQUENCY |            |         |  |

| 0       | 0        | 10 MHz    |            |         |  |

| 0       | 1        | 20 MHz    |            |         |  |

| 1       | 0        | 5 MHz     |            |         |  |

| 1       | 1        | 1 MHz     |            |         |  |

#### Output Control Functional Block

The U10 PAL provides the majority of the output section control. It provides the latching signals COMMANDO- and COMMANDO- to U5 and U6. It provides the RAM-PORT- signal that controls the chip counter U9 and the RAM Select U11 PAL. It decodes writes to \$D0X51 to generate RAM-STROBE, which provides the soft-clocking ability for vector output. It supplies

the LOAD-RAM-HI- and LOAD-RAM-LO- signals that control the Vector RAM Address Functional Block. For more information on the available addresses and the signals they affect, see Table 2-6. Table 2-8 illustrates the U5 register bits used by the Output Control Functional Block.

U10 also provides the START-ENA signal to the SSLOGIC Functional Block. There are two conditions by which this signal can be made active. If the CO-START output of U5 is low, setting bit 0 to a 1 when writing to \$DOX11 sets START-ENA high. If the CO-START output of U5 is set high, START-ENA is not set high until RECV-ARM- is low.

The RECV-ARM- signal comes from the Main PCA and is generated by U23 (74HCT138). RECV-ARM- goes low when ALLCHIP- is low, D0 is low, D1 is high, and A1 through A3 are low (i.e., the input section is armed). This permits the input section to be armed at the same time the output section receives the START-ENA, so that both input and output sections can be started simultaneously.

To clear START-ENA, the CO-START line must be set low and a WRITE @ \$D0X11\$ must be performed with bit 0 set to 0.

Table 2-8. U5 Register Bit Description (Write @ \$D0X01)

| віт | SIGNAL       | 1                 | 0              |

|-----|--------------|-------------------|----------------|

| 7   | LOAD-RAM-    | No Load RAM       | Load RAM       |

| 6   | COUNTER-ENA- | No Counter Enable | Counter Enable |

| 5   | HSIN-POL-    | Falling Edge      | Rising Edge    |

| 4   | CO-START     | Co-Start          | No Co-Start    |

| 3   | DRV/LD-      | Drive             | Load           |

| 2   | MUX2*1       |                   |                |

| 1   | MUX1*        |                   |                |

| 0   | MUX0*        |                   |                |

| *MUX2 | *MUX1   | *MUXO | CLOCK      |

|-------|---------|-------|------------|

|       |         |       |            |

| 0     | 1       | 1     | INT-OSC    |

| 1     | 0       | 0     | PSYN       |

| 1     | 0       | 1     | RAM-STROBE |

| 1     | 1       | 0     | DR CLK     |

| 1     | 1       | 1     | DECREMENT  |

|       | (other) |       | Ground     |

|       |         |       |            |

#### RAM Select Functional Block

The high-speed 30 ns  $8K \times 8$  SRAM in the module must be accessed when loading vector files, when driving vector patterns, and when setting the

#### 2/Theory of Operation

module output to an unchanging state. There are two methods by which the Vector Pattern RAM and the Vector Control RAM can be selected:

- o To drive vectors, the DRV/LD- signal must be set high by performing a write to the U5 register 0 (\$D0X01) with bit 3 set high. This causes all outputs of U11 (BYTE0- through BYTE9-) and the BYTE10- output of U10 to be low, thereby selecting all vector RAM.

- o To load the Vector Pattern and Control RAM, the DRV/LD- signal must be set low by performing a write to the U5 register (\$D0X01) with bit 3 set low. Only the RAM addressed by the chip counter U9 is selected.

#### CHIP COUNTER OPERATION

The output of the chip counter is decoded by U10 and U11 to determine which BYTEx- to set low when loading the RAM. The counter is initialized by setting the LOAD-RAM- output of U5 low (Write @ \$D0X01, bit 7 low) and toggling RAM-PORT- (Read @ \$D0X41). This causes the four-bit binary counter (U9) to parallel-load its preset value of 5. The LOAD-RAM-signal can then be returned high. When the output of the chip counter is 5, the BYTE0- output of the U11 PAL selects static RAM chip U100. A write to RAM-PORT- causes the selected RAM to load the data on the bus and advances the chip counter U9 output to 6, causing U11 output BYTE1-to select U102. This operation is repeated until the counter reaches 15, at which point the U10 PAL output BYTE10- selects the Control RAM U600. Upon performing a write to RAM-PORT-, the Control RAM is loaded with the data, and the RCO output of U9 goes low.

The RCO output is used as the DECREMENT- clock. The clock is routed to the SSLOGIC block where it decrements the Vector RAM Address Register. The RCO output is also routed through U7 to reload the U9 chip counter to the starting count of 5.

#### SSLOGIC (Start/Stop Logic) Functional Block

The SSLOGIC Functional Block consists of five groups of circuitry:

- o Signal polarity/control register.

- o Drive clock selection.

- o Start/stop control.

- o Handshake synchronization.

- o Vector drive complete logic.

#### SIGNAL POLARITY/CONTROL REGISTER

The output section signal polarity and control is determined by the values stored in register U6. The values are set by performing a write to \$DOX11 with the desired value. Table 2-9 contains the register bit assignments. Bits 4 through 7 control the active edge polarity of the externally supplied START, STOP, ENABLE, and DR CLK signals. Bit 3

determines if the vector drive clock should be always enabled or if the external ENABLE should be used. Bit 2 determines if the vector output should be "force" started (no external start required) or if the external START is required. Bit 1 determines if the external STOP signal should terminate vector driving or not. Bit 0 is unused (the address and position of this bit are used for clearing START-ENA).

#### DRIVE CLOCK SELECTION

Five different clock sources are available for use by the output section: CLKP (from DR CLK), PSYN- (Pod Sync), INT-OSC, RAM-STROBE, and DECREMENT (used for vector RAM loading). These clocks are input to an 8-Input Multiplexer (U14). The clock selection is controlled by the MUX2, MUX1, and MUX0 outputs of the U5 register. The clock is selected by performing a write to \$D0X01 and setting bits 2, 1, and 0 to the desired values. Table 2-8 shows which clocks are selected by the different bit settings. The clock source selected for vector driving or loading is routed from U14-5 to U19 (where it is enabled by DONE- if vector driving is not complete) and to the SSGATE Flip-Flop U16.

Table 2-9. U6 Register Bit Description (Write @ \$D0X11)

| BIT | SIGNAL     | 1               | 0                |

|-----|------------|-----------------|------------------|

| 7   | CLK-POL-   | Falling Edge    | Rising Edge      |

| 6   | ENA-POL    | Enable High     | Enabie Low       |

| 5   | STOP-POL-  | Falling Edge    | Rising Edge      |

| 4   | START-POL- | Falling Edge    | Rising Edge      |

| 3   | ENA-ALWAYS | Enable Always   | No Enable Always |

| 2   | FOR-START- | No Forcestart   | Forcestart       |

| 1   | STOP-ENA-  | No Stop Enabled | Stop Enabled     |

| 0   | Unused     |                 |                  |

The PSYN signal is inverted by U20 to PSYN-. This allows the vectors to be driven on the falling edge of PSYN (so the vectors are driven and settled by the time the rising edge of PSYN clocks the input section.

#### START/STOP CONTROL

The Start/Stop Control Circuit consists of two 74ACT74 D-Type Flip-Flops (U13 and U16), a 74AC32 OR Gate (U15), a 74AC20 Quad Input NAND Gate (U12), and a 74AC08 AND Gate (U19).

U16 determines whether the selected clock source (from U14) decrements the Vector RAM Address Register (and latches the RAM data out if in the drive mode) or not. If the DONE- signal is not active on U19-1, the clock is gated through to U16-3. If the SSGATE- line is high, the clock is disabled. If SSGATE- is low, the rising-edge of the clock causes CK-OUT (U16-6) to go high and is presented to the vector drive circuitry. As soon as the clock input is no longer high, the U15 CLK-PRES output goes low (since U15 pin 5 is low as well) and sets U15, returning the CK-OUT signal low.

SSGATE- on U12 pin 6 provides the qualifying signal to the clock. In order to have the clock qualified, the following conditions must be met:

- O U12 pin 1 must be high. This line insures that a start has been received, either by the FOR-START- line being low or by the STRP signal having the programmed edge on the external START line.

- o U12 pin 2 must be high. This line ensures that no external STOP signal of the programmed edge has been received or that vector driving is not yet complete (DONE- on U13 pin 1 clears the pin 5 output, thereby disabling SSGATE-).

- o U12 pin 4 must be high. This is the ENA-RCVD line, and is either high all the time (if ENA-ALWAYS is high) or high only when the input on the external ENABLE line is at the programmed level.

- o U12 pin 5 must be high. This is the HS-ENABLE line and is high if vector driving is not suspended awaiting a WAIT input. If a WAIT statement has been reached in the vector file, the HSOUT line of the Vector Control RAM is active and sets the HS-ENABLE low, suspending vector driving. (The following text describes handshake synchronization in more detail.)