Volume 5, number 2

Summer 1988

# **Inside the** Troubleshooter

# Newsfront

Philips instruments complement the Fluke line of board testers...

9100 On-site Service available...

Free training available for 9100 and 9010...

OuickTools™ software for the 90 Series...

**Application Note for** the 90 series .....3

# Case History

The evolution and future direction of a production test system ......4

#### Elsewhere...

**Diagnostic Programming** on the Intel 8237A and AMD 9517A .....6

Programming multiplication and division on

The Fluke 90 Series: A new emulation technique in testing .......8

# Fluke Cooperative Service Members

The Fluke Cooperative Services team is a network of independent specialists who know hardware, software, and your industry ... 10

# Course Schedule

A complete listing of Fluke 9000 Series classes through the end of the year ......11 FLUKE

# TroubleShooter

# Increasing the speed of RAM testing with HyperRAM

The new HyperRAM test algorithm (patent pending) was developed by John Fluke Mfg. Co. to provide fast RAM testing while retaining comprehensive fault detection capabilities. HyperRAM is included in Fluke's new HyperTEST<sup>TM</sup> procedure for fast functional memory testing with the 9100 Series Digital Test System and the 9000 Series Micro System Troubleshooter. Also included in HyperTEST is HyperROM, a new algorithm that greatly increases the speed of ROM testing.

## RAM test algorithms and techniques

Various RAM test algorithms now in use balance the need for thorough testing with available test time. Each of these tests sacrifices some fault detection capability to reduce testing time.

The simplest form of RAM test is the read/write test commonly used in power-up self tests. At the other end of the spectrum are complex multipass tests such as the 30N (where N is the number of accesses per memory location), 16N, and 14N tests that improve fault coverage at the expense of speed.

In between the simple read/write and the complex multipass tests is Fluke's 5N probabilistic test called RAM Fast. This patented RAM test algorithm covers most common faults deterministically while detecting other less common faults probabilistically. The chance of detecting faults probabilistically improves with multiple executions of the test or with multiple occurrences of similar faults. The faults detected probabilistically by the RAM Fast test commonly cause multiple occurrences of similar failures. The RAM test algorithm uses pseudo random data to perform five accesses to each RAM address. The speed and fault coverage of this test are excellent.

Fluke's recently developed HyperRAM algorithm expands on the RAM Fast test by providing much faster execution while retaining the same fault coverage. Rather than using

an infinite string of random data that must be calculated at each address location, the HyperRAM test uses a small fixed set of random data before beginning the test. This fixed block of random data is reused as many times as necessary to cover the entire range of RAM addresses tested. Eliminating data calculation and utilizing fixed block sizes vastly improves test speed.

The HyperRAM algorithm, along with optimized test methods, has been incorporated into the 9000A-80286H Microprocessor Interface Pod. The 80286H pod with HyperRAM capability is supported by the Fluke 9000 Micro-System Troubleshooter and the 9100 Digital Test System. Future pods will also incorporate the HyperRAM test function.

## Optimizing features of HyperRAM

The HyperRAM test implemented in the 80286H pod has been optimized beyond the test algorithm. HyperRAM test speed was increased by programming the algorithm in assembly language instead of a high level language like C. To further increase the speed of the HyperRAM test, the 80286H pod uses the following optimizing features:

- memory emulation of overlay RAM

- native processor execution (RUNUUT mode)

- breakpoints

...The HyperRAM algorithm executes a test up to 60 times faster than the RAM Fast test.

## HyperRAM...

(cont. from pg 1)

The HyperRAM test is executed in the RUNUUT mode while the algorithm resides in the overlay RAM in the pod. This allows the RAM test to execute considerably faster than traditional microprocessor emulation, since no bus switch or single step operations are required. Further, since overlay RAM in the 80286H pod is high speed, with zero wait

states, RUNUUT executes test instructions faster than some UUT based self tests.

Breakpoints send signals to the host test system that a test is complete. A "break" occurs once a preselected event has occurred, such as reaching a specific address or data pattern. Once the test is complete, information can be extracted from memory by the test system. Breakpoints can also be used to check the status of the HyperRAM test without stopping the test. If the test is still running, a "busy" signal is returned to the host test system.

# Implementation of HyperRAM

The Fluke HyperRAM test utilizes all of the optimizing features mentioned earlier. The HyperRAM algorithm uses the 80286's string move and compare instructions where possible to quickly copy or test large sections of memory. The test is executed in protected mode, allowing access to the 80286's entire 16M byte address space. Breakpoints allow the 80286H pod to communicate status information to the host test system at regular intervals.

HyperRAM is executed on the 9100 Series in immediate mode by selecting the "HYPER" softkey under the "RAM TEST" menu. This invokes a TL/1 program which requests the RAM test parameters and passes them to the pod. The user enters values for the address space including the starting address, ending address, random number seed, and delay. The TL/1 program then starts the test, monitors its progress, invokes a diagnostic routine if the test fails, and reports the results.

Execution on a 9000 Series instrument is accomplished by writing test parameters to special addresses in the pod using the basic WRITE operation. The test begins executing when the last parameter is entered. Test status is monitored by performing READ operations. On completion. the diagnostic information (e.g., failed address, expected and actual data) is read from additional special addresses in the pod. For more information on performing the HyperRAM test on the 9000 Series Troubleshooter see the 9000A-80286H Istruction Manual, Section 3.

Using a 9100A Digital Test System and a 9000A–80286H Interface Pod, the HyperRAM algorithm executes a test up to 60 times faster than the RAM Fast test (depending on the size of the memory being tested). When testing the memory of an IBM PC/AT, configured with 512K bytes of DRAM running at 6 Mhz with 1 memory access wait state, the test time was reduced from 165 seconds, using the RAM Fast test, to 6 seconds. Test time was reduced from 11 minutes to 13 seconds when testing a 2 Mbyte Intel Above Board 286 expansion RAM card

#### Conclusion

As microprocessor-based products become more complex and more memory space is

# HyperRAM Fault Coverage

The HyperRAM algorithm detects two types of RAM faults:

- Those that exist (or do not exist) with 100% certainty.

- Those that are detected part of the time with a specified probability.

Although the second category of faults are only detected part of the time, multiple faults multiply the probability that at least one will be detected. The HyperRAM algorithm is designed to detect faults that typically occur in more than one place. For example, address, row, or column decoder failures all cause large sections of RAM to fail simultaneously. If as few as 32 locations are affected (even though the probability of finding a single isolated fault might be only 50%), the chances of not detecting at least one fault in 32 is 1 in 2.15 x 10°.

Many different types of RAM faults are detected by the HyperRAM algorithm, including stuck memory cells and aliased cells. Stuck memory cells always present the same logic level, 1 or 0, regardless of what the level should be at a particular location. Aliased cells are cells that are effectively "shorted" together; this occurs when data written to one cell is written to other cells. Aliasing may also occur when a single cell is selected on read and write operations even though different addresses are specified.

Faults detected with 100% certainty include:

- Stuck memory cells.

- Stuck data lines.

- Stuck address lines.

- Shorted address lines.

added, demand for a faster RAM test will continue to rise. Hyper-RAM is designed to answer these demands by optimizing test times without sacrificing the test coverage expected of modern, high quality RAM tests.

- Cells at different addresses that are aliases.

- Uni transitional stuck at fault (the cell initially contains one level, but gets stuck after a write to the opposite level).

Faults detected part of the time include:

(The numbers in parentheses indicate the probability of detection on a single test execution).

- A pair of cells within the same address that are aliases (50%).

- Data written to a cell overwrites data in a cell located at a different address (50%).

- Data read from a cell is actually read from a cell located at a different address (aliasing) (75%).

- A cell value that is influenced by the value in a second cell (50%).

- A cell value that is influenced by the value of an address line (50%).

- A cell value that is influenced by the values in N other cells (pattern sensitivity) (100 x (.5<sup>N</sup>)%).

- Shorted data lines, where N is the number of addresses affected (100 x (1-.5<sup>N</sup>)%).

The HyperRAM test also detects dynamic RAM refresh problems. If the test is invoked with an adequately large delay parameter, all RAM refresh circuit failures are detected. Occasionally, it is necessary to disable the pod's "standby read" feature so that standby reads do not artificially refresh the RAM.

Newsfront

# 90 Series News— Application Note

The 90 Series Board Testers are surprising many users with their simplicity of operation. However, the turn-on with the unit under test may require special consideration for the way the designer handled some elements of his design. To address this issue Fluke offers an Application Note, "Getting Started with the 90 Series" with seven pages of hints to help insure success. This is highly recommended reading for the service engineer and may provide good advice for the designer as well on the topic of "designing for testability."

# Philips Instruments complement Fluke line of board testers

To complement our line of board testers, Fluke offers a broad line of technologically innovative, high performance logic analyzers and digital storage oscilloscopes, with unprecedented ease-of-use. The Philips logic analyzers are ideal for hardware-software integration, plus hardware and software development.

Philips digital storage oscilloscopes offer advanced features like 2GHz bandwidth, user programmable set-up memories, and unmatched calculating and analysis capabilities. Also featured is AUTOSET, for automatic selection of channel, amplitude, timebase and trigger to provide errorfree display of any input signal. Philips DSO's also provide a wide range of performance in speed and resolution to capture, display, measure and document even fastchanging signals in a variety of applications. For more information contact Fluke at 1-800-44-FLUKE ext. 77.

# 9100 On-site service

On-site service for your 9100s is now available. If you're using your 9100s for production test, or they find their way into a critical repair turnaround environment, you demand guaranteed uptime. For approximately 2.3% of the acquisition price, you get on-site repair service that supplements your 90 day warranty and meets this demand. After the end of the 90 day warranty, for only about 6% of the acquisition price, you get extended warranty coverage as well as on-site service for one year to help keep your test operation running smoothly.

In the U.S., call 1-800-44-FLUKE, ext. 73, to find out more about this Fluke service. To order this service in other countries, call your local Fluke representative.

# Free training available for 9100 and 9010

With the purchase of a mainframe, Fluke offers free training for 9100 and 9010 customers. Ask your Account Manager about a certificate entitling you to either a hands-on application for the 9010, or a hands-on application and programming course for the 9100. The courses are specifically designed to drive your performance curve higher. This program has been in effect from July 1, 1987 for U.S. customers. Only one certificate per mainframe.

# QuickTools TM Software for the 90 Series

Fluke introduces QuickTools, a software package designed for remote operation and control of the Fluke 90 Series through an IBM PC or compatible. QuickTools makes remote operation of the 90 Series as easy as using the Tester's front panel. This package allows you to use not only all of the 'local' features via the RS-232 interface, but also accesses features not available through the front panel, including:

- Break-Point

- Frame-Point

- External Trigger

- Upload

- Download

- Memory Fill

- and many others!

Also built into QuickTools are features which allow the operator to:

- Stimulate entire board through creation of batch tests

- Create & edit programs using built-in program editor

- Record or print entire interaction between 90 Series and PC

- Make easy remote command syntax calls via pop-up prompting

- Check out program steps on 90 Series while in 'Interactive' mode

- Execute short sequences with function keys

Price: \$300, U.S. List

3

# **A Case History**

# Using the Fluke Troubleshooter for production testing

By Edward A. Gedeon

The evolution

and future direction

of a production

test system.

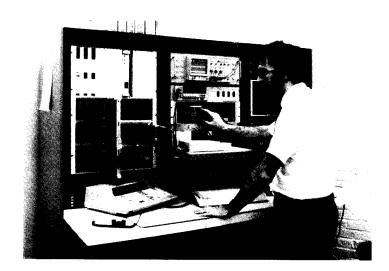

For several years, a major manufacturer has been using Fluke Troubleshooters and Instrument Controllers for production testing and repair. Described below is the evolution of the test system and its future direction.

### Developing the need

A division of the company is the leading manufacturer of newspaper and commercial printing equipment. In 1979, the "electronics" of a press consisted mainly of switches, relays, and miles of point-to-point wiring. The first microprocessor based systems had just reached the drawing board. These early systems were either functionally identical replacements of older electro mechanical designs, or add-on features that performed single functions such as aligning the margins of the paper entering the press. These new features were very popular with customers, and orders for microprocessor controls increased steadily.

The increased production that followed required increased testing capabilities. At first, each new design had dedicated, standalone test fixtures with varying sizes, shapes, connectors, procedures, and test difficulty. One tester had 121 switches and 104 lights on the front panel and stood seven feet tall. It was commonly referred to as "The Port-a-Potty".

Not all fixtures were this complex. For example, our group designed a tester for a microprocessor-based board with separate kernel, RAM, ROM, and I/O line tests. The tests could be run individually or in sequence, with error messages displayed on an alphanumeric display. One could step through a test, loop on an error, or abort the test program. This test fixture was very successful. However, it was designed for on board testing only. We were faced with redesigning identical features into every fixture for each new circuit board. Fortunately, the Fluke 9000 Series has helped simplify the development of test fixtures.

The 9010A Troubleshooter performed all the functions of our previous test system, but was simpler to program. After spending five years working with assembly language, the 9010A instruction set was a welcome change. The 9010A language compiler made programming simpler. Software development time was reduced and the only additional hardware was easily satisfied with off the shelf I/O boards and interface cables.

Used alone, the 9010A still has a few drawbacks. Program size and complexity are limited. Prompts and error messages are limited by the 32-character display. Trying to perform simple arithmetic with the 9010A is

difficult, even with the utility subroutines developed by Fluke. These problems were eliminated when the current system was adopted: A 9020A Troubleshooter coupled with a Fluke 1722A Instrument Controller.

#### The current system

The Fluke 1722A Instrument Controller was first used in 1985. and since then, test programs for over fifty different circuit boards have been developed. The 1722A uses the IEEE-488 bus to control the 9020A Troubleshooter and the 6809 Interface Pod. Test menus and programs are displayed on the touch screen; in most cases, the test operator can run the entire program using only the touch screen. A second 9020A was added to develop an intelligent serial I/O board based in the Motorola 68008 µP. This board was tested using a 68000 pod and an adapter. We kept both test programs in the system, using one for testing 8-bit boards with the 6809 pod, and the other for 16-bit boards using the 68000 pod. We recently added a Fluke 8840A DMM connected to the IEEE-488 Bus and under control of the 1722A.

The remaining hardware in the test system consists of a STD Bus Card Cage (for 8-bit boards), a Gespeac G 96 Card Cage (for 16-bit boards), a power panel which makes various DC voltages available for test purposes, and a

5

few special purpose interface and I/O boards to monitor signals output from the UUT. We have designed our own interface boards using off the shelf I/O boards.

Test programs are written in BASIC and stored on 5 ½! diskettes. To help reduce software development time, a library of subroutines for common functions such as touch screen input, menu generation, error handling, and program chaining has been developed. Programming time ranges from one to four weeks depending on the complexity of the board.

Originally, boards that were installed in the same chassis had their programs stored on the same diskette. Soon, two problems arose. First, some systems were more complex than others, so that some diskettes were filled to capacity while others held only two or three programs. Second, when a technician on the manufacturing floor was given a new board to test, he was confused about which diskette contained the test needed. The problem was solved by putting the test programs in numerical order, using the part numbers of the boards being tested, and labeling each diskette with the range of boards it tested.

A typical board test is performed as follows. The test system is set up with the 1722A, or 9020A with interface pod, a CPU under test, and one or two I/O

boards. The diskette is loaded into the 1722A disk drive. Then, the menu driver and all of the test programs are copied to the 1722A internal RAM. The IEEE-488 port is initialized, the BASIC shell is loaded, and the main menu is generated, listing all of the test programs on the disk. The test operator touches the 1722A screen next to the name of the test and that test program is executed. As the test progresses,

#### **Future considerations**

The present system has some limitations. Newer test programs take longer to execute because of the complexity of the boards. Because of the limitations of the 1722A and the 9020A, memory testing is becoming a bottleneck. A typical board has 256K to 1 megabyte of RAM. Even with the "Quick RAM" test used by the newer interface pods, 1 megabyte takes over 12 minutes to test. EPROM testing is equally time consuming, as the production software becomes more sophisticated and program size grows geometrically.

Another drawback to the present test system is the bandwidth of the IEEE-488 bus. On one board, two 512 byte FIFO buffers were tested. This required writing thousands of bytes of data from the 1722A to the 9020A, one at a time, then reading them back, and checking the "buffer empty" and "buffer full" flags for errors. Program execution time was 15 minutes for testing a single board.

Still another problem is that the 9020A is designed to operate

New memory tests are up to 30 times faster than the "Quick RAM" and "Quick ROM" tests now in use.

Instead of designing special interfaces for each design, the I/O modules monitor up to 160 signals. The 20 Mbyte hard disk provides more than enough storage space for our test programs. The programs we have written so far would fill about a quarter of the hard disk. Now, programs can be written in a high level language designed for testing.

Best of all is the built-in fault tracing algorithm. Given a list of devices and interconnections for a particular board, the 9100A can guide the test operator through the troubleshooting procedure. It may also be possible to download interconnection and part information from the CAD system, which would reduce software development time to a few days.

There has been a great deal of success with the test equipment, and Fluke products will continue to be used in the future. With Fluke's help, this manufacturer has applied state-of-the-art electronics to its newspaper and commercial printing equipment.

# The benefits of emulative testing

Being application specific, like emulative testing is, has its advantages. Testing is faster and it enforces a logical troubleshooting approach. It even makes general purpose instrumentation like oscilloscopes work better in dynamic  $\mu P$  based circuitry by providing control and stable stimulus.

#### A.Faster Testing

Emulative board test speeds testing and troubleshooting because it's tests cover the circuits functions so well. This board coverage is achieved because the tests work like the circuit was designed, with the µP in control, in real time.

"Case History," continued on page 12

# "The 9100A Digital Test System operates much faster than our present system..."

results are displayed on the 1722A's screen. In case of an error, the fault is highlighted, and the operator is given the option of looping on the error, ignoring it and continuing, or aborting the test program and returning to the main menu.

On completing the test, the operator can either return to the main menu or repeat the test program. This "repeat" feature is used to test batches of identical boards. The operator turns off DC power to the card cage, replaces the board just tested, restores power, and restarts the test without re-initializing the system.

only with microprocessor-based boards. This means that peripheral boards usually need additional circuitry to interface to the test equipment. As soon as the design engineer has finished a new board, additional time must be spent designing an additional board just to test the first board. The more complex the test set up, the more complicated the test program: 500 line programs are typical.

Fortunately, the 9100 Series of testers offers solutions to exactly the type of problems we are now facing. The 9100A Digital Test System operates much faster than our present system, mostly because there is no IEEE-488 bus.