# and the second second

A standard of the state of t

and the second of the second second

the test of the second se

**9000A-Z8000**

**1**] 15.1

# NOTE

This manual documents the Model 9000A-Z8000 and its assemblies at the revision levels identified in Section 7. If your instrument contains assemblies with different revision letters, it will be necessary for you to either update or backdate this manual. Refer to the supplemental change/errata sheet for newer assemblies, or to the backdating information in Section 7 for older assemblies.

# 9000A-Z8000 Interface Pod

Instruction Manual

P/N 716035 MAY 1984 \*1984, John Fluke Mfg. Co., Inc. All rights reserved. Litho in U.S.A.

# WARRANTY

Notwithstanding any provision of any agreement the following warranty is exclusive

The JOHN FLUKE MFG. CO., INC., warrants each instrument it manufactures to be free from detects in material and workmanship under normal use and service for the period of 1-year from date of purchase. This warranty extends only to the original purchaser. This warranty shall not apply to fuses, disposable batteries (rechargeable type batteries are warranted for 90-days), or any product or parts which have been subject to misuse, neglect, accident, or abnormal conditions of operations.

In the event of failure of a product covered by this warranty. John Fluke Mfg. Co., Inc., will repair and calibrate an instrument returned to an authorized Service Facility within 1 year of the original purchase; provided the warrantor's examination discloses to its satisfaction that the product was defective. The warrantor may, at its option, replace the product in lieu of repair. With regard to any instrument returned within 1 year of the original purchase, said repairs or replacement will be made without charge. If the failure has been caused by misuse, neglect, accident, or abnormal conditions of operations, repairs will be billed at a nominal cost. In such case, an estimate will be submitted before work is started, if requested.

THE FOREGOING WARRANTY IS IN LIEU OF ALL OTHER WARRANTIES, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS, OR ADEQUACY FOR ANY PARTICULAR PURPOSE OR USE. JOHN FLUKE MFG. CO., INC., SHALL NOT BE LIABLE FOR ANY SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, WHETHER IN CONTRACT, TORT, OR OTHERWISE.

#### If any failure occurs, the following steps should be taken:

1. Notify the JOHN FLUKE MFG. CO., INC., or nearest Service facility, giving full details of the difficulty, and include the model number, type number, and serial number. On receipt of this information, service data, or shipping instructions will be forwarded to you.

2. On receipt of the shipping instructions, forward the instrument, transportation prepaid. Repairs will be made at the Service Facility and the instrument returned, transportation prepaid.

#### SHIPPING TO MANUFACTURER FOR REPAIR OR ADJUSTMENT

All shipments of JOHN FLUKE MFG. CO., INC., instruments should be made via United Parcel Service or "Best Way"\* prepaid. The instrument should be shipped in the original packing carton; or if it is not available, use any suitable container that is rigid and of adequate size. If a substitute container is used, the instrument should be wrapped in paper and surrounded with at least four inches of excelsion or similar shock-absorbing material.

#### CLAIM FOR DAMAGE IN SHIPMENT TO ORIGINAL PURCHASER

The instrument should be thoroughly inspected immediately upon original delivery to purchaser. All material in the container should be checked against the enclosed packing list. The manufacturer will not be responsible for shortages against the packing sheet unless notified immediately. If the instrument is damaged in any way, a claim should be filed with the carrier immediately. (To obtain a quotation to repair shipment damage, contact the nearest Fluke Technical Center.) Final claim and negotiations with the carrier must be completed by the customer.

The JOHN FLUKE MFG. CO., INC. will be happy to answer all applications or use questions, which will enhance your use of this instrument. Please address your requests or correspondence to: JOHN FLUKE MFG. CO., INC., P.O. BOX C9090, EVERETT, WASHINGTON 98206, ATTN: Sales Dept. For European Customers: Fluke (Holland) B.V., P.O. Box 5053, 5004 EB, Tilburg. The Netherlands.

\*For European customers, Air Freight prepaid

#### John Fluke Mfg. Co., Inc., P.O. Box C9090, Everett, Washington 98206

# **Table of Contents**

| SECTION |                | 31111                                     | PAGE        |  |

|---------|----------------|-------------------------------------------|-------------|--|

| 1       | INTRO          |                                           | 1-1         |  |

|         | 1-1.           | PURPOSE OF THE INTERFACE POD              |             |  |

|         | 1-2.           | DESCRIPTION OF POD                        |             |  |

|         | 1-3.           | SPECIFICATIONS                            |             |  |

| 2       | INSTA          | LLATION AND SELF TEST                     | 2-1         |  |

|         | 2-1.           | INTRODUCTION                              |             |  |

|         | 2-2.           | INSTALLING THE MICROPROCESSOR IN THE POD  |             |  |

|         | 2-3. CO        | ONNECTING THE P O P TO THE TROUBLESHOOTER | I - I       |  |

|         | 2-4.           | PERFORMING THE POD SELF TEST              | 2-3         |  |

|         | 2-5.           | CONNECTING THE POD TO THE UUT             | E-Z         |  |

| 3       | MICRO          | OPROCESSOR DATA                           | 3-1         |  |

|         | 3-1.           | INTRODUCTION                              | I-E         |  |

|         | 3-2            | INTRODUCTION<br>MICROPROCESSOR SIGNALS    | 3-1         |  |

| 4       | OPER           | ATING INFORMATION                         | 4-1         |  |

|         | 4-1.           | INTRODUCTION                              | 4-1         |  |

|         | 4-2.           | GETTING STARTED                           | 4-1         |  |

|         | 4-3.           | ADDRESS SPACE ASSIGNMENT                  | 4-2         |  |

|         | 4-4.           | Introduction                              | d-Z         |  |

|         | 4-5.           | Address Mapping                           | 4-2         |  |

|         | 4-6.           | S I ATUS CONTROL LINES                    |             |  |

|         | 4-7.           | Introduction                              |             |  |

|         | 4-8.           | Status Line Bit Assignments               |             |  |

|         | 4-9.           | User-Enableable Status Lines              |             |  |

|         | 4-10.<br>4-11. | Status Flags Generated by the Pod         |             |  |

|         | 4-11.<br>4-12. | TIMEOUT FLAG                              |             |  |

|         | 4-12.<br>4-13. | NON-MASKABLE INTERRUPT ACKNOWLEDGE FLAG   |             |  |

|         | 4-13.          | NON-WASKABLE INTERRUPT ACKNOWLEDGE FLAG   |             |  |

|         | 4-14.          | VECTORED INTERRUPT ACKNOWLEDGE FLAG       |             |  |

|         | 4-16.          | SEGMENT PAGE ADDRESS TRANSLATION TRAP     | <b>4</b> -0 |  |

|         |                | ACKNOWLEDGE FLAG                          | 4-6         |  |

|         | 4-17.          | Forcing Lines                             |             |  |

|         | 4-18.          | Interrupt Lines                           |             |  |

|         | 4-19.          | User-Writeable Control Lines              |             |  |

# TABLE OF CONTENTS, continued

SECTION

------

# TITLE

| 4-20.  | Control Line Bit Assignments                                 | 4-I  |

|--------|--------------------------------------------------------------|------|

| 4-21.  | SPECIAL FEATURES AND CONTROLS OF THE Z8000 POD               | 4-8  |

| 4-22.  | QUICK FUNCTIONS                                              | 4-x  |

| J-23.  | Quick-Looping Read or Write                                  | 4-Y  |

| 4-24.  | Quick RAM Test                                               | 4-13 |

| 4-25.  | Quick ROM Test                                               | 4-16 |

| 4-26.  | SPECIAL FEATURES OF THE Z8000 POD                            | 4-16 |

| 4-27.  | Interrupt Acknowledge Words (Addresses FOOO 0000 FOOO 0003)  | 4-18 |

| 4-27.  | Fast-Looping Read: Write at Last Address (Address F000 0004) | 4-18 |

| 4-29.  | Default High Address (Address F000 0005)                     | 4-18 |

| 4-30.  | Fast RAM Test and Fast ROM Test Addresses (Addresses         |      |

|        | F000 0006 F000 0001 1)                                       | 4-18 |

| 4-3 I  | Last Test Status (Address F000 0012)                         | 4-19 |

| 4-32.  | Run UUT FCW (Address F000 0013)                              | 4-19 |

| 4-33.  | Transparent Read Address Control (Addresses F000 0014        |      |

|        | F000 0015)                                                   | 4-19 |

| 4-34.  | State of MO Output (Address F000 0016                        | 4-19 |

| 4-35.  | Refresh Enabled (Address FOOO 0017)                          | 4-19 |

| 4-36.  | Refresh Rate (Address F000 0018)                             | 4-19 |

| 4.37.  | State of Fast Mode (Address FOOO 0019)                       | 4-20 |

| 4-38.  | State of Continuous Interrupt Flag (Address F000 001A)       | 4-20 |

| 4-39.  | Last Error Group (Addresses F000 001 B F000 0021)            | 4-20 |

| 4-40.  | Error Reporting Masks (Addresses F000 0022 F000 0023)        | 4-22 |

| 4-41   | Self Test Diagnostic (Address F000 0024)                     | 4-22 |

| 442.   | DEFAULT ADDRESSES FOR LEARN, BUS TEST.                       |      |

|        | AND RUN UUT                                                  | 4-22 |

| 443.   | Learn Operation Default Address                              | 4-23 |

| 4-44.  | Bus flest Default Address for Data Line Testing              | 4.23 |

| 445.   | Run UUT Mode                                                 | 4-23 |

| 4-46.  | INTERRUPT HANDLING                                           | 4-23 |

| 4-47.  | PROBE AND OSCILLOSCOPE SYNCHRONIZA FION MODES                | 4-24 |

| 4-48.  | PROBLEMS DUE TO A MARGINAL UUT                               | 4.24 |

| 4-49   | UUT Operating Speed and Memory Access                        | 4-25 |

| J-50.  | UUT Noise Levels                                             | 4-25 |

| 4-5 I. | Bus Loading                                                  | 4-25 |

| 4-52.  | Clock Loading                                                | 4-25 |

| 4-53.  | POD DRIVE CAPABILITY                                         | 4-25 |

| 4-54.  | LOW UUT POWER DETECTION                                      | 4-25 |

| THEOR  |                                                              | 5.1  |

|        |                                                              |      |

| 5-I.   | INTRODUCTION                                                 |      |

| 5-2.   | GENERAL POD OPERA FION                                       |      |

| 5-3.   | Processor Section                                            | • •  |

| 5-4.   | UUT Interface Section                                        |      |

| 5-5.   | Timing and Control Section                                   |      |

| 5-h.   | DETAILED BLOCK DIAGRAM DESCRIPTION                           |      |

| 5-7.   | Detailed Description of the Processor Section                |      |

| 5-x.   | Detailed Description of the UUP Interface Section            |      |

| 5-9    | Detailed Description of the Liming and Control Section       |      |

| 5-10.  | Pod Context                                                  |      |

| 5-I I. | UUI Context                                                  | 3-10 |

5

## TABLE OF CONTENTS, continued

#### PAGE SECTION 31111 5-12. 5-12 5-13 Initialization TROUBLESHOOTING 6 6-1 INTRODUCTION WARRANTY AND FACTORY SERVICE ...... 6-1 6-2. Χ-I, DETERMINING WHETHER T'H& POD IS DEFECTIVE OR 6-4. INOPERATIVE ...... 6-2 **Ă**−S, TROUBLESHOOTING A DEFECTIVE POD 6-6. 6 - T the Self Test Failure Codes 6-3 Interpreting 6-8 TROUBLESHOOTING AN INOPERATIVE POD ...... 6-7 6-9. 6-10 6-11. 6-12 EXTENDED TROUBLESHOOTING PROCEDURES ...... 6-13 6-13. 6-14. 6-15. 6-16. 6-17 6-18. LIST OF REPLACEABLE PARTS 7 INTRODUCTION ...... 7-1 Į-Į, HOW T 0 OBTAIN PARTS 7-1 7-S. MANUAL CHANGE AND BACKDATING INFORMATION ..... 7-2 7-3. UTILITY PROGRAM FOR QUICK FUNCTIONS ...... A-1 A SCHEMATIC DIAGRAMS 8 TABLE OF CONTENTS 8-1.

INDEX

# **List of Tables**

# TABLE

# TITLE

# PAGE

| 1-l. | 28000 Pod Specifications                        | 1-3  |

|------|-------------------------------------------------|------|

| 3-1. | Signal Descriptions                             | 3-1  |

| 3-2. | Signal Summary                                  | 3-3  |

| 4-1. | Status Codes                                    | 4-4  |

| 4-2. | Status and Control Line Bit Assignments         | 4-5  |

| 4-3. | Special Addresses                               | 4-n  |

| 4-4. | Special Address Summary                         | 4-10 |

| 4-5  | Quick-Looping Functions of the 28000 Pod        | 4-13 |

| 4-b  | Using the Quick RAM Test                        | 4-15 |

| 4-7. | Using the Quick ROM Test                        | 4-17 |

| 6I.  | Required Test Equipment for Pod Troubleshooting | 6-2  |

| 6-2. | Standard Self Test Failure Codes                | 6-3  |

| 7-1. | 28000 Final Assembly                            | 1-3  |

| 7-2. | A33 Processor PCB Assembly                      | 7-6  |

| 7-3. | A34 Interface PCB Assembly                      | 7-9  |

| 7-4. | Manual Status and Backdating Information        | 7-11 |

# List of Illustrations

# FIGURE

# TITLE

# PAGE

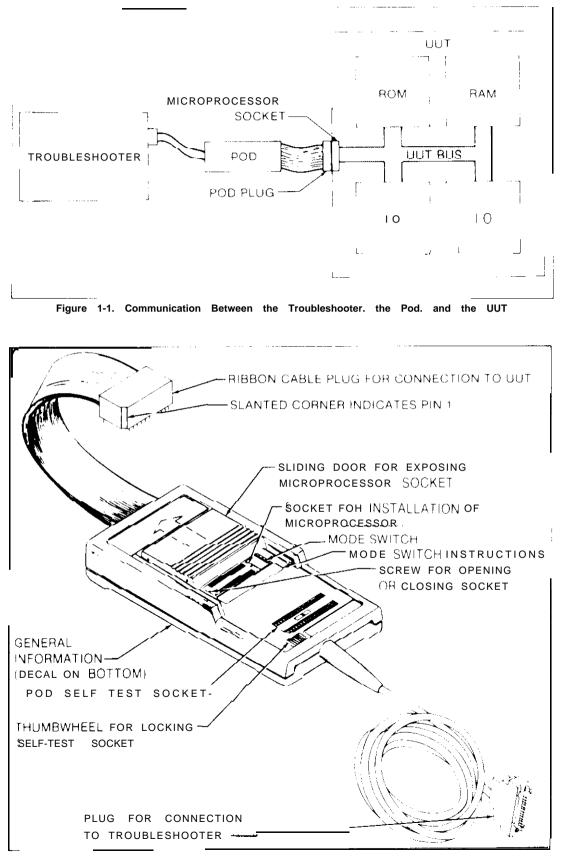

| - .  | Communication Between the Troubleshooter, the Pod. and the UUT | 1-2  |

|------|----------------------------------------------------------------|------|

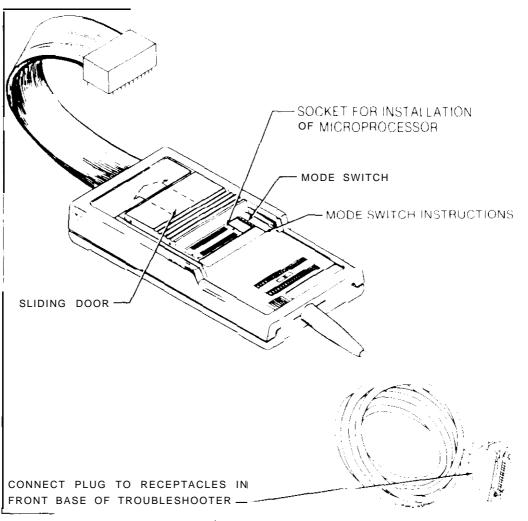

| 1-2. | External Features of the ZXOOO Interface Pod                   | 1-2  |

| 2-1. | Location of Microprocessor Socket and Mode Switches            | 2-2  |

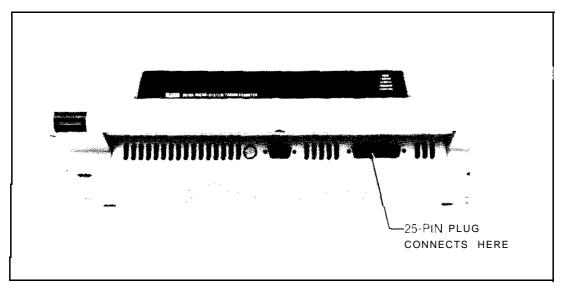

| 2-2. | Connection of Interface Pod to Troubleshooter                  | 2-2  |

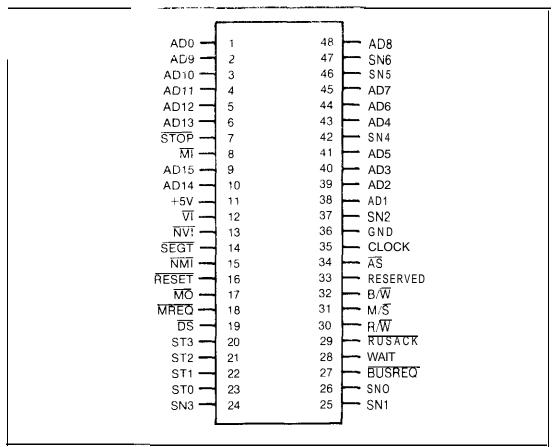

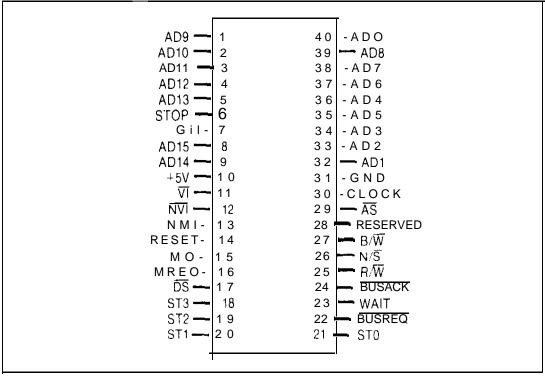

| 3-1. | Z8001 Pin Assignments                                          | 3-4  |

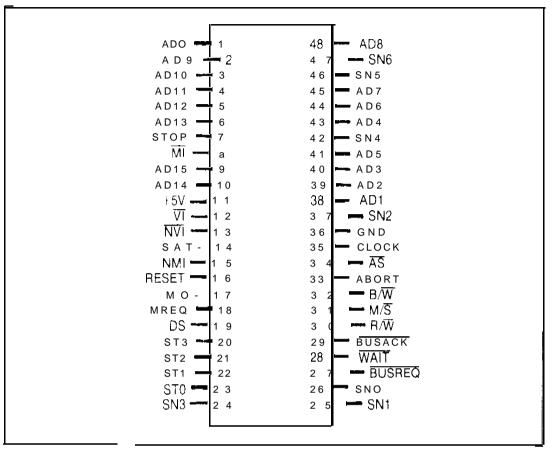

| 3-2. | 28002 Pin Assignments                                          | 3-4  |

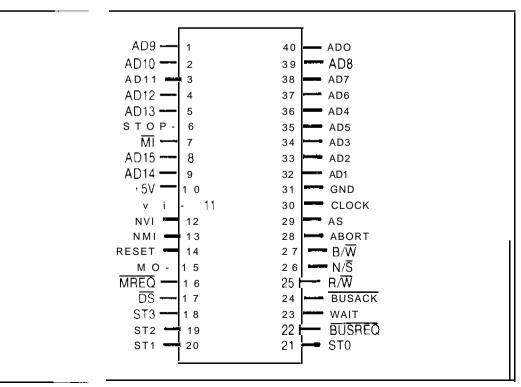

| 3-3. | 28003 Pin Assignments                                          | 3-5  |

| 3-4. | ZR004 Pin Assignments                                          | 3-5  |

| 5-1. | General Block Diagram                                          | 5-2  |

| 5-2. | Detailed Block Diagram                                         | 5-6  |

| 5-3. | Handshake Signals                                              | 5-8  |

| 54.  | 28000 Signal Timing Relationships                              | 5-10 |

| 5-5. | Sync Pulse Generation                                          | 5-11 |

| 6-1. | Troubleshooting a Defective Pod                                | 6-6  |

| 6-2. | 'Troubleshooting an Inoperative Pod                            | 6-8  |

| 7-1. | Z8000 Final Assembly                                           | 7-4  |

| 7-2. | A33 Processor PCB Assembly                                     | 7-x  |

| 7-3. | A34 Interface PCB Assembly                                     | 7-10 |

| 8-1. | A33 Processor PCB Assembly                                     | x-2  |

| x-2. | A34 Interface PCB Assembly                                     | 8-5  |

# Section1 Introduction

# NOTE

It is assumed that the user of this manual is familiar with the basic operation of one of the 9000 series Micro-System Troubleshooters as described in the 9000 series Operator Manuals.

# I-I. PURPOSE OF THE INTERFACE POD

The 9000A-Z8000 Interface Pod (hereafter referred to as the Pod) interfaces any Fluke YOOO series Micro-System Troubleshooter (hereafter referred to as the Troubleshooter) to equipment using one of the Z8000 family of microprocessors. The Troubleshooter services printed circuit hoards, instruments, and systems employing microprocessors. The 9000A-Z8000 Interface Pod adapts the general purpose architecture of the Troubleshooter to the specific architecture of the Z8000 microprocessor family. The Pod adapts such microprocessor-specific functions as pin layout. status/control functions, interrupt handling, timing, and memory and I/O addressing.

The 9000A-Z8000 Interface Pod can accommodate all four members of the Z8000 family: Z8001, Z8002, Z8003, and Z8004. An adapter is provided for use with the 40-pin 28002 and Z8004 versions. A switch on the Pod selects between Segmented Memory28001 and Z8002 versions, and Virtual Memory 28003 and Z8004 versions. Unless otherwise specified, references to the "Z8000" in this manual refer to any of the 28000 family of microprocessors.

#### I-2. DESCRIPTION OF POD

Figure I-I shows the communication between the Troubleshooter, the Pod, and the Unit-Under-Test (hereafter referred to as the UUT). Cables connect the Pod to the I roubleshooter via a front,-panel connector and to the UUT through the microprocessor socket.

I he external features of the Pod is shown in Figure I-2

Internally, the Pod consists of a pair of printed circuit board assemblies mounted within an impact-resistant case. The Pod contains a Z8000 family microprocessor along with the supporting hardware and control software that is required to do the following:

- 1. Perform handshaking with the Troubleshooter.

- 2. Receive and execute commands from the Troubleshooter.

- 3. Report UU1 status to the Troubleshooter,

- 4. Allow the Pod microprocessor to operate the UUT.

Figure 1-2, External Features of the Z8000 Interface Pod

'The Troubleshooter supplies operating power (+5V) for the Pod. The LJUT provides the external clock signal required by the Pod for operation. Using the UUT clock signal allows the Troubleshooter and Pod to function at the designed operating speed of the UUT (up to 10 MHz).

Logic level detection circuits are provided on each line to the UUT. These circuits allow detection of bus shorts, stuck-high, or stuck-low conditions, and any bus drive conflict (two or more drivers attempting to drive the same bus line).

Over-voltage protection circuits are also provided on each line to the UUT. These circuits guard against Pod damage which could result from the following:

- I. Incorrectly inserting the ribbon cable plug in the UUT microprocessor socket.

- 2. UUT faults which place potentially-damaging voltages on the UUT microprocessor socket.

The over-voltage protection circuits guard against voltages of +12V to -7V on any one pin. Multiple faults, especially of long duration. may cause Pod damage.

A power level sensing circuit constantly monitors the voltage level of the UUT power supply (+5V). If UUT power rises above or drops below an acceptable level the Pod notifies the Troubleshooter of the power fail condition.

'The 48-pin zero-insertion force Self Test Socket provided on the Pod enables the Troubleshooter to check Pod operation. The ribbon cable plug must be connected to the Self Test Socket during self test operation. The ribbon cable plug should also be inserted into this socket when the Pod is not in use to provide protection for the plug.

# **1-3. SPECIFICATIONS**

Specifications for the Pod are listed in Table I-I

| IELECTRICAL PERFORMANCE                                                                                                                                                                                                                                                   |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| PowerDissipation5wattsmax.MaximumExternalVoltage-7Vto+12Vmaybe appliedbetween<br>ground and any ribbon cable plug pin<br>continuously.                                                                                                                                    |  |  |  |  |  |

| MICROPROCESSOR SIGNALS                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Input Low Voltage -03V m i n . , 0.8V m a x .<br>Input High Voltage 2.0V min., 5.0V max.<br>Output Low Voltage 0.5V max. at rated current<br>Output High Voltage 2.4V m i n . a t - 4 0 0 ua<br>Tristate Output Leakage Current ±0.02 mA typical, +0.1 to<br>-0.2 mA max. |  |  |  |  |  |

| Input Current<br>CLK -1.2 mA max.<br>All Other Input Lines ,6 mA max.                                                                                                                                                                                                     |  |  |  |  |  |

| Table | I-I. | Z8000 | Pod | Specifications |

|-------|------|-------|-----|----------------|

|-------|------|-------|-----|----------------|

| TIMING CHARACTERISTICS                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------|

| Maximum External Clock <b>Frequency</b> 10.0 MHz typical<br>Insertion Delays Io 28000 Signals                                       |

| Input Signals 1 2 ns.t y p i c a l<br>Output Signals 15 ns typical                                                                  |

| UUT POWER DETECTION                                                                                                                 |

| Detection of Low Vcc Fault Vcc <+4.5V<br>Detection of High Vcc Fault V c c c >+5.5V<br>Pod Protection from UUT Low Power Vcc <+3.3V |

| GENERAL                                                                                                                             |

| Sire         5.7 cm H x 14.5 cm W x 27.1 cm L (2.2 in H x 5.7 in W x 10.7 in L)                                                     |

| Weight 1.5 kg (3.3 lbs)                                                                                                             |

| Environment<br>STORAGE -40°C to +70°C, Rt- <95% non-<br>condensing                                                                  |

| OPERATING 0 ° C t o +40°C, R H <95% nor<br>condensing<br>+40°C t o +50°C, RH <75% non-<br>condensing                                |

|                                                                                                                                     |

# Table 1-1, Z8000 Pod Specifications (cont)

# Section 2 Installation and Self Test

## **Z-I. INTRODUCTION**

The procedures for connecting the Pod to the-Troubleshooter, performing the Pod Self Test, and connecting Pod to the UUT are given in the following paragraphs.

# 2-2. INSTALLING THE MICROPROCESSOR IN THE POD

A microprocessor must be installed in the Pod to prepare it for testing a UUT.

Note

The Pod is supplied with a Z8001 microprocessor rated for 6 MHz operation. You will need to replace the microprocessor if your application requires a faster Z8001 or if your UUT uses a Z8002, Z8003, or Z8004.

The Pod socket is not designed for repeated insertions. It is not meant to test a new CPU with each tested assembly.

To install a microprocessor in the Pod, perform the following steps:

- I. If the Pod is already connected, remove power from the UUT and the  $Troubleshooter. \end{tabular}$

- 2. Select a microprocessor to use in the Pod, either the one out of the  $UUT,\,{\rm or}\,$  another of the same type.

- 3. Open the sliding door on the top of the Pod (shown in Figure 2-I) to expose the Pod microprocessor socket. Open the socket contacts by using a screwdriver to turn the screw at the end of the socket. Turn the screw counterclockwise to open the socket.

- 4. If a Z8002 or Z8004 is used, insert the microprocessor into a 40-48 pin adapter before installing it into the Pod. Insert the chosen microprocessor into the socket. aligning pin I to the marked position. Close the socket contacts by turning the screw clockwise. Close the sliding door.

- 5 Set the Processor Select Switch to the correct position (as shown on the Pod decal) for Segmented Memory or Virtual Memory devices.

# 2-3. CONNECTING THE POD TO THE TROUBLESHOOTER

- 1. Remove power from the Troubleshooter.

- 2. Using the round shielded cable, connect the Pod to the Troubleshooter at the location shown in Figure 2-1. Secure the connector using the sliding collar.

Figure 2-1. Location of Microprocessor Socket and Mode Switches

Figure 2-2. Connection at Interface Pod to Troubleshooter

# 2-4. PERFORMING THE POD SELF TEST

'To perform the Pod Self Test, perform the following steps:

- 1. Make sure that a6 MHz or greater clock speed microprocessorisinstalled in the Pod microprocessor socket. and that the Processor Select Switch is set according to the Pod decal.

- 2. If a 40-pin adapter is attached to the ribbon cable plug, remove the adapter before proceeding.

- 3. Open the pins of the Pod Self Test socket by turning the adjacent thumbwheel. insert the ribbon cable plug into the socket, Close the socket using the thumbwheel.

- 4. Turn the power on and press the BUS TEST key on the Troubleshooter to initiate the Pod Self Test.

If the Troubleshooter displays the message POD SELF TEST Z8000 OK, the Pod is operating properly.

If the Troubleshooter displays any message other than POD SELF TEST Z8000 OK, the Pod may not be operating properly. Make sure the Pod ribbon cable plug is properly positioned in the self test socket and try the Self Test again.

For information about Pod troubleshooting and repair, refer to Section 6.

# 2-5. CONNECTING THE POD TO THE UUT

#### WARNING

TO PREVENT POSSIBLE HAZARDS TO THE OPERATOR OR DAMAGE TO THE UUT, DISCONNECT ALL HIGH-VOLTAGE POWER SUPPLIES, THERMAL ELEMENTS, MOTORS, OR MECHANICAL ACTUATORS WHICH ARE CONTROLLED OR PROGRAMMED BY THE UUT MICROPROCESSOR BEFORE CONNECTING THE POD.

Connect the Pod to the UUT as follows:

- I. Be sure that power is removed from the UUT

- 2. Disconnect UUT analog outputs or potentially hazardous UUT peripheral devices as described in the warning at the beginning of this section.

- 3. If necessary, disassemble the UUT to gain access to the UUT microprocessor socket. If the UUT microprocessor is still in the socket, remove the microprocessor.

- 4. 'Turn the Pod self test socket thumbwheel to release the Pod plug, and remove the Pod plug from the self test socket.

- 5. Insert the Pod plug into the UUT microprocessor socket, using the proper adapter if the UUT uses a 40-pin microprocessor. Make sure the slanted corner of the Pod plug is aligned with pin I of the UUT microprocessor socket.

- 6. Reassemble the UUT using extender boards if necessary

# CAUTION

The Pod **contains active** protection circuits. To avoid damage to the Pod, turn the Troubleshooter power on before applying power to the UUT.

7. Apply power to the  $UUT_{\rm e}$

# Section 3 Microprocessor Data

# **3-I. INTRODUCTION**

This section contains microprocessor data which may he useful during operation of the Troubleshooter. This information includes descriptions of Z8000 signals and pin assignment.

# 3-2. MICROPROCESSOR SIGNALS

Table 3-1 lists all of the Z8000 microprocessor signals and provides a briefdescription of each signal. Refer to the microprocessor manufacturer's literature for complete information.

Table 3-2 is a summary of the Z8000 microprocessor signal activity.

Figures 3-I through 3-4 show the **ZXOOO** family pin assignments.

| SIGNAL NAME | DESCRIPTION                                                                                                                                                                                                                                                 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ABORT       | The Abort line is used in conjunction with the $\overline{SAT}$ line to interrupt instructions before they are completed. (Available on the Z8003 and Z8004 only.)                                                                                          |

| ADO-AD15    | These 16 tri-statemultiplexed Address/Data lines are used to address memory and for Input/Output. The lines contain address information when the Address Strobe ( $\overline{AS}$ ) linerises and data when the Data Strobe ( $\overline{DS}$ ) line rises, |

| AS          | The rising edge of this Address Strobe line indicates valid addresses.                                                                                                                                                                                      |

| BUSACK      | When this Bus Acknowledge line is Low. the CPU has relinquished control of the bus.                                                                                                                                                                         |

| BUSREQ      | The Bus Request line is driven Low to request the bus from the CPU.                                                                                                                                                                                         |

| ธิริ        | The rising edge of the Data Strobe line indicates valid data available on the multiplexed Address/Data $(\overline{AD})$ lines.                                                                                                                             |

| MREQ        | Memory Request is a tri-state output that indicates that a memory address is present on the address/data bus.                                                                                                                                               |

| Table  | 3-1.  | Signal  | Descri | otions |

|--------|-------|---------|--------|--------|

| 1 0010 | • • • | erginar | 000011 |        |

| SIGNAL NAME               | DESCRIPTION                                                                                                                                                                                                               |  |  |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <b>M</b> , <del>M</del> O | Multi-Micro In and Multi-Micro Out form part of a daisy-chain that allows sharing resources in a multi-microprocessor system.                                                                                             |  |  |

| ĪMĪ                       | A falling edge on the Non-Maskable Interrupt line requests a non-maskable interrupt. $\overline{\rm NM}$ has priority over the Vectored and Non-Vectored Interrupts,                                                      |  |  |

| NVI                       | The Non-Vectored Interrupt line Initiates a non-vectored interrupt.                                                                                                                                                       |  |  |

| CLK                       | The System Clock is a single-phase, five-volt time base,                                                                                                                                                                  |  |  |

| RESET                     | The Reset line resets the CPU,                                                                                                                                                                                            |  |  |

| R/₩                       | Read/Write indicates that the CPU is performing a read or write operation with memory or I/O.                                                                                                                             |  |  |

| SAT                       | The Segment Page Address Translation Trap line is activated by a Memory Management Unit (MMU) to interrupt the CPU while a program or data in secondary storage IS moved into main memory. (Available on the Z8003 only.) |  |  |

| SEGT                      | The Segment Trap isasserted by the Memory Management Unit (MMU) to interrupt the CPU when the MMU encounters a segment trap. (Available on the Z8001 only.)                                                               |  |  |

| SN0-SN6                   | The Segment Number lines provide a segment number for use by a Memory Management Unit. (Available on the Z8001 and 28003 only,)                                                                                           |  |  |

| STO-ST3                   | These Status lines indicate the CPU status (refer to Table 3-3 Z8000 CPU Status Codes).                                                                                                                                   |  |  |

| STOP                      | The Stop line is usually used to single-step instructions,                                                                                                                                                                |  |  |

| VI                        | This line requests a Vectored-Interrupt.                                                                                                                                                                                  |  |  |

| WAIT                      | The Wait line tells the CPU that an I/O device or the memory isnotready for a transfer of data.                                                                                                                           |  |  |

| B∕₩                       | Byte/Word specifies the nature of the 16-bit information on the address/data bus.                                                                                                                                         |  |  |

| N/S                       | Normal/System Mode indicates the CPU's present operating mode.                                                                                                                                                            |  |  |

|                           |                                                                                                                                                                                                                           |  |  |

|                           |                                                                                                                                                                                                                           |  |  |

|                           |                                                                                                                                                                                                                           |  |  |

Table 3-1. Signal Descriptions (cont)

| SIGNAL NAME                              | MNEMONIC | INPUT/<br>OUTPUT | ACTIVE<br>STATE | DRIVE |

|------------------------------------------|----------|------------------|-----------------|-------|

| Abort                                    | ABORT    | input            | low             | tri   |

| Address/Data                             | AD0-AD15 | output           | high            | tri   |

| Address Strobe                           | ĀŠ       | output           | low             | tri   |

| Bus Acknowledge                          | BUSACK   | output           | low             |       |

| BUS Request                              | BUSREQ   | input            | low             | tri   |

| Memory Request                           | MREQ     | output           | low             |       |

| Multi-Micro In                           | MI       | input            | low             |       |

| Multi-Micro Out                          | MO       | output           | low             |       |

| Non-Maskabie<br>Interrupt                | NMI      | input            | low             |       |

| Non-Vectored<br>Interrupt                | NVI      | input            | low             |       |

| System Clock                             | CLK      | input            | -               |       |

| Reset                                    | RESET    | input            | łow             | tri   |

| Read/Write                               | R/W      | output           | high/low        |       |

| Segment Page Address<br>Translation Trap | SAT      | input            | low             |       |

| Segment Trap                             | SEGT     | input            | low             | tri   |

| Segment Number                           | SN0-SN6  | output           | high            | tri   |

| status                                   | STO-ST3  | output           | high            |       |

| stop                                     | STOP     | input            | low             |       |

| Vectored Interrupt                       | VĪ       | input            | low             |       |

| Wait                                     | WAIT     | input            | low             | tri   |

| Byte/Word                                | B∕₩      | output           | high/low        | tri   |

| Normal/System Mode                       | N/S      | output           | high/low        |       |

Table 3-2. Signal Summary

Figure 3-1. 28001 Pin Assignments

Figure 3-2. 28002 Pin Assignments

Figure 3-3. 28003 Pin Assignments

Figure 3.4. 28004 Pin Assignments

# Section 4 Operating Information

# 4-1. INTRODUCTION

This section contains information which pertains to operating the Troubleshooter with Z8000-based systems. This additional information complements the information in the froubleshooter Operator and Programming manuals, and covers such items as the following:

- . Address space assignment

- . Special address functions

- . Characteristics of Z8000 memory addressing

- . Definitions and hit assignment of status lines

- . Definitions of forcing and interrupt lines

- . Definitions and characteristics of user-writable control lines

- . Bit assignments of control lines

- . Interrupt handling

- . Characteristics of Bus 'Test. Learn, and Run UU'l

- Marginal  $\bigcup \bigcup \Box$  problems

# 4-2. GETTING STARTED

After the Pod is connected to the Troubleshooter and installed in the UUT. you may see the message POD *TIMEOUT* - *ATTEMPTING RESET* displayed by the Troubleshooter as soon as any Pod operation is attempted. This message usually appears because the U UT is asserting a forcing status line: either the BUSREQ (Bus Request), or WAIT lines. Manually resetting the UUT may remove the problem, but it may be necessary to disable the status input using the Troubleshooter Setup function. Setting the corresponding Setup messages SET ENABLE xxxx? to NO disables the offending line.

If the status line remains faulty and you attempt another operation, the message ACT/VE FORCE  $L/NE \cdot LOOP$ ? appears. Pressing the MORE keyallowsyoutoseewhichlineis causing the message to appear. You can disable reporting of this error and continue operation by setting the Setup message SET TRAP ACTIVE FORCE LINE? to NO. For more information about enable lines, refer to a later section titled User Enablable Status Lines. For more information about forcing lines. refer to a later section titled Forcing Lines.

# NOTE

*Operating the Pod with the status lines disabled will cause UUT errors if the* 28000 microprocessor is required to WAIT or allow DMA accesses while under test.

If the message POD TIMEOUT- ATTEMPTING RESET remains after you disable the enablable lines, the problem may be that the UUT is not supplying a clock to the Pod. If the clock is working properly, perform a Pod self test as described in Section 2.

If the Troubleshooter displays a"  $ACTIVE \ FORCE \ LINE$  message during the performance of BUS 'TEST on a properly functioning UUT, it may be necessary to change the Bus Test address using the Setup function of the Troubleshooter, or it may be necessary to inhibit reporting of forcing line errors by using the Setup function of the Troubleshooter. or by using the forcing line error mask special address. Refer to the Forcing Line Error Mask description under the Special Features of the 28000 Pod in this section.

# 4-3. ADDRESS SPACE ASSIGNMENT

#### 4-4. Introduction

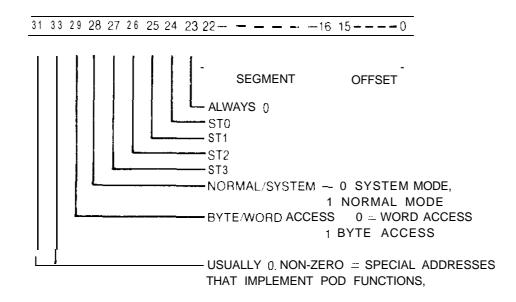

Ail of the Z8000 family of microprocessors have 16 multiplexed address lines (ADO - AD15) which allow direct addressing of 64K bytes of memory. Inaddition, the Z8001 and 28003 versions have seven segment lines (SN0-SN6) which select one of 128 64K address segments, allowing a total addressing range of 8M bytes. The 28000 can use seven data types, from 32-bit long words to individual bits.

## 4-5. Address Mapping

In order to allow the user to easily enter the complex address descriptions for the 28000, a simplified address descriptor is used for specifying addresses via the Troubleshooter.

Addresses for the segmented versions of the 28000 microprocessor (28001 and 28003) are normally defined by a" Offset (a" address within a 64K byte block) and a Segment (one of 128 possible memory blocks).

#### 64K Byte Offset Addresses

Address offsets (and addresses for non-segmented versions) are specified by bits 0-15 of the address. This provides an address offset range of 0000- FFFF. The address offset is put on lines AD0-AD15 during a bus access by the Pod.

## Address Segment Notation

The Z800] and Z8003 have additional output lines that can be used to switch between different segments of memory.

To simplify segment address components "sing the Troubleshooter. the seven segment hits appear in bits  $16\mathchar`22$  of the address.

As a" added convenience for the operator. the high byte of the address designates  $Normal/\overline{System}$  mode and  $Byte/\overline{Word}$  operation. There arc four status lines. ST0-ST3, that indicate Pod operation in the stack. program, or data space.

For example, the address

# 1962 A77E

shows an address offset of A77E in memory segment 62. The CPU's program counter registers will receive the value 6200 A77E. The upper byte indicates system mode operation and using word accesses in the stack space. These status elements are described below.

# Word and Byte Accesses

The ZKOOO family of microprocessors provides for both word and hpte accesses on the microprocessor bus. The Troubleshooter makes specifying word or byte accesses convenient for the operator by using a single bit of the address. Bit 29 of the address will be sensed by the Pod and the B/W(BYTE/WORD) line to the UUT will he set accordingly. If bit 29 is zero, then the  $B/\overline{W}$  signal will be low during the bus cycle. resulting in a word access. For byte accesses, hit 29 is set to a one.

The Z8000 Pod accepts only even addresses for word accesses. If odd addresses are specified for word access, the Troubleshooter defaults to the next lower (even) address and displays an error message.

## Normal System Mode

The Z8000 microprocessors provide a control signal  $(N/\overline{S})$  to the UUT that indicates the CPU's operating mode. This signal can be controlled through setting or clearing bit 28 in the address. If bit 2X is a one, then the Pod sets the  $N/\overline{S}$  line high, indicating the normal mode to the UUT. The system mode is indicated by setting bit 28 to zero.

Status Line

Bits 24.27 are four status lines that denote current UUT system status. Not all combination of the four status lines, the Normal/System status line, and the Byte; Word status line will occur. All possible status code combinations are shown in Table 4-I. status Codes.

Table 4-I. Status Codes

#### Special Addresses

In addition to the regular address spaces, the Pod recognizes special addresses that are used to access information in the Pod ()r to cause the Pod to perform special functions. The special addresses are of the form FOOO 00XX. These special functions include indirect vectoring of Run UUT, Quick looping, Quick RAM and ROM tests, interrupt handling, and other miscellaneous controls. These functions are discussed in the section titled Special Functions of the 28000 Pod.

For example, the address

F000 00 16

is a special Pod address containing the state of the MO output line,

# **4-6. STATUS/CONTROL LINES**

# 4-i'. Introduction

The Troubleshooter classifies the signals at the microprocessor pins into four categories: address, data. status, and control. Address and data are multiplexed on the same lines. The A: D (Address/Data) lines contain address information on the rising edge of the Address Strobe line, and valid data on the rising edge of the Data Strobe line. Status lines are inputs to the microprocessor. They provide the CPU with critical status information about the system. Control lines are outputs from the microprocessor. They are the means with which the microprocessor can control other devices in the system using bus transactions.

The Pod permits the operator to monitor the state of the status lines and to manipulate the control lines from the Troubleshooter mainframe. 'The following paragraphs describe these capabilities.

#### 4-8. Status Line Bit Assignments

When a Read Status operation is performed, the Troubleshooter displays the logic levels of each of the status lines in binary form, where "1" indicates a logic high. and a "0" indicates a logic low. To determine which digits correspond to specific status lines. refer to Table 4-2 or the Pod decal (on the bottom of the Pod).

For example: If a Read Status operation is performed and there are no active status lines and no flags set. the Troubleshooter displays:

# **READ** (a) STS = 0000 0111 11101111 OK

If a WAIT is pending, a Read Status operation will display:

```

READ (a) STS = 0000 0111 1110 1011 OK

```

| BIT      | STATUS LINES                     | BIT | CONTROL LINES |  |  |  |

|----------|----------------------------------|-----|---------------|--|--|--|

| 1 5      | SAT ACKNOWLEDGE FLAG             | 15  |               |  |  |  |

| 14       | VI ACKNOWLEDGE FLAG              | 14  | _             |  |  |  |

| 13       | NVI ACKNOWLEDGE FLAG             | 1 3 |               |  |  |  |

| 12       | NM ACKNOWLEDGE FLAG              | 1 2 | -             |  |  |  |

| 11       | TIMEOUT FLAG                     | 11  | ĀŠ            |  |  |  |

| 10       | MI                               | 10  | MÖ            |  |  |  |

| 9        | RESET                            | 9   | N/S           |  |  |  |

| a        | ** V                             | а   | MREQ          |  |  |  |

| 7        | ** N V I                         | 7   | R/₩           |  |  |  |

| 6        | ** <u>NM</u> 1                   | 6   | B/W           |  |  |  |

| 5        | <u>SAT</u>                       | 5   | DS            |  |  |  |

| 4        | POWER FAIL FLAG                  | 4   | ST3           |  |  |  |

| 3        | . ABORT (Z8003, Z8004 ONLY)      | 3   | ST2           |  |  |  |

| 2        | *** WAIT                         | 2   | S T 1         |  |  |  |

| 1        | * STOP                           | 1   | ST0           |  |  |  |

| 0        | * *** BUSREQ                     | 0   | . BUSACK      |  |  |  |

|          |                                  |     |               |  |  |  |

| _        | . FORCING LINES . USER WRITEABLE |     |               |  |  |  |

|          | ** INTERRUPT LINES               |     |               |  |  |  |

| *** USEF | R ENABLEABLE                     |     |               |  |  |  |

Table 4-2. Status and Control Line Bit Assignments

The active low level at bit 2 indicates that the WAIT line is active. Note that most status lines are active low; the exceptions are flags at bits 4 and 11-15.

# NO TE

When displaying status line error information (or other error information). the Troubleshooter displays the faulty lines as ones and good lines as zeroes rather than showing logic levels.

# NOTE

The flag bits 4 and 11-15 do not represent particular 28000 signals, but are generated within rhe Pod to indicate significant events to the Troubleshooter operator. (Refer to the section titled Status Lines Generated by the Pod.)

# 4-9. User-Enablable Status Lines

The ZXOOO has two inputs (BUSREQ and WAIT) which the operator can individually enable or disable using the Troubleshooter's Setup function. When these inputs are disabled, the UUT-generated signals appearing at these inputs are prevented from affecting the Pod.

Example: A  $\overline{WA^{\pm}}$  Lie stuck at the active low level would cause the Z8000 within the 201 to step and wait for a device to accept a data transfer, preventing normal 201 Troubleshooter operation. After disabling this input to the Z8000 using the Setup function of the Troubleshooter, the WAIT signal is prevented from holding up normal 202 operation. Also see the discussion of the Timeout Flag, Paragraph 4-12.

Either of these status lines may be enabled or disabled using the Troubleshooter Setup function. The relevant Setup display message is SET-ENABLE xxxxx? where xxxxx is either WAIT or BUSREQ. Pressing the YES key on the Troubleshooter enables the status line, pressing the NO key disables the status line. The default for both lines is YES -- enabled.

# NOTE

During Troubleshooter Setup, selecting the message SET-ENABLE xxxxx? NO prevents the enable line from affecting the operation of the Pod (although the Pod can still detect whether the line is high or low). This differs from selecting the Troubleshooter Setup message SET-TRAP ACTIVE FORCE LINE? NO which does not prevent an enable line from affecting the operation of the microprocessor, but does prevent the active condition of a disabled line from being reported on the Troubleshooter display.

# 4-10. Status Flags Generated by the Pod

The Z8000 Pod provides several status flags that do not represent particular Z8000 signals. These flags are used to provide helpful information to the operator. The Podgenerated flags are: Power Fail, Timeout, Non-Maskable Interrupt Acknowledge, Non-Vectored Interrupt Acknowledge, Vectored Interrupt Acknowledge, and Segment Page Address Translation Trap Acknowledge,

# 4-11. POWER FAIL STATUS FLAG

The Power Fail Status Flag is set high by the Pod whenever the UUT power supply voltage drops below 4.5V or rises above 5.5V. This flag is sensed by the mainframe and, if set, causes a BAD POWER SUPPLY message to be displayed on the Troubleshooter.

# 4-12. TIMEOUT FLAG

The Timeout Flag is set high by the Pod whenever a Pod timeout error occurs. It indicates that a UUT access was prematurely aborted by the Pod's watchdog timer. This will occur if the Pod is in the Fast mode (see the description of Special Address F000 0017) and the  $\overline{WAIT}$  line is stuck low.

# 4-13. NON-MASKABLE INTERRUPT ACKNOWLEDGE FLAG

The Non-Maskable Interrupt Acknowledge Flag is set high by the Pod whenever the CPU processes a Non-Maskable Interrupt.

# 4-14. NON-VECTORED INTERRUPT ACKNOWLEDGE FLAG

The Non-Vectored Interrupt Acknowledge Flag is set high by the Pod whenever the CPU processes a Non-Vectored Interrupt.

# 4-15. VECTORED INTERRUPT ACKNOWLEDGE FLAG

The Vectored Interrupt Acknowledge Flag is set high by the Pod whenever the CPU processes a Vectored Interrupt.

# 4-16. SEGMENT PAGE ADDRESS TRANSLATION TRAP ACKNOWLEDGE FLAG

The Segment Page Address Translation Trap Acknowledge Flag is set high by the Pod whenever the CPU processes a Segment Page Address Translation Trap interrupt.

# 4-17. Forcing Lines

Forcing lines are a special category of status lines which, when active, can force the microprocessor into some specific state or action.

The following signals are classified as forcing lines on Z8000 microprocessors: RESET, WAIT, STOP, BUSREQ, and on the Z8003 and Z8004 only, ABORT. The status bits for these functions are shown on the Pod decal and in Table 4-2.

If one of these lines is asserted, the Troubleshooter displays the error message ACTIVE FORCE LINE (@ aaaa)-LOOP?. The ACTIVE FORCE LINE error message helps isolate status bies which are not functioning properly.

Notice that two of the forcing lines, WAIT and BUSREQ, are user-enablable lines. If these user-enablable lines are disabled (via the Setup function or a Special Address), their inputs to the Pod microprocessor are disabled, but the Pod continues to monitor their condition; if they are asserted, the Pod reports to the Troubleshooter that a forcing line is active. If these lines are enabled, they are not considered forcing lines, even when they are active, and no ACTIVE FORCE LINE message will be displayed.

## 4-18. Interrupt Lines

interrupt inputs to the Z8000 consist of the four status lines  $\overline{NMI}$ ,  $\overline{NVI}$ ,  $\overline{VI}$ , and  $\overline{SEGT(SAT)}$ . The Pod will enable these interrupt lines and gather interrupt information if interrupts have been enabled using the Troubleshooter SETUP function. For more detail, refer to the section titled Interrupt Handling.

#### NOTE

The reporting of interrupt request lines is disabled at power on. Reporting of active interrupt lines is enabled by selecting the Troubleshooter Setup function message SET-TRAP ACTIVE INTERRUPT? and pressing the YES key.

## 4-19. User-Writable Control Lines

The Z8000 has a control line which the 'Troubleshooter can set high or low with the Write Control function. This feature is used by Bus Test to check a line which cannot be toggled by normal read and write operations. It is also useful for helping troubleshoot these lines. The Write Control function is described in the following paragraphs as it pertains to the Z8000 Pod. Note that the Write Control function only sets a line low (active) for one UUT bus cycle just long enough to verily that it can be driven.

The Write Control and Data 'Toggle Control Troubleshooter functions require the entry of binary digits to specify the desired level of each user-writable control line.

The one user-writable control line in the Z8000 Pod is BUSACK. To drive the BUSACK line low, use a WRITE (@ CTL = 0 command.

#### 4-20. Control Line Bit Assignments

When performing a Bus Test or various other Troubleshooter functions, the I roubleshooter may detect that one or more control lines are not drivable. For example, the I roubleshooter might detect that the IX line is not drivable. The Troubleshooter will then display the message *CTL ERR 0000000 00100000-LOOP?*. The zeros and ones correspond to the kit numbers assigned to the control lines as listed in Table 4-2 and on the label on the back of the Pod. Bit 5 is set to I because the DS line was detected as not drivable. All error messages that pertain to non-drivable control lines use the same bit number assignments as listed in I able 4-2.

# 4-21. SPECIAL FEATURES AND CONTROLS OF THE **Z8000** POD

The Z8000 Pod offers several special functions which enhance its usefulness. These special functions reside in the Pod rather than the Troubleshooter and are accessed by reading or writing to special addresses outside the standard address space of the Z8000 microprocessor. I he special addresses are listed in T able 4-3.

# 4-22. QUICK FUNCTIONS

The Pod can perform three "quick" functions: the Quick-Looping Read and Write, the Quick RAM Test, and the Quick ROM Test. As their names imply, the advantage of the Quick functions is that they execute faster than the corresponding mainframe functions (Looping Read and Write, RAM Test and ROM Test). The software routines that control Quick functions reside in the Pod and not in the Troubleshooter, reducing communication overhead and greatly reducing execution time. The special addresses are listed in Table 4-3.

| ADDRESS    | DESCRIPTION                                        |  |  |

|------------|----------------------------------------------------|--|--|

| FOOO 0000  | Read TMT acknowledge word                          |  |  |

| FOOO 0001  | Read NVI acknowledge word                          |  |  |

| FOOO 0002  | Read                                               |  |  |

| FOOO 0003  | Read SAT acknowledge word                          |  |  |

| FOOO 0004  | Fast-looping read/write at last address            |  |  |

| FOOO 0005  | Read/write default high address                    |  |  |

| FOOO 0006  | Read/write fast RAM increment                      |  |  |

| FOOO 0007  | Read/write fast RAM start high address             |  |  |

| FOOO 0008  | Read/write fast RAM start offset                   |  |  |

| FOOO 0009  | Read/write fast RAM end high address               |  |  |

| F000 000A  | Read/write fast RAM end offset                     |  |  |

| F000 000B  | Read/write fast ROM start high address             |  |  |

| F000 000C  | Read/write fast ROM start offset                   |  |  |

| F000 000D  | Read/write fast ROM end high address               |  |  |

| F000 000E  | Read/write fast ROM end offset                     |  |  |

| F000 000F  | Read fast RAM error high address; ROM checksum     |  |  |

| FCQO 0010  | Read fast RAM error low address! Inactive ROM bits |  |  |

| FOOO 0011  | Read/write refresh enabled                         |  |  |

| FOOO 0012  | Readiwrite refresh rate                            |  |  |

| FOOO 0013  | Read/write transparent read high address           |  |  |

| FOOO 0014  | Read/write transparent read offset                 |  |  |

| FOOO 0015  | Read/write runuut FCW                              |  |  |

| FOOO 0016  | Read/write state of MO output                      |  |  |

| F000 0017  | Read/write state of fast mode                      |  |  |

| FOOO 0018  | Read/write state of continuous Interrupt flag      |  |  |

| FOOO 0019  | Read last address high errors (no dummy read)      |  |  |

| F000 001A  | Read last address low errors (no dummy wad)        |  |  |

| F000 001 B | Read ast data drivability (no dummy read)          |  |  |

| F000 001 C | Read last control errors (no dummy read)           |  |  |

| F000 001 D | Read last forcing line errors (no dummy read)      |  |  |

| F000 001 E | Read last status (no dummy read)                   |  |  |

| F000 001 F | Read last error summary (no dummy read)            |  |  |

| FOOO 0020  | Read/write control drivability mask                |  |  |

| F000 0021  | Read/write forcing line reporting mask             |  |  |

| FOOO 0022  | Read selftest error. write selftest disable        |  |  |

Table 4-3. Special Addresses

Appendix A in this manual lists a Troubleshooter program that makes the Pod's Quick functions operate. from the perspective of the operator, like standard Troubleshooter functions. Using this program, the operator selects the desired functions, then is prompted for parameters in same manner as the standard Troubleshooter functions. This method may he preferable for some uses over the normal method of loading individual special addresses that is described in subsequent paragraphs.

The program is presented in two forms: as a standard 'Troubleshooter program, and as a source program for the optional 9010 Language Compiler. The 9010 Language Compiler program is available for several common mainframe computers and controllers. Contact Fluke Customer Service for details.

#### 4-23. Quick-Looping Read or Write

The Quick-Looping Read or Write function is useful for enhanced viewing on an oscilloscope that is synchronized to the TRIGGER OUTPUT pulse (available on the Troubleshooter rear panel). If a signal trace on the oscilloscope screen is dim due to a low repetition rate. the Quick-Looping function can increase the repetition rate to make the signal trace much more visible.

#### NOTE

The Address Sync mode will synchronize the Troubleshooter TRIGGER OUTPUT to the beginning of the bus cycle. The Data Sync mode may be more useful to check for valid data. Refer to the section titled Probe and Oscilloscope Synchronization Modes for details of the available synchronization modes..

To select the Quick-Looping function, first perform a standard read or write operation at the desired address. Then do a *READ* or WRITE @ *F0000004*. The Pod first performs a read or write operation in the normal manner. reporting to the Troubleshooter any U UT system errors detected (such as *ACTIVE FORCE LINE*, or *CTL ERR*, etc.): then the Pod enters the Quick-Looping mode where the read or write operation is performed many times faster than the ordinary Looping function specified by pressing the LOOP key on the Troubleshooter keyboard. During the Quick Loop, the Pod does not check for any UUT System errors. Quick-Looping continues until the operator selects another operation.

For example, if the operator specifies the operation READ (a) 1800 0000, the READ (a) F000 0004 will perform a looping read operation at the address 00 0000 (with status code bits of 1000 and the CPU in the Normal mode). If the operator specifies the operation WRITE (a) 1802 00FE = 8C17, WRITE (a) F000 0004 ENTER ENTER will perform a looping write operation at address 02 OOFE (with status code hits of 1000), writing the data 8C17.

The Quick-Looping function may he used for read or write operations at any of the valid 28000 addresses listed in Table 4-3.

If both error reporting and the Quick-Looping feature are desired. you may apply the ordinary Troubleshooter Looping function to the Quick-Looping read or write, such as *READ* @ 1812 3456 ENTER READ @ F000 0004 ENTER LOOP. The Troubleshooter will command read operations at address 12 3456 at the normal looping speed with full error reporting. For every ordinary read operation, the Pod will interject several Quick-Looping read operations (with no error reporting) which will enhance oscilloscope viewing.

The Special Addresses used with the Quick-Looping function are described in Table 4-5.

4-9

|   |           | Table 4-4. Special Address Summary              |                                                                  |  |

|---|-----------|-------------------------------------------------|------------------------------------------------------------------|--|

|   | ADDRESS   |                                                 | DESCRIPTION                                                      |  |

|   | FOOO 0000 | NMI Acknowledge Word                            | (paragraph 4-27)                                                 |  |

|   | FOOO 0001 | NVI Acknowledge Word                            | (paragraph 4-27)                                                 |  |

|   | FOOO 0002 | $\overline{V}I$ Acknowledge Word (              | (paragraph 4-27)                                                 |  |

|   | FCOO 0003 | SAT Acknowledge Word                            | d (paragraph 4-27)                                               |  |

|   | FOOO 0004 | Fast Looping Read/Write                         | e at Last Address (paragraph 4-23, <b>4-28</b> )                 |  |

|   | FOOO 0005 | Default High Address (                          | paragraph 4-29)                                                  |  |

|   | FOOO 0006 | Fast RAM/ROM Test In                            | crement (paragraph 4-24. 4-25)                                   |  |

|   | F00000007 | Fast RAM Test Start Hig                         | h Address (paragraph 4-24)                                       |  |

|   | FOOO 0008 | Fast RAM Test Start Of                          | fset (paragraph 4-24)                                            |  |

|   | FOOO 0009 | Fast RAM Test End Hig                           | h Address (paragraph 4-24)                                       |  |

|   | F000 000A | Fast RAM Test End Off                           | set (paragraph 4-24)                                             |  |

|   |           | Code                                            | Meaning                                                          |  |

|   |           | XX00                                            | No test requested                                                |  |

|   |           | ХХВО<br><b>ХХВ</b> 1                            | Busy. R/W test in progress<br>Busy, performing decode test       |  |

|   |           | xxco                                            | Complete, no errors                                              |  |

|   |           | XXFO<br>XXF1                                    | Fail Read/Write test<br>Failed Address Decode test               |  |

|   |           | хх                                              | Indicates the upper byte of the current RAM offset being tested. |  |

|   | F000 000B | Fast ROM Test Start Hi                          | gh Address (paragraph 4-25)                                      |  |

|   | F000 000C | Fast ROM Test Start Offset (paragraph 4-25)     |                                                                  |  |

|   | F000 000D | Fast ROM Test End High Address (paragraph 4-25) |                                                                  |  |

|   | F000 000E | Fast ROM Test End Offset (paragraph 4-25)       |                                                                  |  |

|   |           | Code                                            | Meaning                                                          |  |

| 4 |           | XX00                                            | No test requested                                                |  |

|   |           | ХХВО                                            | Busy, test in progress                                           |  |

|   |           |                                                 |                                                                  |  |

# Table 4-4. Special Address Summary

|                                                                      | Table 4-4. Special Address Summary (cont)                            |  |  |

|----------------------------------------------------------------------|----------------------------------------------------------------------|--|--|

| ADDRESS                                                              | DESCRIPTION                                                          |  |  |

|                                                                      | XXC0Complete. no errorsXXC1Complete. inactive bits                   |  |  |

|                                                                      | XX Indicates the upper byte of the current ROM offset being tested,  |  |  |

| F000 000F                                                            | Fast RAM Test Error High Address (paragraph 4-25)                    |  |  |

|                                                                      | Fast ROM Test Checksum (paragraph 4-24)                              |  |  |

| FOOO 0010                                                            | Fast RAM Test Error Low Address (paragraph 4-24)                     |  |  |

|                                                                      | Fast ROM Test Inactive Bits (paragraph 4-25)                         |  |  |

| FOOO 0012                                                            | Read Last Test Status (paragraph 4-31)                               |  |  |

| FOOO 0013                                                            | Run UUT FCW (paragraph 4-32)                                         |  |  |

| FOOO 0014                                                            | Transparent Read High Address (paragraph 4-33)                       |  |  |

| FOOO 0015                                                            | Transparent Read Offset (paragraph 4-33)                             |  |  |

| FOOO 0016                                                            | State of MO Output (paragraph 4-34)                                  |  |  |

| FOOO 0017                                                            | Refresh Enabled (paragraph 4-35)                                     |  |  |

| FOOO 0018                                                            | Refresh Rate (paragraph 4-36)                                        |  |  |

| FOOO 0019                                                            | State of Fast Mode (paragraph 4-37)                                  |  |  |

| FOOO 001 A                                                           | State of Continuous Interrupt Flag (paragraph 4-38)                  |  |  |

| F000 001 B                                                           | Last Address High Drivability Error (No Dummy Read) (paragraph 4-39) |  |  |

| FOOO 001 C                                                           | Last Address Low Drivability Error (No Dummy Read) (paragraph 4-39)  |  |  |

| F000 001D                                                            | Last Data Drivability Error (No Dummy Read) (paragraph 4-39)         |  |  |

| I<br>FOOO 001E Last Conirol Errors (No Dummy Read) (paragraph 4-39)  |                                                                      |  |  |

| F000 001 F Last Forcing Line Errors (No Dummy Read) (paragraph 4-39) |                                                                      |  |  |

| FOOO 0020                                                            | Last Status (No Dummy Read) (paragraph 4-39)                         |  |  |

| FOOO 0021                                                            | Last Error Summary (No Dummy Read) (paragraph 4-39)                  |  |  |

|                                                                      |                                                                      |  |  |

|                                                                      |                                                                      |  |  |

| ļ                                                                    |                                                                      |  |  |

| Table 4-4. Special Address Summ | nary ( | (cont) |

|---------------------------------|--------|--------|

|---------------------------------|--------|--------|

| ADDRESS   | DESCRIPTION                  |                                                                                                                                                                                                                                                                                   |  |

|-----------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|           | SYSTEM FAULT BYTE XXXX       | ADDRESS LINES NOT DRIVABLE(BIT0)<br>ADDRESS LINES NOT DRIVABLE (BIT1)<br>CONTROLLINES NOT DRIVABLE (BIT2,<br>FORCING LINES PENDING AND DISABLED(BIT3<br>INTERRUPT PENDING(BIT41<br>ILLEGAL ADDRESS(BIT5)<br>SELF TEST (BIT6)<br>UUT POWER FAILURE (BIT7)                          |  |

| F0000022  | Control Drivability Error Re | porting Mask (paragraph 4-40)                                                                                                                                                                                                                                                     |  |

| FOOO 0023 | Forcing Line Error Reportin  | g Mask (paragraph 4-40)                                                                                                                                                                                                                                                           |  |

| FOOO 0024 | Self Test Diagnostic (paragr | aph 4-41)                                                                                                                                                                                                                                                                         |  |

|           | FFFF                         | Hex FFFF indicates that the Pod passed the internal self test without any errors being detected.                                                                                                                                                                                  |  |

|           | ACTIVE FORCE LINE            | After receiving an Active Force Line error<br>message. pressing the MCRE key on the<br>Troubleshooter will provide a bit map showing<br>the status lines. Refer to Figure 4-2. or the Pod<br>decal. for forcing line bit assignments. A "1"<br>indicates a defective status line. |  |

|           | CTL ERR                      | Press the MORE key to display a bit map of the control lines that the Pod self test has determined are probably faulty. A "1" signifies a bad control line.                                                                                                                       |  |

|           | ADDR ERR                     | The MORE key displays a map of the address/data lines that failed a simple read/write test (see discussion below).                                                                                                                                                                |  |

|           | DATA ERR                     | The MORE key will display a map of the address/data lines that failed a simple drivability test (see discussion below).                                                                                                                                                           |  |

|           | BAD PWR SUPPLY               | The Pod has measured an out-of-tolerance power supply voltage.                                                                                                                                                                                                                    |  |

|           | 1                            | The Pod has computed an internal ROM signature that differs from what was expected,                                                                                                                                                                                               |  |

|           | 2                            | The Pod has found a Read/Write error in its internal RAM.                                                                                                                                                                                                                         |  |

|           |                              |                                                                                                                                                                                                                                                                                   |  |

2

N S F

١ г ł ł Е ..... 8 ٢ ٢ f ( Е г ١ ŧ *.*. ¢ C ¢

# Table 4-4. Special Address Summary (cont)

| UNCTION                   | SPECIAL ADDRESSES<br>AND OPERATIONS | DESCRIPTION OF USE                                                                                                                                                                                                                     |

|---------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|