Operation, Maintenance and Service Manual

# GOAL IV

14600 Winchester Blvd. Los Gatos, CA 95030 Telephone (408) 374-2440 Telex 357-488

# TABLE OF CONTENTS

|            | Section                                            | Page           |

|------------|----------------------------------------------------|----------------|

| Α.         | Introduction and Warranty                          | 0 & M - 1      |

| В.         | New Machine Setup Procedure                        | 0 & M - 2      |

| C.         | Service Access                                     | 0 & M - 2      |

| D.         | New Machine Checkout                               | 0 & M - 3      |

| E.         | Game Sequence                                      | 0 & M - 4      |

| F.         | Circuit Board Adjustments                          | 0 & M - 7      |

| G.         | Static Modification                                | 0 & M - 8      |

| н.         | T.V. Monitor Adjstument                            | 0 & M - 9      |

| I.         | Coin Acceptor: Operation, Adjustment & Maintenance | 0 & M - 10     |

| J.         | General Maintenance                                | 0 & M - 13     |

| ĸ.         | Troubleshooting                                    | 0 & M - 13     |

| L <b>.</b> | Detailed Circuit Description                       | PCB - 1        |

|            | Introduction                                       | PCB - 1        |

|            | Test Equipment                                     | PCB - 1        |

|            | Adjustments                                        | PCB <b>-</b> 3 |

|            | General Troubleshooting Approach                   | PCB <b>-</b> 3 |

|            | Block Diagram Description                          | PCB - 4        |

|            | Power Supply                                       | PCB - 7        |

|            | Computer Clock                                     | PCB - 8        |

|            | Horizontal Sync Circuitry                          | PCB - 10       |

|            | Vertical Sync Circuitry                            | PCB - 11       |

|            | Sync Summing                                       | PCB ~ 13       |

|            | Windows                                            | PCB - 14       |

|            | Electronic Latch Circuit                           | PCB - 15       |

|            | Chadit Cinquit                                     | DOD 16         |

| ! |  |  |

|---|--|--|

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

# Table of Contents (continued)

|    |                              | Section       | <u>Page</u>     |

|----|------------------------------|---------------|-----------------|

| ∟. | Detailed Circuit Description | n (continued) |                 |

|    | Start Circuit                |               | PCB <b>-</b> 19 |

|    | Time Line Circuit            |               | PCB - 20        |

|    | Playfield Circuit            |               | PCB - 21        |

|    | Game Select Circuit          |               | PCB <b>-</b> 23 |

|    | Players Circuit              |               | PCB - 23        |

|    | Serve Timing Circuit         |               | PCB <b>-</b> 31 |

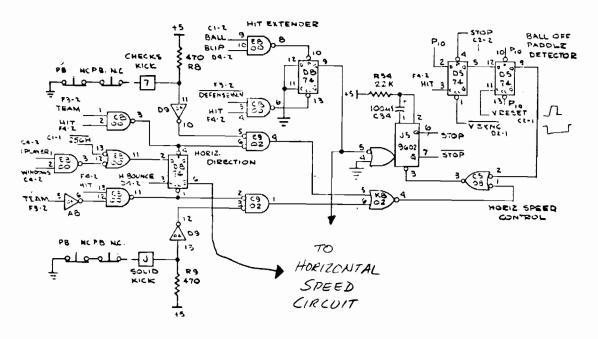

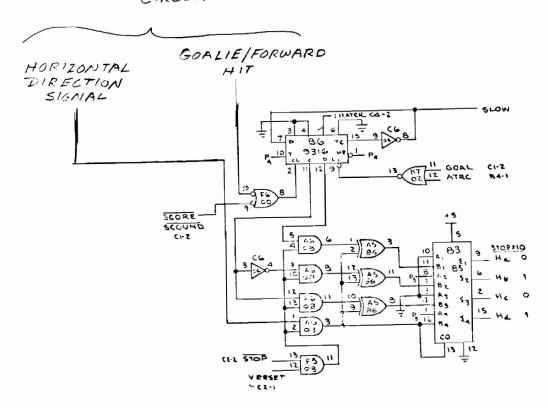

|    | Catch/Kick/Horizontal Dire   | ction Circuit | PCB - 33        |

|    | Ball Motion                  |               | PCB - 36        |

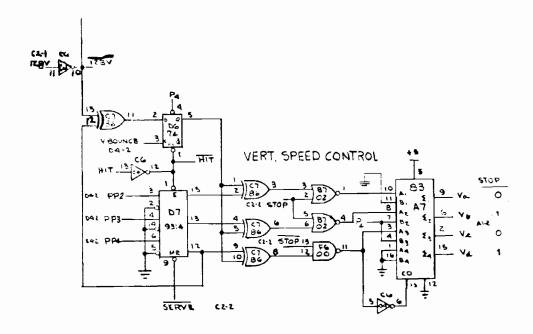

|    | Vertical Direction and Spee  | d Circuit     | PCB <b>-</b> 38 |

|    | Horizontal Direction and Sp  | eed Circuit   | PCB - 40        |

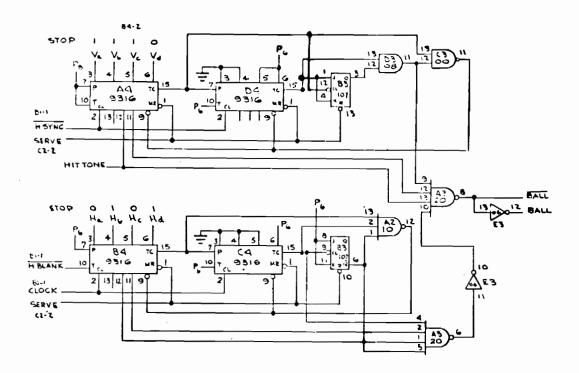

|    | Ball Motion Circuit          |               | PCB <b>-</b> 43 |

|    | Hit Circuit                  |               | PCB <b>-</b> 45 |

|    | Moving Hole Circuit          |               | PCB - 46        |

|    | Window/Miss/Bounce Circu     | it            | PCB - 48        |

|    | Sound Circuit                |               | PCB <b>-</b> 51 |

|    | Score Circuit                |               | PCB - 52        |

|    | Video Summina Circuit        |               | PCB - 56        |

# A. Introduction/Warranty

Goal IV is a video amusement device which simulates a soccer game. It may be used by one, two, three or even four players.

This game has been designed with solid state circuitry to be as maintenance free as possible. However, as with all devices, mechanical or electrical, there may be minor problems.

If the printed circuit board (PCB) fails within the one-year\* warranty period, contact the distributor from whom the game was originally purchased for replacement or repair instructions. All such warranty returns must be accompanied by completed warranty return forms. Any PCB repairs attempted by anyone other than authorized Atari Service Center personnel will void the warranty.

If the PCB fails after the warranty period has expired, it will be repaired for a nominal parts and labor charge.

Atari, Inc. warrants the T.V. monitor for a period of thirty days commencing the day of shipment from the Atari factory. If the monitor fails within that period, immediately contact the distributor from whom the game was originally purchased for repair or replacement instructions. Any T.V. repairs (other than replacement of fuses or adjustments) attempted during the warranty period by anyone other than authorized Atari Service Center personnel will void the warranty.

If the T.V. monitor fails <u>after</u> the warranty period has expired, it may be returned to the distributor where it will be repaired for a nominal parts and labor charge, or it may be taken to any competent T.V. repair shop.

<sup>\*</sup>From date of shipment from the factory.

## B. New Machine Setup Procedure

Before turning this machine on, inspect it carefully for any damage which may have occurred during shipment.

Inspect both interior and exterior of the machine for any obvious damage to the cabinet or internal components. Check for cracked or broken cabinet parts, assemblies pulling loose, broken or disconnected wires or foreign objects shorting electrical connections.

After the machine has been plugged in and turned on, perform the checkout procedure.

#### C. Service Access

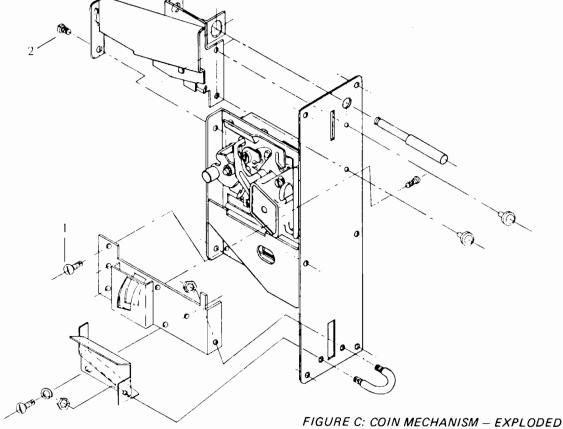

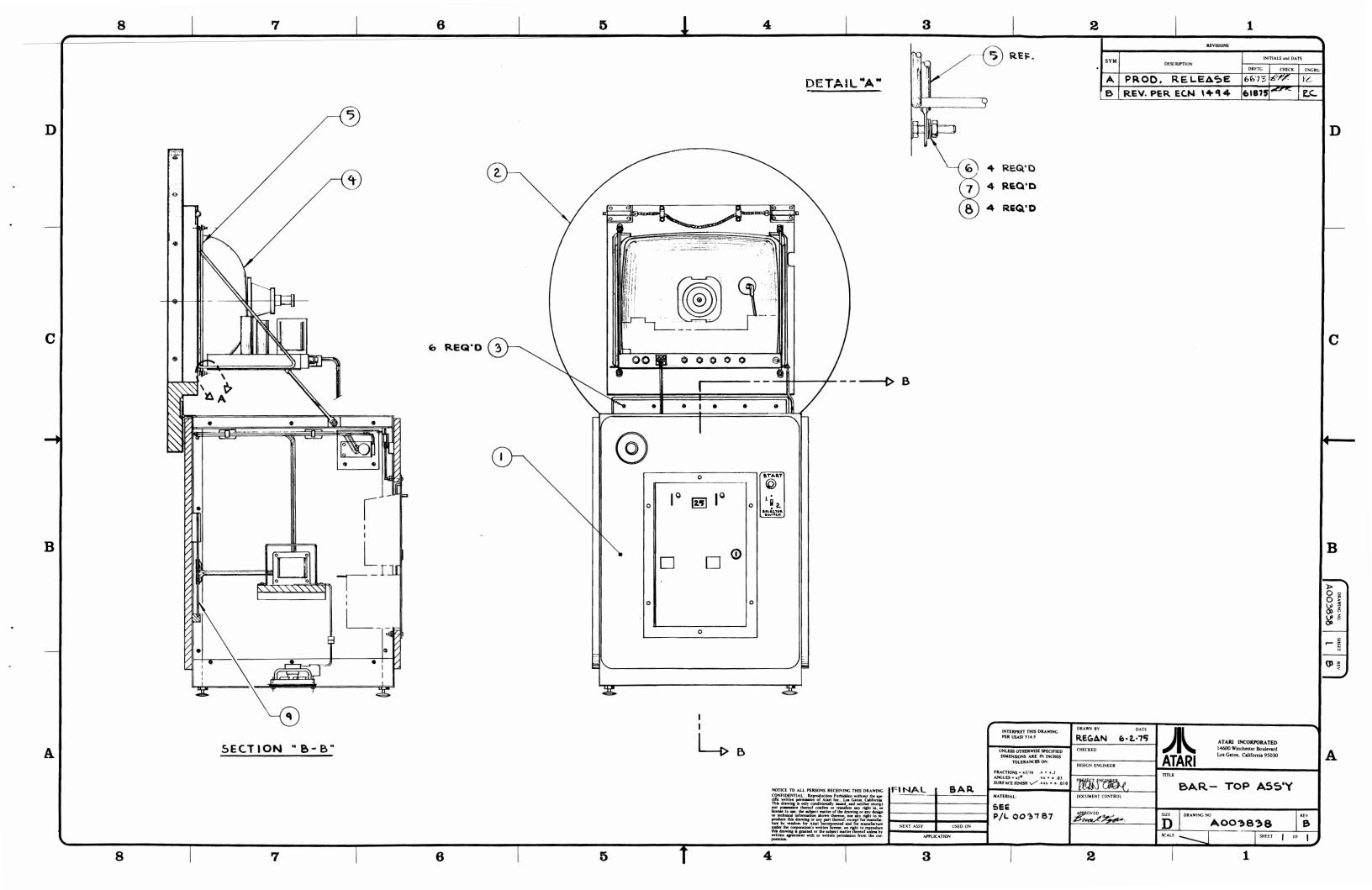

All servicing is performed inside the machine through the hinged top that provides access to all components, sub-assemblies and adjustments with the exception of the coin box.

The coin door is located on the front of the machine underneath the control panel. To remove the coins, unlock the metal coin door, grasp the door lip and pull out the coin box.

To reach the interior of the machine, unlock coin door and reach upwards just inside the door opening. Near the top of the interior compartment is a chain. Pull down on this chain and, with the other hand, lift up the hinged top. To hold top open, lift up metal support rod on the right side of base's top edge and insert end of rod into oval slot at right front side of TV chassis.

Please note that two interlock switches are provided for the game, so that the machine is completely turned off whenever either the top or coin door is opened. These switches protect the operator from accidental shock and so they must always be kept in perfect working order. If the machine is adjusted or tested

with the rear door open, the interlock switches must be placed in the closed (or "on" position) by pulling out the white actuator shafts.

WARNING: The covered black terminal block carries full line voltage whenever the line plug is connected to a power outlet. This cover should be removed only with the line plug disconnected. Do not leave off the cover once it has been removed.

#### D. New Machine Checkout

As each new machine leaves the factory, every component and sub-assembly is carefully checked for proper operation. However, since parts may have been damaged or adjustments changed during shipping, the following checkout procedure must be repreated prior to placing the machine on location:

- 1. Inspect both the exterior and interior of the machine for obvious shipping damage such as cracked or broken cabinet parts, sub-assemblies broken loose, etc.

- 2. Carefully inspect the interior of the machine to see that all solder joints, slip—on connectors and plug—in type connectors are firmly seated. Pay particular attention to the PCB edge connector, the fuses and the slip—on connectors to the potentiometers, the kick switches, the start switch and the mode selector switch. Also check the connections to the coin switch, the T.V. monitor, the interlock switches and all the other Molex—type connectors.

- 3. Plug the machine in, and pull out the white actuator shafts of the interlock switches if the rear door is open. Inspect the CRT (cathode ray tube) image for steady and sharp picture which exhibits the proper levels of brightness and contrast.

- 4. Insert several old and new coins into the coin acceptor. No genuine coin should be rejected and each coin insertion should step the coin counter one digit.

Depress the coin rejector button to make sure that the linkage is operating smoothly.

- 5. Coin insertion should produce game credit which is indicated by a small red light (LED) in the start switch button mounted on the control panel.

- 6. Depress the start switch button and check for proper game sequence, making sure that all aspects of the game (i.e. paddle display and control, score count and display, ball motion, etc.) are functioning correctly. If you are not familiar with the game sequence for Goal IV, read the game sequence description.

- 7. Operate all the players' paddle controls to make sure the potentiometers exhibit no evidence of "noise" (erratic jumping of the paddle image) as the paddles traverse the screen, and that all the kick switches operate when firmly pressed. Please note that all the kick switches operate when firmly pressed. The machine will automatically kick if the kick switch is not pressed within three seconds.

- 8. The door locks should turn to the "locked" and "unlocked" positions smoothly and the doors should open and close without binding.

- 9. The interlock switches must turn off the entire machine when the rear door is opened. (SEE THE "WARNING" UNDER SECTION "C".)

- 10. Check the carriage bolts which connect the metal legs to the cabinet to make sure that the stress and lock washers are in place, and the nuts are tightly screwed down.

#### E. Game Sequence

Before the coin is inserted and the start switch pressed, the CRT will display the "ATTRACT MODE" - a ball rebounding from the playfield walls and the players' paddles.

Coin insertion lights the red credit lamp in the start switch button, indicating there is game credit and pressing this button begins the new game.

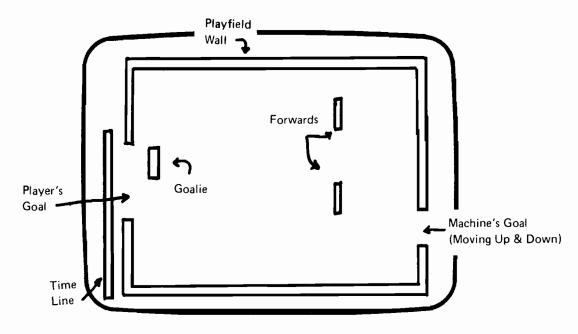

At this point, the goals and the time line appear. The goals are two open areas in the playfield perimeter; the object of the game is to shoot the ball into the opposing players' goal. The time line is an ever-shortening line located on the CRT outside the left edge of the playfield perimeter. This line indicates the amount of time left to play the game. When the time line completely disappears, the game is over.

The game can be played in either of two modes by changing the position of the mode selector switch located below the start switch on the front panel. If this switch is set to position "1", the game will be conditioned to "one player vs. the machine." If the mode selector switch is set to position "2", the machine will be conditioned for "solid players vs. checked players."

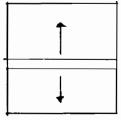

MODE #1: If the mode selector switch is set to position "1" (one player vs. the machine), the game sequence is as follows: Coin insertion lights the credit lamp and the game commences when the lighted start button is pressed, producing this CRT configuration:

The player has three paddles (or "men") and the machine has none. The player has a large goal through which the ball can easily pass if the player is not alert. The "machine" has a small, moving goal and a carefully aimed shot is required to place the ball in this moving goal.

The machine serves automatically from the middle of the CRT. The object of the game is to bounce or kick the ball into the machine's goal. One of the player's potentiometers controls the player's forward men (the "forwards") and the other is used to maneuver the player's goalie.

The ball is stopped when it contacts one of the men. Depressing the potentiometer knob kicks the ball from that man. The direction of the kick is manipulated by moving the paddle image before pressing for the kick. If the knob is not pressed within three seconds, the machine automatically kicks the ball. If the man is moved off the ball, the ball is kicked.

A point is scored when the ball passes through the opponent's goal areas, and the scores are momentarily flashed on the screen until the next serve. Making a goal at the opponent's side produces a higher score for your side.

The game is played in this fashion until the time line completely disappears.

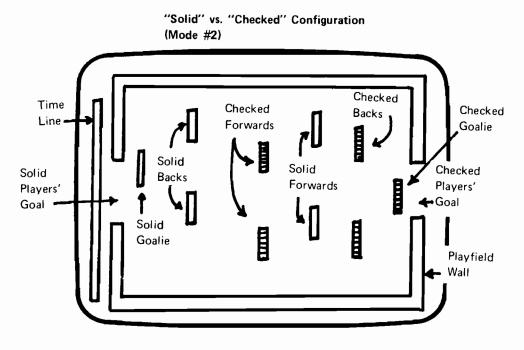

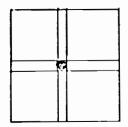

MODE #2: If the mode selector switch is set to position "2", the machine will be conditioned to "solid players vs. checked players" and the game sequence is as follows: Coin insertion lights the credit lamp indicating there is game credit, and the game commences when the start switch button is pressed.

The CRT configuration displayed for this mode is a playfield in which there are two types of players: solid men and checked men. One player controls the solid team and another operates the checked team. However, if desired, one or two players may operate each team so that three or four players may be accomodated.

When the machine is conditioned to make #2, each side has five men: two forwards, two backs and one goalie. Each side has two potentiometers ("pots"): one pot controls the forwards and the other controls the defense men (the backs and the goalie). Each side also has a goal area and both goals are of equal size.

The machine will serve automatically from the middle of the CRT and the object of the game is to shoot the ball into the opposing player's goal. When a goal is scored, the scores for both sides are momentarily flashed on the screen until the next ball is served.

The ball is stopped when it contacts the forwards or the goalies and is bounced when it contacts the backs. The stopped ball is kicked from the man by firmly pressing either of the potentiometer knobs. The angle of the kicked ball can be manipulated by moving the man slightly before pressing for the kick. If the

knob is not pressed within three seconds, the machine will kick the ball automatically. If the man is moved off of the ball, the ball is kicked.

The game continues in this fashion until the time line completely disappears, at which time the game ends and the attract mode is restarted.

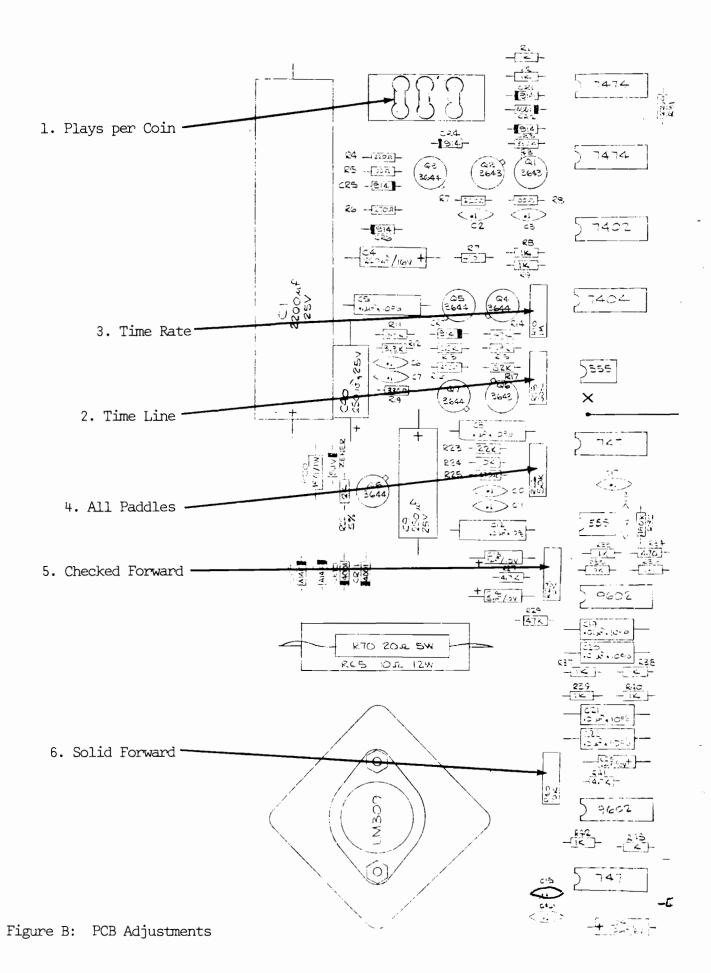

# F. Circuit Board Adjustments

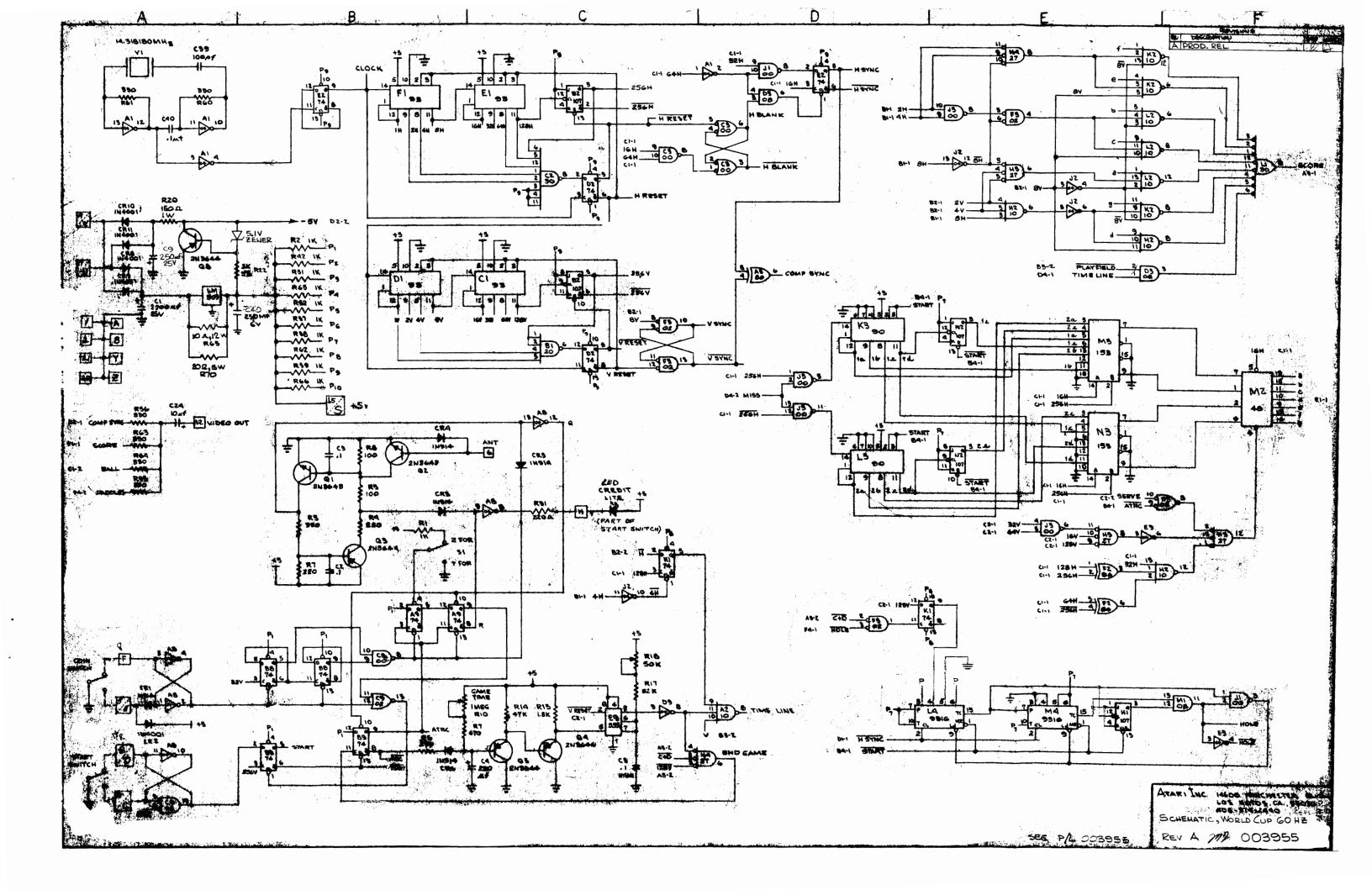

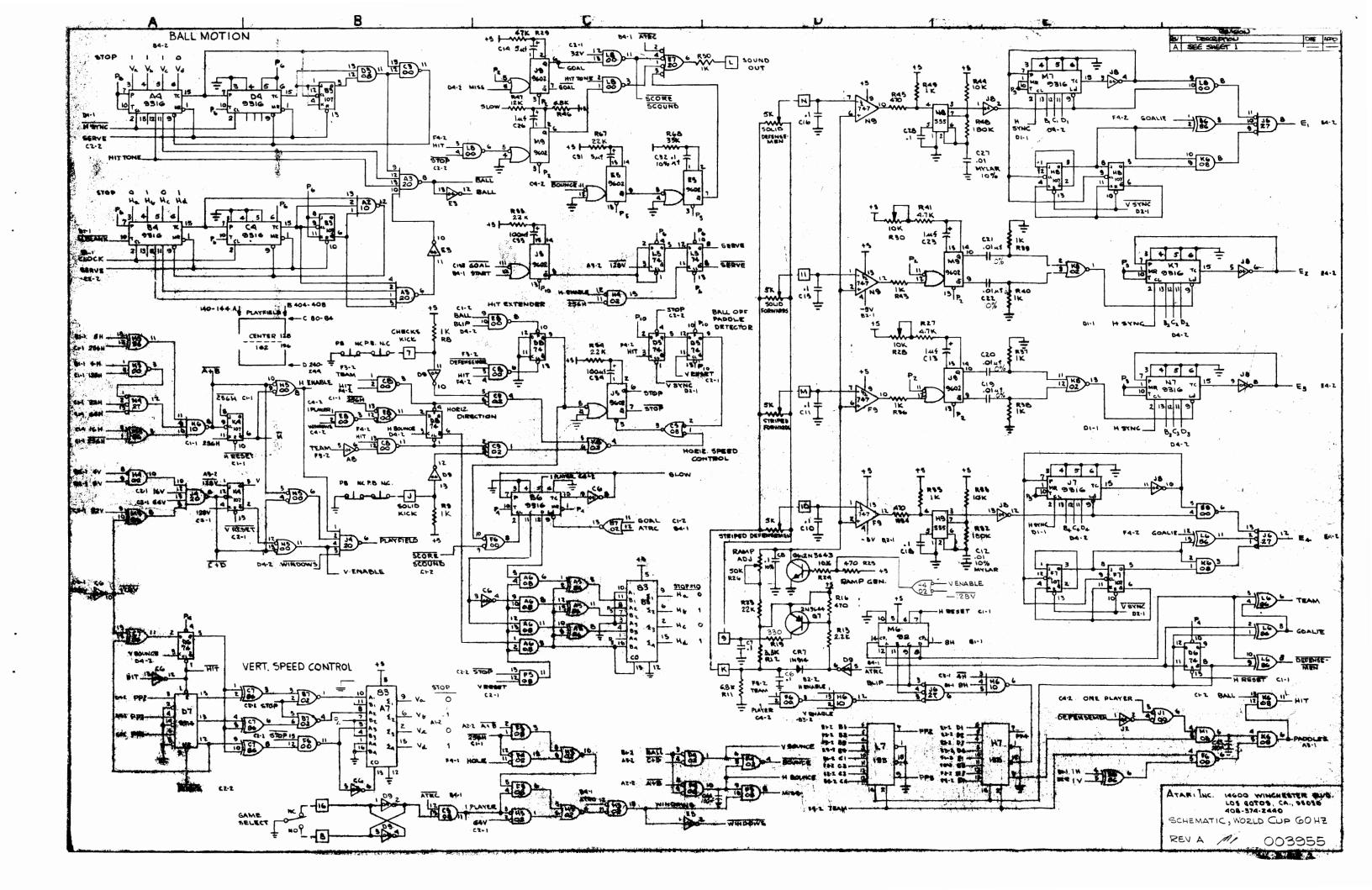

There are a number of adjustments which are made directly on the printed circuit board (PCB) with the machine energized. Adjustments 3-6 are performed with a game started. (refer to Fig. B on page 0.8 M - 18)

- 1. PLAYS PER COIN: The plays-per-coin adjustment is located near the large CAN-TYPE filter capacitor and is marked "1P" and "2P". If the switch is set to "1P" position, the player will receive one play per each coin he inserts; if this switch is set to the "2P" position, the player will receive two games per coin.

- 2. TIME LINE: With the game on but <u>not</u> started, turn the small blue trim pot clockwise all the way (looking at the thumbwheel side of the pot). If the time line dips below the top of the playfield wall, turn the pot <u>counter-clockwise</u> until the time line just comes even with the upper side of the playfield wall.

- 3. TIME RATE: The time rate pot controls the <u>rate</u> at which the time line decreases. Turn the pot clockwise to increase the game length and counter-clockwise to decrease the playing time.

- 4. ALL PADDLES: All the paddle images or "men" can be simultaneously centered within the playfield perimeter by adjusting the trim pot. Adjust this pot so that the goalies cannot be moved outside the innermost edge of the playfield perimeter.

- 5. CHECKED FORWARD: Set all the player-operated potentiometer knobs so

that the upper edge of the upper man controlled by that knob barely touches the bottom of the upper boundary of the playfield perimeter. Then adjust the trim pot so that the lower checked forward is in line with the lower defensive back.

6. SOLID FORWARD: This adjustment is the same as Adjustment #5 except that it changes the position of the solid forward.

#### G. Static Modification

Due to the inclusion of the static modification in the electronic latch circuit, it is no longer possible for the player to obtain free games by inducing a static charge in the coin entrance plate, or any other metal part of the machine (providing that the antenna wire has been cut to optimum length).

The antenna wire is a length of white wire approximately 12 inches long. One end is connected to pin 6 of the 22-pin PCB edge connector and the other end has been intentionally left not connected.

When a static discharge occurs, an electric current is induced in the antenna wire. This impulse is transmitted to the electronic latch circuit which turns off game credit and resets the game to the attract mode. The static modification may be tested by touching the end of the antenna wire with your finger, as the body usually has enough capacitance to trigger the static modification.

The sensitivity of the static modification may be adjusted by changing the length of the antenna wire. Lengthening the wire increases the sensitivity of the circuit so that a lesser charge will turn off game credit. Outling the wire shorter decreases the sensitivity of the system and a larger charge is required to trigger the circuit.

If you have problems with static charges accidentally shutting off the game, try cutting the antenna wire shorter in increments of 1-2 inches at a time. Be aware, however, that if the antenna wire is cut too short, players may be able

to obtain free game credit by inducing a static charge in the machine.

# H. T.V. Monitor Adjustment

All the T.V. monitor adjustment points are accessible through the hinged top. The monitor adjustments function like those of any normal T.V. set. Please see figure #H for the locations of these adjustments.

- 1. VOLUME: Adjust the volume to the preference of the location. Please keep in mind that the machine will sound louder with either door open.

- 2. BRIGHTNESS: This should be adjusted before the contrast. Adjust the birghtness so that the white lines which cover the screen with the brightness turned up, just disappear.

- 3. CONTRAST: Adjust so that the images are as bright as possible against the dark background without being blurred.

- 4. HORIZONTAL HOLD: Adjust if the picture is slightly off-center horizontally, if the images appear warped or if the picture is broken up into a series of diagonal lines. Adjust for a stable, centered picture.

- 5. VERTICAL HOLD: This needs adjustment only if the picture appears to be rolling up or down the screen. Adjust for a stable, centered picture.

- 6. VERTICAL SIZE: This adjustment is as critical as the vertical linearity. Any change in one will affect the other. The recommended size of the display should be  $8\frac{1}{2}$ " by 12" which includes the time line.

- 7. VERTICAL LINEARITY: This adjustment is primarily to insure the paddle length will remain the same as it traverses the screen from top to bottom. The best way to evaluate the linearity is to look at the playfield and determine if the four lines within the playfield (top and bottom) have the same separation.

- 8. THE YOKE: The yoke should never need adjustment unless the adjusters have been tampered with or the machine damaged. If yoke adjustment is indicated, adjust both yoke rings <u>simultaneously</u> for optimum centering of the image on the CRT. This adjustment is best handled by a qualified service person.

- 9. AC VOLTAGE SWITCH: Set this switch to the 115V position ("115" visible on the switch) if the machine is connected to a 115V source or to the 230V position ("230" visible on the switch) if the machine is connected to a 230 volt source. The T.V. monitor will not function if this switch is misadjusted.

NOTE: If the monitor of a 230-volt machine is set to 115 volts, it will blow the machine line-fuse repeatedly.

- 10. THE T.V. MONITOR FUSE: Two 1-amp, 110-volt, fast-blow fuses protect the T.V. from electrical overload. Replace blown fuses ONLY with those having the above rating. These fuses are located on the T.V. chassis at the front left side as you face the raised chassis. (The PCB fuse is located on the electronics tray just inside the coin door. This fuse should be replaced ONLY with a 1-amp, 110-volt, slow-blow fuse.)

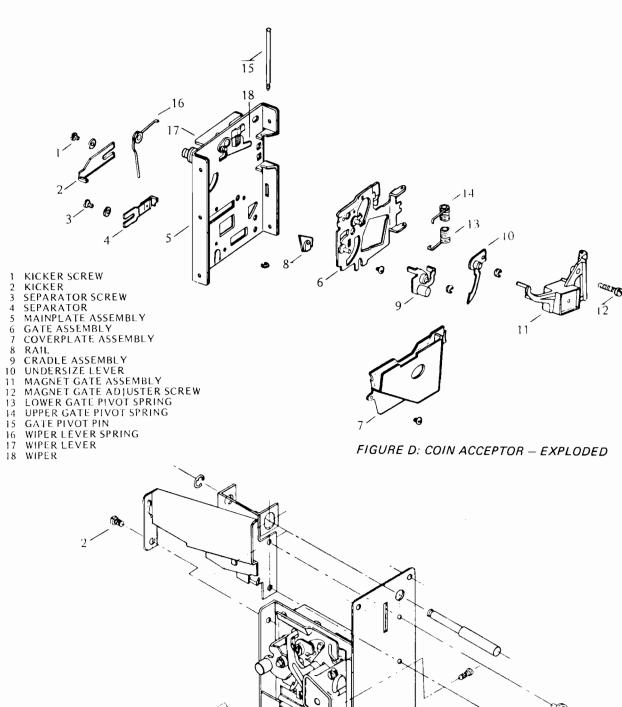

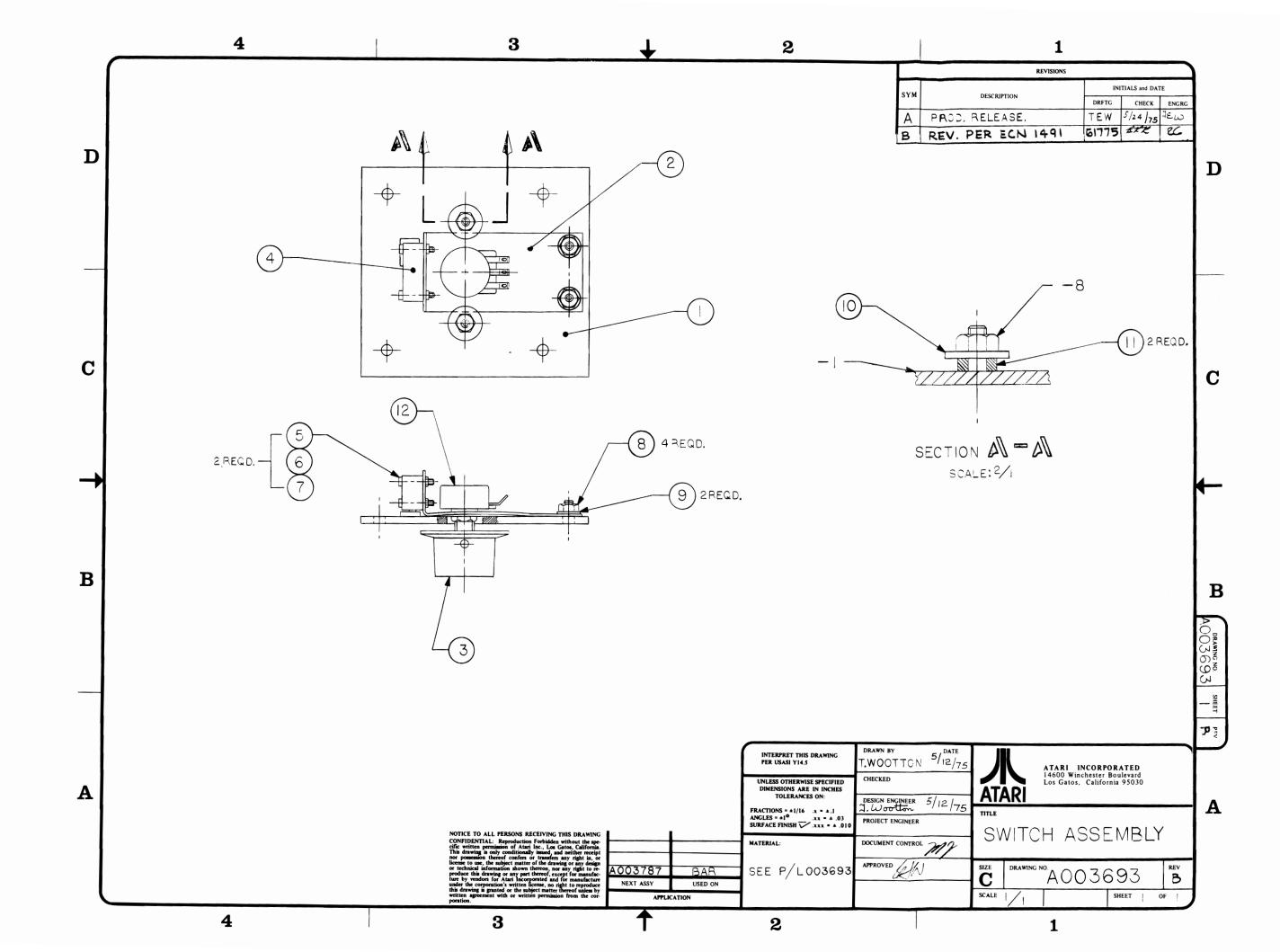

- I. Coin Acceptor: Operation, Adjustment and Maintenance

OPERATION: The detection and rejection of undesired or counterfeit coins are determined by size (both thickness and diameter), weight and metallic composition.

The transfer cradle (9) is used to test both the size and the weight of the coin. The quarter must first pivot an "undersize lever" (10) to unlock the transfer cradle. Undersize "quarters" will fail to unlock the transfer cradle and can be returned by actuating the wiper operating lever. Oversize diameter coins will fail to pass between the transfer cradle and the wiper and can be returned by operating the wiper lever. Coins that are oversize in thickness will fail to pass between the magnet gate and the main channel and will have to be dislodged by

actuating the wiper operating lever. Underweight coins will fail to overcome the transfer cradle counterweight and can be returned by operating the wiper lever.

A magnet is used to test the metallic composition of the coin. Highly magnetic coins, such as steel or iron, will be retained by the magnet and can be returned by actuating the wiper operating lever. Coins having comparatively high magnetic properties will be slowed down by the magnet and will drop off the end of the rail short of the "accept" entrance and will be returned. Coins having little or no magnetic properties, such as brass or zinc, will pass through the magnetic field so fast they will overshoot the "accept" entrance and will be returned.

#### COIN ACCEPTOR

ADJUSTMENT: All coin acceptors leave the factory adjusted for maximum performance. If, however, more critical adjustments are desired, or if the unit has been completely disassembled for service, the following adjustment procedure is suggested.

If the coin acceptor has been removed from the machine, place it in a vertical position on a level surface. If the acceptor is still mounted on the coin door, place the coin door in a vertical position on a level surface.

#### A. KICKER AND SEPARATOR

- 1. Set the acceptor with the back of the unit facing you in the test position.

- 2. Loosen the screws holding the kicker (1) and the separator (3) and move both the kicker (2) and the separator (4) as far to the right as they will go. Tighten the screws.

- 3. Insert several test coins (both old and new) and note that some are returned by striking the separator.

- 4. Loosen the separator screw and move the separator a slight amount to the

- left. Tighten the screw.

- 5. Insert the test coins again and, if some of them are still returned, repeat Step 4 until all the coins are accepted.

- 6. Loosen the kicker screw and move the kicker as far to the left as it will go. Tighten the screw.

- 7. Insert the test coins and note that some are returned.

- 8. Loosen the kicker screw and move the kicker a slight amount to the right. Tighten the screw.

- 9. Insert the coins again and, if some are still returned, repeat Step 8 until all the coins are accepted.

- 10. Be sure that both screws are tight after the adjustments have been made.

- B. THE MAGNET GATE

- 1. Set the acceptor with the front of the unit facing you in the test position.

- 2. Turn the magnet gate adjusting screw (2) out (counter-clockwise) until none of the coins will fit through.

- 3. With a coin resting in the acceptor, turn the adjuster in (clockwise) until the coin barely passes through the magnet gate.

- 4. Test this adjustment using several other coins (both old and new) and, if any of them fail to pass the magnet gate, repeat Step 3 until all the coins are accepted.

- 5. Fix the magnet gate in this position with a drop of glue or lok-tite, if necessary.

C. ACCEPTOR MAINTENANCE: Depending on the environment in which the acceptor is used, periodic preventive maintenance should be performed.

The mainplate (5) may be cleaned with any household cleaner. Thorough rinsing and drying are necessary to remove deposits and/or film.

Remove all metal particles from the magnet by guiding the point of a screwdriver or similar tool along the edges of the magnet. You will notice that the particles will cling to the point of the tool.

Remove the transfer cradle (9) and the undersize lever (10) and clean the brushings and pivot pins. A pipe cleaner is an effective cleaning tool. Apply powdered graphite or pencil lead to the pivot pins and bushings and reassemble.

Spray the entire unit lightly with WD-40, a silicone lubricant.

#### J. General Machine Maintenance

Due to its solid state circuitry, your Goal IV game will require very little maintenance other than periodic cleaning, lubrication and T.V. monitor adjustment.

The cabinet and plexiglass screen may be cleaned with any non-abrasive house-hold cleaner. The coin acceptor and the rejector linkage should be sprayed lightly once every three months with WD-40 or similar silicone lubricant. The potentiometer shafts must <u>never</u> be lubricated in any way. The T.V. monitor is adjusted <u>only</u> when the CRT picture is distorted, or if the contrast or brightness appear to be out of adjustment.

#### K. Troubleshooting

The first step in any troubleshooting procedure is to observe the characteristics of the malfunction. With these clues in mind, examine the areas of the machine

which might <u>cause</u> these symptoms. For example, if there is no power, check the harness, not the PCB. Likewise, if part of the playfield display is missing, check the PCB, not the harness or T.V.

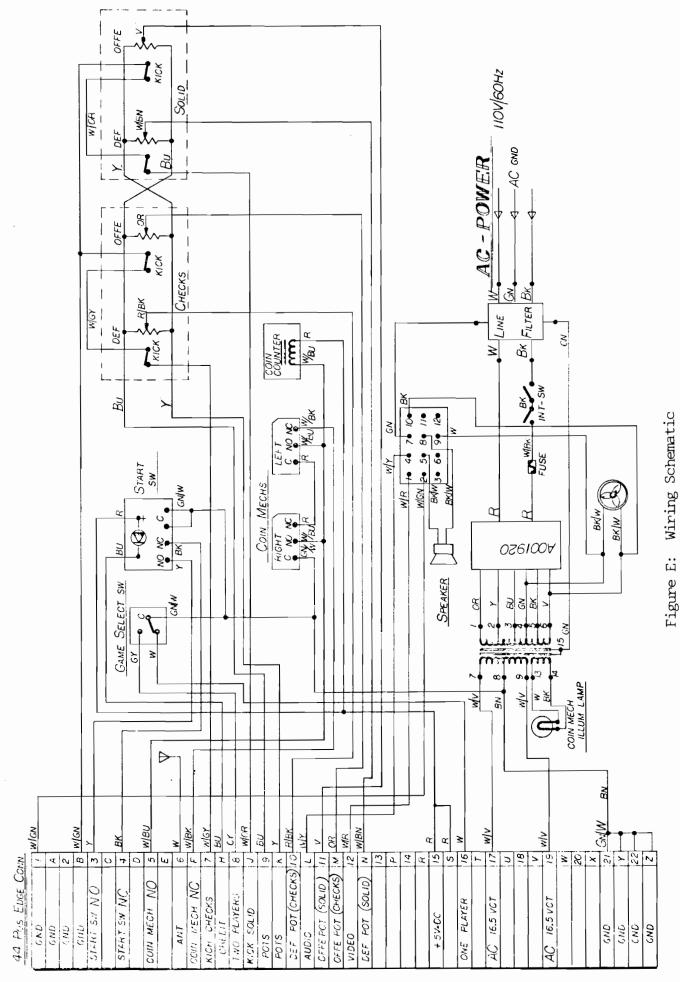

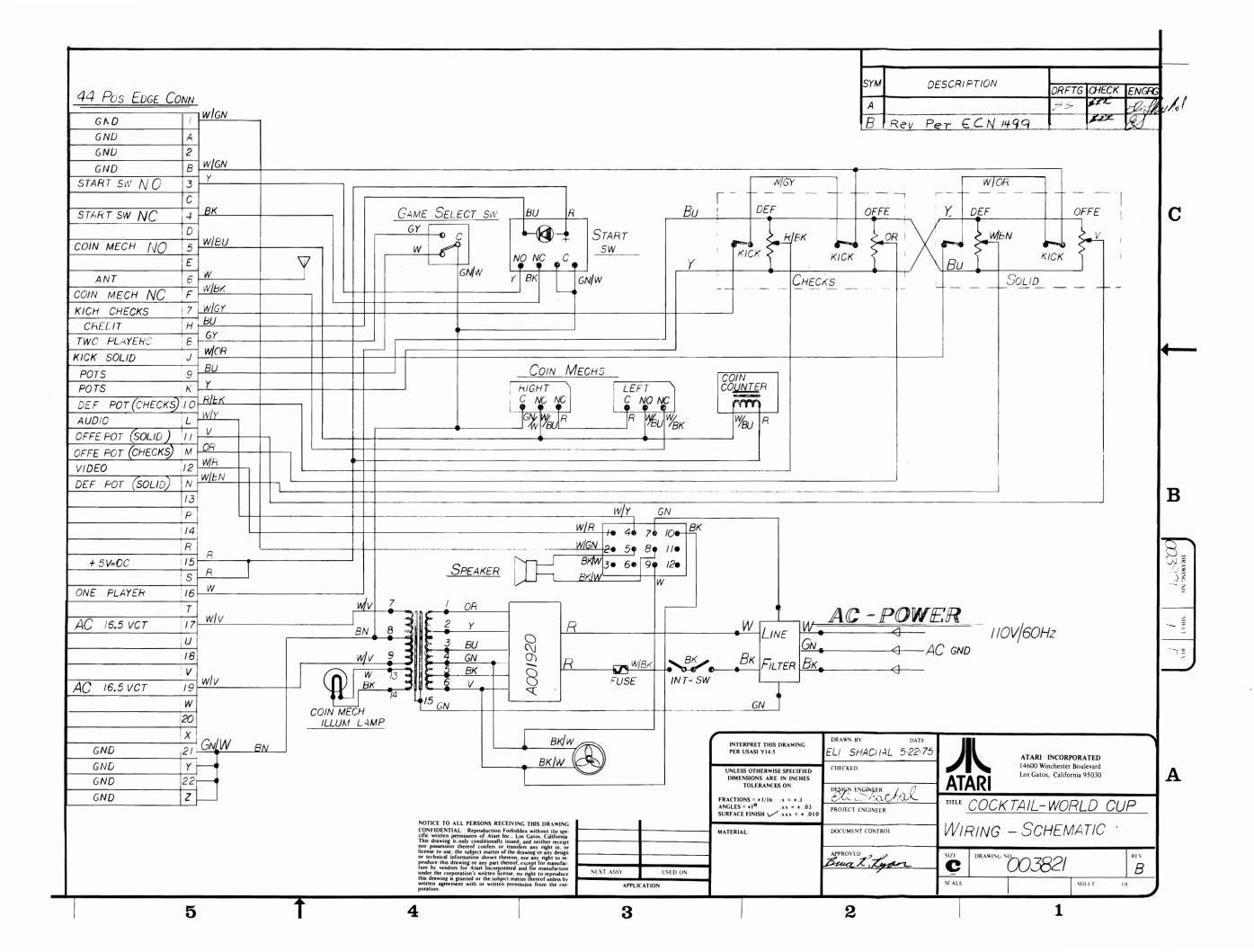

Three major areas of the machine can be isolated for troubleshooting purposes: the T.V., the PCB and the harness. The harness includes the fuses, the transformer, the interlock switches, the A.C. line filter, the start and coin switches, the antenna wire, the potentiometers and kick switches, all plug-in type connectors, the PCB edge connector and all the interconnecting wires.

- 1. SUBSTITUTION: Substitution of parts is a legitimate and easy way to troubleshoot the machine. For instance, if you suspect PCB malfunction, try substituting another and known-to-be-good PCB. To check the T.V. monitor by substitution, connect the malfunctioning game to a known-to-be-good monitor. Harnesses are checked by elimination. Substitute a good T.V. and PCB and, if the malfunction persists, the harness must be at fault.

- 2. OTHER TROUBLESHOOTING TIPS: If you have a T.V. raster only (a T.V. raster is a blank, but lit T.V. screen with the brightness turned all the way up) and you want to determine if the PCB or the T.V. is causing the lack of video display, try the following test: (a) disconnect the PCB edge connector; (b) turn the brightness and contrast all the way up; (c) connect pin 11 of the PCB edge connector to pin 12 with a test lead. If your T.V. monitor is functioning correctly, you will see faint black bars ("hum bars") on the screen.

To check the speaker, turn the volume control all the way up and connect one end of a test lead to pin L (audio) of the <u>dis</u>connected PCB edge connector. Momentarily touch the other end to either pin 17 or pin 19 (transformer secondary AC) of the edge connector and if the speaker is functioning correctly, you will hear a loud buzz (60-cycle hum).

To check if the <u>PCB power supply</u> is functioning correctly, use the following procedure:

- 1. First check for the presence of transformer secondary voltage between pins 21 and 19 with a VOM. Meter should read 8-10 volts AC.

- 2. Then check the PCB power supply output between pin 21 and pin 15 with a VOM. Meter should read 5 volts DC.

- 3. TROUBLESHOOTING BY SYMPTOM:

- 1. <u>No Power</u>: a. Check for correct line voltage and if O.K., then check fuses and interlock switches. If O.K., check transformer primary which should show line voltage. Then check transformer secondary (pins 19 and 21) which should be 10 VAC.

- 2. <u>Game Credit Shuts Off</u>: Try cutting the antenna wire shorter in increments of 1-2 inches.

- 3. <u>Game Credit Shuts Off and/or T.V. Picture Shrinks</u>: Check line voltage with VOM and be aware that a large motor nearby (e.g., air conditioner) may drop line voltage when starting up.

- 4. <u>No Picture; No Raster</u>: Check to see if T.V. connector is plugged in; check for line voltage at T.V. and if T.V. AC voltage switch is set to correct position. Check T.V. fuses and brightness control.

- 5. T.V. Raster Only: Check harness and especially the PCB edge connector. Check PCB. Check T.V.

- 6. Picture Rolls: Adjust T.V. vertical hold. Check or replace PCB.

- 7. <u>Picture is Wavy:</u> Adjust T.V. horizontal hold. Replace transformer. Check harness. Particularly grounds.

- 8. <u>Picture is Broken into Diagonal Lines</u>: Adjust T.V. horizontal hold. Replace PCB.

- 9. Jerky Paddle Motion: Replace appropriate potentiometer.

- 10. No Game Credit: Check coin switch, start switch and harness. Replace PCB.

- 11. No Game Start: Check coin switch, start switch and harness. Replace PCB.

- 12. Game Sequence Incorrect or Parts of Playfield Display Missing, Distorted or Not Functioning: Replace PCB.

- 13. No Audio: Check volume control, speaker connections. Replace PCB.

(Mode #1) "Player" vs. "Game" Configuration

Both views are as seen standing on side opposite coin mechanism.

FIGURE A: PLAYFIELD

O & M - 18

0 & M - 20

Schematic Diagram

Figure F: Motorola XM501 Monitor

The above drawing of the monitor adjustment points is for the most part self-explanatory. However, please note the following:

- 1. Reference point #1 is the A.C. voltage switch. This switch should never be touched.

- 2. Reference points #2 through #7 are the same as on a normal T.V.

- 3. Reference point #8 is the Vertical Linearity knob. It is used to adjust the picture for the same length at both the top and bottom.

- 4. Reference point #9 is the Vertical Height knob. This controls the height of the picture.

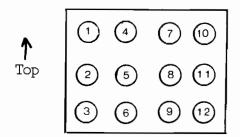

Plug Connector Detail

Pin specifications for connector:

- 1. Video

- 2. Ground

- 3. N.C.

- 4. Sound in

- 5. Spkr. out 1

- 6. +5V out

- 7. AC ground

- 8. Spkr. out 2

- 9. AC in

- 10. AC in (always hot)

- 11. & 12. not used

Figure G: TV Monitor Adjustments

# L. Detailed Circuit Description

#### INTRODUCTION:

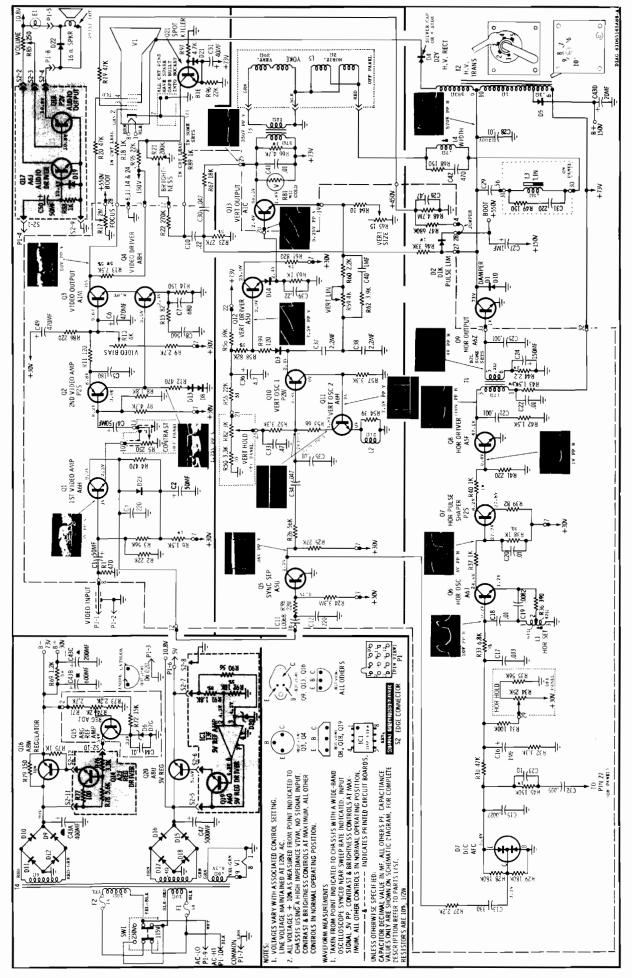

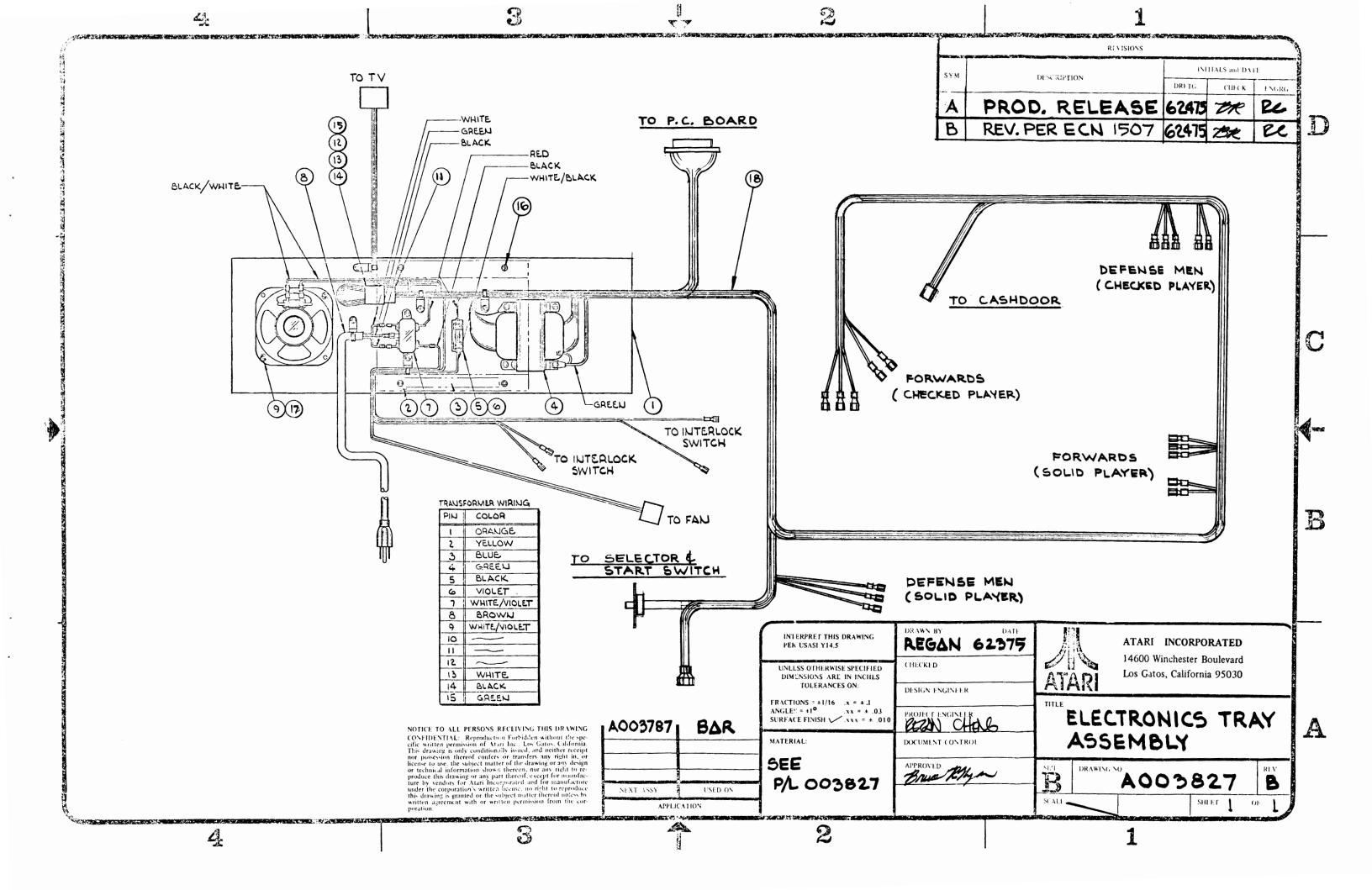

The Atari Goal IV game consists of a cabinet, TV monitor, a computer printed wiring assembly (PWA), interconnecting harness, and various cabinet-mounted circuit components. Except for a schematic, no information about the TV monitor is presented in this manual. The TV monitor is a modified Motorola XM501 unit, and circuit malfunctions can be solved using standard TV troubleshooting techniques. However, the computer PWA requires troubleshooting techniques that may be unfamiliar to the average technician. Therefore, the troubleshooting information in this manual is dedicated to the computer PWA and its associated cabinet circuitry.

#### TEST EQUIPMENT:

In order to test any Atari PCB, some equipment such as the logic probe is absolutely essential. Other equipment is desirable and makes testing easier but is not absolutely essential. Some equipment items are available from the Atari Customer Service Department and these are: The Atari Universal Test Fixture, the Kurz-Kasch 520 Logic Probe, the Atari Video Probe, and the Hewlett-Packard 10529 Logic Comparator. Other equipment items that are very useful are the HP 10526T Logic Pulser and the HP 465 Oscilloscope. These items are available through your local electronics supply house.

REQUIRED MINIMUM EQUIPMENT: The following items are absolutely essential to perform the test procedures presented in this manual.

1. Atari Universal Test Fixture. The Atari Universal Test fixture can be used to test the computer printed wiring assemblies (PWAs) for Goal IV. This test fixture is equipped with a 19-inch TV monitor, two 5-volt BNC connectors for use where a regulated 5-volt source is required, and all the controls necessary to operate the computer PWAs. Connector cables must be ordered separately for each different type of PCB to be tested. The test fixture and cables are

only available through the Atari Customer Service Department.

2. Logic Probe. The logic probe is an instrument designed for checking the outputs of integrated circuits. Atari recomments the Kurz-Kasch Logic Probe, Model No. LP-520, which is available through the Atari Customer Service Department or most large electronics supply houses.

This logic probe indicates if a signal is a logic high, logic low, or changing from one state to another. Consult the operating instructions included with the probe for further details about its operation. Logic probes received from the Atari Customer Service Department are specially modified to be compatible with the 5-volt BNC connector of the Universal Test Fixture.

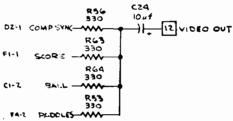

3. Video Probe. The video probe is a very simple but extremely useful device and consists of two test clips, a length of rubber-coasted test-lead wire, and a 4.7K, 1/4-watt carbon resistor. Video Probes may be obtained free from the Atari Customer Service Department; or, if necessary, they can be assembled from standard components available at all electronics supply houses.

To use the video probe, attach one clip to the negative (-) side of the 10-MFD video coupling capacitor found near position C24 on the computer PWA and clip the other end to the desired signal test points as indicated in the test procedures presented in this manual. The video probe allows the desired signal to be displayed on the TV monitor screen.

OPTIONAL EQUIPMENT: It is possible to find 90% of the possible computer PWA malfunctions without the following items. However, if a complete set of troubleshooting equipment is desired, Atari recommends:

1. Hewlett-Packard 10529A Logic Comparator. The Hewlett-Packard 10529A Logic Comparator is used to verify correct IC operation. This device simply clips onto in-circuit ICs and instantly displays any logic state difference between the in-circuit test IC and the reference IC in the comparator. Logic differences are indicated by a lighted light-emitting diode for each pin of a 14

or 16 dual in-line package.

If the logic comparator is purchased from the Atari Customer Service Department, it is shipped with 20 preprogrammed reference PWAs. If the device is purchased elsewhere, these PWAs must be specially programmed.

- 2. Hewlett-Packard 10526T Logic Pulser. The Hewlett-Packard 10526T Logic Pulser is used to stimulate in-circuit ICs so that they are driven to their opposite states. This device is available from the Atari Customer Service Department or can be obtained from most large electronics supply houses.

- 3. Tektronics 465 Oscilloscope. The Tektronics 465 Oscilloscope is used for viewing various waveforms and should be ordered from Tektronics. Consult the manufacturer's operating instructions for details on oscilloscope operation.

#### ADJUSTMENTS:

No adjustment information is provided in this manual. Refer to the Operating and Maintenance Manual of the Goal IV game for recommended adjustment procedures for the computer PWA, TV monitor, and coin mechanism.

#### GENERAL TROUBLESHOOTING APPROACH:

The first step when troubleshooting malfunctions of the computer PWA is to relate the visible or audible malfunction to one or more circuits of the computer PWA. For instance, if one of the player symbols is malfunctioning, study the text of the players circuit and then try to determine what might be causing the problem. Then, using schematics, waveforms (where provided), component location diagram, and recommended test equipment, check out the players circuitry. Partial schematics of the computer are provided with each circuit des description. Overall schematics of the computer PWA and TV monitor, a cabinet wiring schematic, a component location diagram for the computer PWA, and a parts list are located at the back of this manual.

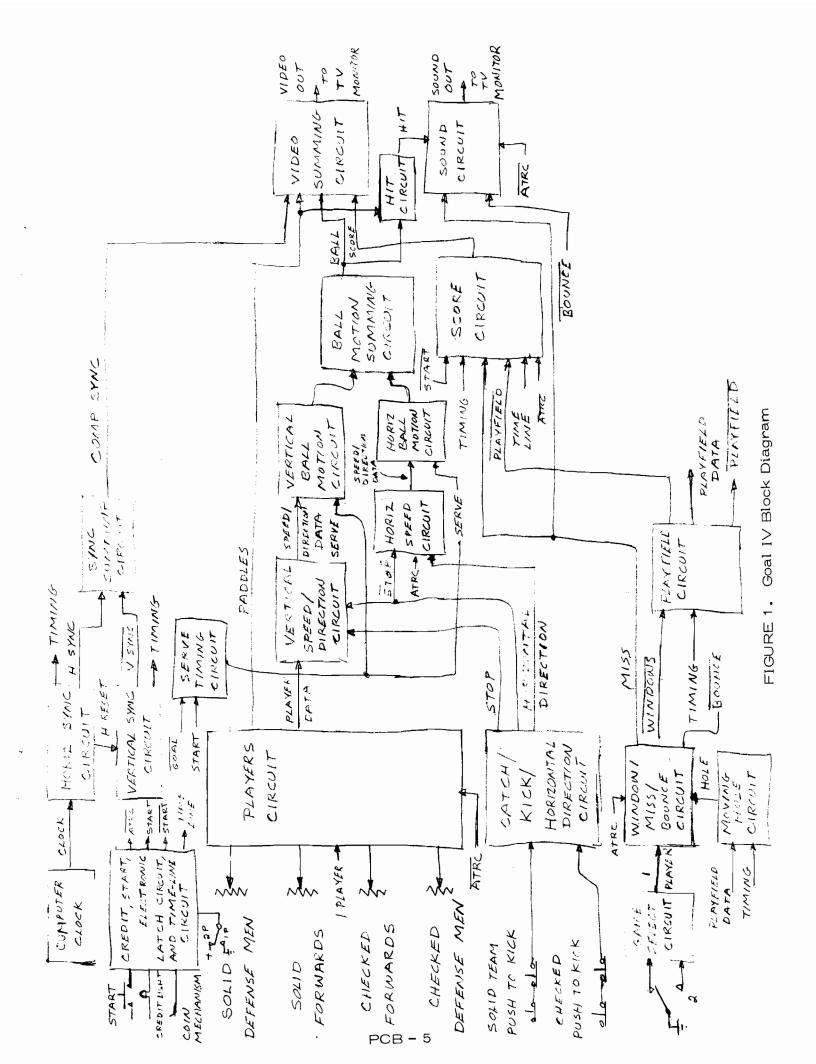

# BLOCK DIAGRAM DESCRIPTION:

All circuitry of the computer PWA is activated when the power cord of the Goal IV game is connected to a suitable source of AC power. Circuitry in the credit/start/electronic latch circuit automatically generates ATRC, START and START signals. These signals are used by various circuits of the computer PWA to place the game in the attract mode.

ATTRACT MODE: In the attract mode, the computer clock furnishes timing signals to various circuits of the computer PWA. The horizontal sync and vertical sync circuits process the CLOCK signal and send timing signals to various circuits of the computer PWA and horizontal sync and vertical sync to the TV monitor via the sync summing and video summing circuits. The player controls, sound circuit, and score circuit are defeated by the  $\overline{\text{ATRC}}$  signal; and the window/miss/bounce AND circuit and a portion of the horizontal-speed circuit are defeated by the ATRC signal. Consequently, the goal windows do not appear in the playfield symbol generated by the playfield circuit, the players cannot be positioned, and no sounds are developed. However, the  $\overline{\text{ATRC}}$  signal enables the score display circuit, allowing the score of the last game to be continuously displayed.

Player data indicating what portion of each player is being developed at any given time is continuously fed to the vertical speed circuit. In turn, the vertical speed circuit sends speed and direction signals to the vertical ball motion circuit, which furnishes the vertical-motion component of the BALL signal to the ball-motion summing circuit. The catch/kick/horizontal direction circuit furnishes horizontal direction information to the horizontal speed circuit, which then sends direction and fixed-speed data to the horizontal ball-motion circuit. The resulting horizontal-motion and vertical-motion components of the BALL signal are summed and send to the video summing circuit. Since no active GOAL or START signals are developed in the attract mode, the serve timing circuit is inactive. As a result, in the attract mode, the ball continually bounces off defensemen and sides of the playfield in a random fashion. If the ball strikes

a goalie or forward, it is momentarily arrested and then kicked into motion.

PLAY MODE: After a proper coin is inserted in the coin mechanism, the credit/start/electronic-latch/time-line circuit lights the credit light and enables the START SWITCH pushbutton. Either a one-player or two-player mode can be selected by setting the front panel 2/1 switch to the desired position.

One-Player Mode. In the one-player mode, the player plays against the Goal IV machine. Game play is initiated by pressing the front-panel START SWITCH pushbutton, which causes the machine to switch from the attract to the one-player play mode.

The ATRC, START and START signals from the credit/start/electronic-latch/ time-line circuit enable all the circuitry that was defeated in the attract mode. This circuit also generates a TIME-LINE signal that causes a vertical time-line bar to appear at the left of the playfield symbol. In addition, the 1 PLAYER signal from the game select circuit conditions the window/miss/bounce circuit for one-player operation. Consequently, this circuit accepts a moving HOLE signal from the moving hole circuit and generates a WINDOWS signal containing fixed and moving-goal data. This WINDOWS signal causes the playfield circuit to generate a PLAYFIELD signal that, in turn, is used to cause a playfield symbol having a fixed goal on the left and a moving goal on the right to appear on the TV screen. The 1 PLAYER signal also causes the players circuit to eliminate the solid defensemen and all of the checked players from the PADDLES signal. Thus, only the solid goalie and forwards symbols appear on the TV screen.

When the START SWITCH pushbutton is pressed, the time-line begins to diminish in vertical height; after a short pause, the ball is served from the center of the playfield towards the left goal. If the ball goes through the left goal, the window/miss/bounce circuit sends a MISS signal to the score circuit. In turn, the score circuit causes the left and right scores to be momentarily displayed on the TV screen. If the player uses the solid DEFENSE MEN control to position the solid goalie such that the ball hits the goalie, the ball is momen-

tarily arrested. The player may then reposition the goalie and press the PRESS TO KICK pushbutton. The ball is then sent off in a direction that depends on what portion of the player symbol last contacted the ball. If the goalie is moved off the ball, the ball is automatically kicked. If the goalie is not moved off the ball nor is the ball kicked within three seconds after the ball is arrested by the goalie, the ball is automatically kicked. The solid forwards operate in a similar fashion but are positioned by the front-panel solid FORWARDS control. If the ball passes through the moving goal, the new score is displayed and another ball is served to the left after about three seconds. The game continues in this fashion until the time bar disappears. At this time, the game is ended, and the game automatically reverts to the attract mode. If the internal 1P/2P switch is set to 2P, a new game may be started by pressing the START pushbutton. Otherwise, if the switch is set to the 1P position, another coin must be deposited to establish game credit.

Two-Player Mode: The two-player mode is similar to the one-player mode except that the playfield symbol contains two fixed goals; solid and checked goalies, defensemen, and forwards appear on the TV screen; and the direction the ball is served varies in accordance with the score. In this mode, the solid players oppose the checked players. One further variation is that the defensemen can only be used to bounce the ball. Only the goalies and forwards can catch and kick in the manner previously described.

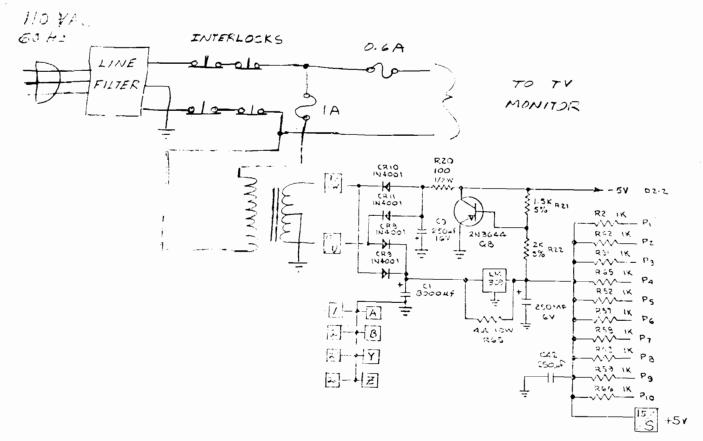

## POWER SUPPLY:

The power-supply circuitry for the Goal IV computer PWA is shown in Figure 2. Input single-phase, 60-Hz, 110 VAC power is routed through an AC line filter, interlocks, and a 1A fuse to the primary of transformer T1. Half the output of the secondary winding is applied across a positive power supply and its load, and the other half is applied across a negative power supply and its load.

POSITIVE POWER SUPPLY: The positive power supply consists of diodes

CR8 and CR9; capacitors C1 and C40; series voltage regulator LM309; and resistors R2, R42, R51, R65, R52, R57, R58, R62, R59 and R66. Diodes CR8 and CR9 provide full-wave rectification of the AC input, and capacitor C1 filters the resulting pulsating DC output of the diodes. Series voltage regulator LM309 provides a highly regulated +5 VDC output to various circuits of the computer PWA, and resistors R65 and R70 increase the current capacity of the power supply. Capacitor C40 provides filtering for the +5 VDC bus. Resistors R2, R42, R51, R65, R52, R57, R58, R62, R59 and R66 are pull-up resistors for various logic circuits of the computer PWA.

NEGATIVE POWER SUPPLY: The negative power supply consists of diodes CR10 and CR11; capacitor C9; transistor Q8; and resistors R20 and R22. Diodes CR10 and CR11 full-wave rective the AC input, and capacitor C9 filters the resulting pulsating DC output of the diodes. Transistor Q8 and resistors R20 and R22 form a -5 VDC shunt regulator that uses the regulated +5 VDC of the positive power supply as its voltage reference. Thus, if the -5 VDC output tends to become more negative, transistor Q8 conducts more to force the output voltage back to the -5 VDC level. Conversely, if the -5 VDC output tends to become more positive, Q8 conducts less and, consequently, restores the output voltage to -5 VDC.

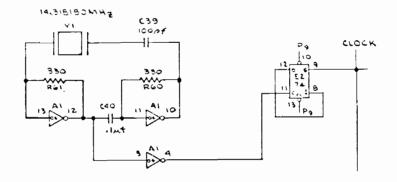

# COMPUTER CLOCK:

Figure 3 shows the circuitry of the computer clock. Inverting amplifiers A1-12 and A1-10, resistors R60 and R61, capacitors C39 and C40, and crystal Y1 form the oscillator portion of the clock circuit. Crystal Y1 is situated in the feedback circuit of the oscillator and functions as a 14.318180-MHz narrow-band filter. Thus, the oscillator is forced to oscillate at a frequency of 14.318180-MHz. The signal taken from the output of amplifier A1-12 is routed through inverter A1-4 to the input of flip-flop E2-9/8. This flip-flop divides the input signal by 2 and delivers a 7.159090-MHz CLOCK signal to various logic circuits of the computer PWA.

FIGURE 2. Power Supply

FIGURE 3. Computer Clock Circuit

PCB - 9

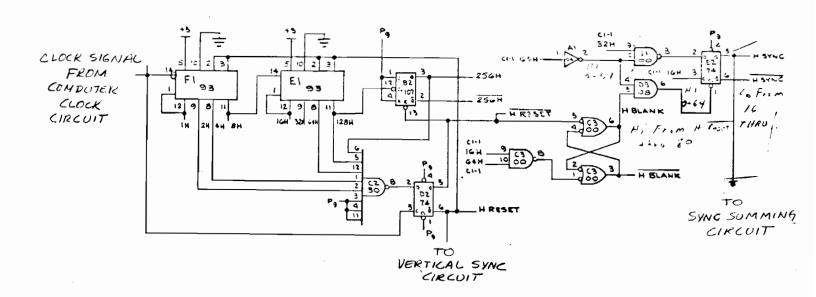

### HORIZONTAL SYNC CIRCUITRY:

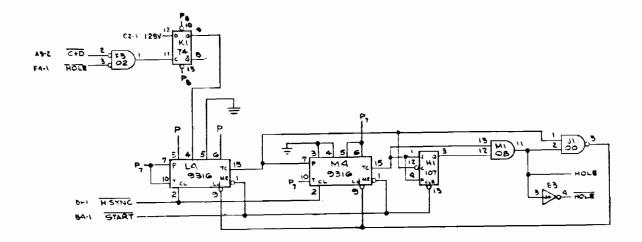

Horizontal sync for the TV monitor and timing signals for various circuits of the computer PWA are supplied by the circuitry shown in Figure 4. This circuit is composed of a counter circuit (F1, E1, B2); NAND gates C2-8, C3-8, and J1-8; AND gate D3-6; inverter A1-2; and flip-flops C3-6/3 and E2-5/6. The counter receives the CLOCK signal from the computer clock circuit and produces numerous submultiples of the CLOCK signal that are designated 1H, 2H, 4H, 8H, 16H, 32H, 64H, 128H, 256H and 256H. These submultiples are distributed to various logic circuits of the computer PWA for timing and signal development purposes. The development of the H SYNC, H SYNC, H BLANK, H BLANK, H RESEIT, and H RESET signals is discussed in the following paragraphs. Development and timing of other signals related to the submultiples of the CLOCK signal are discussed in other portions of this manual.

FIGURE 4. Horizontal Sync Circuit

Each TV line of the Goal IV game is approximately 63.6- sec long, which is equivalent to the time it takes the counter to count 455 CLOCK pulses after being reset. At the count of 455, the 256H, 128H, 64H, 4H and 2H signals are all high. As a result, the output of NAND gate C2-8 goes low. When the CLOCK pulse occurs, the Q output of flip-flop D2-5/6 goes low, and the  $\overline{Q}$  output goes high. The Q output is used to reset flip-flop B2-3/2 of the counter, to set flip-flop C3-6/3, and for other signal development purposes on the computer PWA. The  $\overline{Q}$  output (H RESET) of D2-5/6 is used to reset counters F1 and E1 and is sent to the vertical-sync circuitry and various other circuits of the computer PWA.

Setting flip-flop C3-6/3 causes the output at pin C3-3 to go low, which establishes the leading edge of the H BLANK pulse, and the output at pin C3-6 to go high, which establishes the leading edge of the H BLANK pulse. The H BLANK pulse is applied to AND gate D3-6. Before the count of 64H is reached, the output of inverter A1 is high. Therefore, the output of AND gate D3-6 is high. Signals 16H and 32H are both high at the count of 48. Consequently, the output of NAND gate J1-3 goes low, and the clock input (pin 3) of flip-flop E2-5/6 is enabled. With a low applied to pin E2-2 and highes applied to pins E2-4, E2-3 and E2-1 of flip-flop E2-5/6, the Q output of the flip-flop goes low, which forms the leading edge of the H SYNC pulse, and the Q output goes high, which forms the leading edge of the H SYNC pulse. At the count of 64, the 64H signal goes high, causing flip-flop E2-5/6 to change states and form the trailing edges of the H SYNC and H SYNC pulses. At the count of 80, the 16H and 64H signals are high, causing a low to be applied to the reset input (pin 1) of flip-flop C3-6/3. As a result, the flip-flop changes states and thereby forms the trailing edges of the H BLANK and H BLANK signals. The H SYNC signal is sent to the TV monitor via the sync summing and video summing circuits and is also sent to various circuits of the computer PWA. The HSYNC and HBLANK signals are also sent to various circuits of the computer PWA.

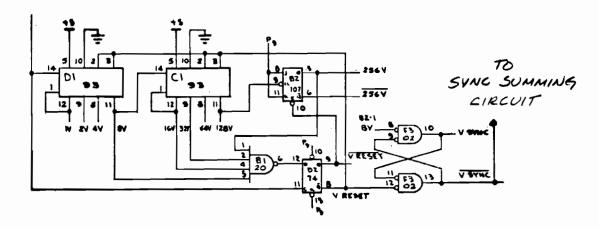

# VERTICAL SYNC CIRCUIT:

Vertical sync for the TV monitor and signal-development and timing signals

for various circuits of the computer PWA are supplied by the vertical sync circuitry, which is shown in Figure 5. The vertical sync circuit is composed of a counter circuit (D1, C1, B2-5/6), NAND gate B1-6, and flip-flops D2-9/8 and F3-10/13. During operation, the counter receives the H RESET signal from the horizontal sync circuit and produces numerous submultiples of the H RESET signal that are designated 1V, 1V, 4V, 8V, 16V, 21V, 64V, 128V, 256V and  $\overline{256V}$ . These submultiples are distributed to various logic circuits of the computer PWA for timing and signal development purposes. The development of the V RESET,  $\overline{V}$  RESET,  $\overline{V}$  SYNC, and  $\overline{V}$  SYNC signals is discussed in the following paragraphs. Development and timing of other signals related to the submultiples of the H RESET signal are discussed in other portions of this manual.

It requires approximately 1/60 of a second to develop one field of the TV picture for the Goal IV game, which is the time it takes the counter to count 262 H RESET pulses after being reset. At the count of 312, the 256V, 4V and 1V signals are all high. As a result, the output of NAND gate B1-6 goes low. When the next H RESET pulse occurs, the Q output  $\overline{(V RESET)}$  of flip-flop D2-9/8 goes low; and the  $\overline{Q}$  output  $\overline{(V RESET)}$  goes high. The Q output is used to reset flip-flop B2-5/6 of the counter and for other timing and signal development purposes on the computer PWA. The  $\overline{Q}$  output is used to reset counters D1 and C1 and to set flip-flop F3-10/13.

Setting flip-flop H1-3/11 causes the output at pin F3-13 to go low, which forms the leading edge of the VSYNC pulse. When the 8V signal goes low, flip-flop H1-3/11 is reset. Resetting flip-flop H1-3/11 forms the training edge of the VSYNC pulse. This pulse is then sent to the sync summing circuit and to other circuits of the computer PWA for signal timing and development purposes.

H RESET SIGNAL FROM HORIZONTAL SYNC

FIGURE 5. Vertical Sync Circuit

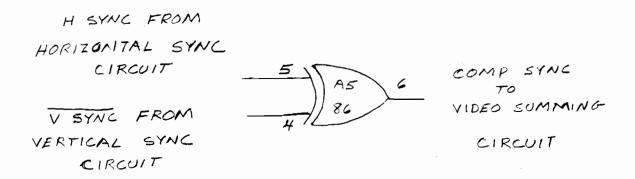

#### SYNC SUMMING:

Exclusive OR gate A5-6 (shown in Figure 6) is used to combine the horizontal sync and vertical sync signals. H SYNC pulses are applied to pin 5 of this gate, and  $\overline{\vee}$  SYNC pulses are applied to pin 4. The logic of the exclusive OR gate causes the  $\overline{\vee}$  SYNC pulse to be serrated by the H SYNC pulses. Serrating the  $\overline{\vee}$  SYNC pulse keeps the horizontal oscillator of the TV monitor synchronized during vertical retrace. The output of the exclusive OR gate is sent to the video summing circuit and consists of a serrated vertical sync pulse (containing 7 serrations) followed by 255 horizontal sync pulses. Therefore, one field of the TV picture consists of 255 viewable lines. Since no interlace provisions are incorporated into the circuitry of the computer PWA, successive fields are laid approximately on top of one another, resulting in a picture frame that contains approximately 255 lines. This frame is repeated 25 times per second.

FIGURE 6. Sync Summing Circuit

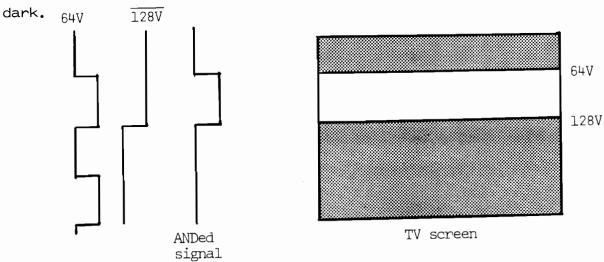

## WINDOWS:

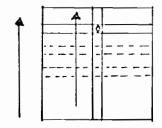

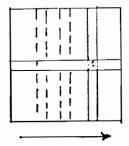

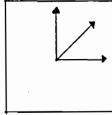

The term window is one that has been coined to explain the process of gating the TV lines so that they can only appear within certain limits. The most confusing thing about the window concept is that it takes information from the vertical sync circuit to produce a horizontal window and vice versa. For example, Figure 7 correlates the vertical signals required to produce a horizontal window between vertical positions 64V and 128V with the window produced on the TV screen. Thus, if the 64V and 128V signals from the vertical sync circuits are ANDed, a signal develops that can be used to blank the electron beam of the picture for all TV lines except those occurring between vertical positions 64V and 128V. As a result, a bright band between positions 64V and 128V appears on the screen of the picture tube. The rest of the screen remains

FIGURE 7. Development of a Typical Horizontal Window

#### ELECTRONIC LATCH CIRCUIT:

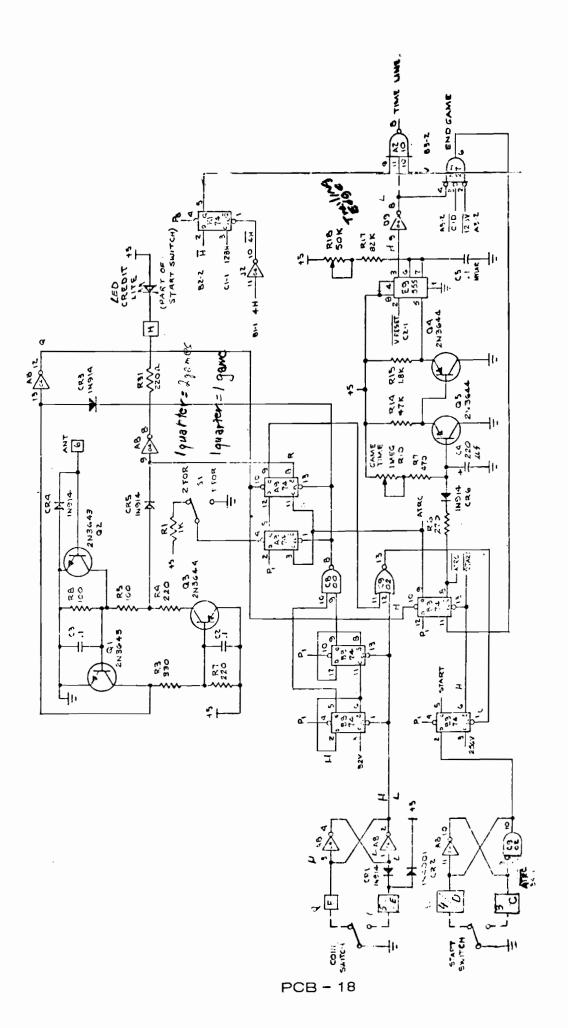

The electronic latch circuit is shown in Figure 8 and consists of transistors Q1, Q2 and Q3 and associated circuitry; inverter A8-12 and an antenna. The antenna is mounted within the cabinet; all other components of the electronic latch circuit are mounted on the computer PWA. The latch circuit has four functions, which are described in the following paragraphs.

The first function of the latch circuit is to initialize (Q high) flip-flop A9-9/8 of the one/two-play circuit and flip-flop B9-9/8 of the start circuit when power is first turned on. This function results from the fact that the latch circuit stabilizes with the collector of transistor Q1 at a higher state after power is turned on. This high is inverted by inverter A8-12 and used to present the Q outputs of flip-flops A9-9/8 and B9-9/8 to a high level. Presetting these two flip-flops disables the start circuit and places the game in the attract mode, which is discussed in another section of this manual.

The second function of the latch circuit is to furnish enabling levels to the preset inputs of flip-flops A9-9/8 and B9-9/8 when the credit circuit has determined that a proper coin has been deposited. As described in the text of the credit circuitry, NAND gate C8-8 develops a negative-going pulse after a proper coin is deposited. This pulse is routed through diode CR3 and resistor R3 to the base of transistor Q3, turning on the transistor. Providing transistor Q2 is not turned on by the antenna circuit (discussed in the next paragraph), the high developed at the collector of Q3 turns on transistor Q1. Turning on Q1 latches transistors Q1 and Q3 in the on state, which perpetuates the high levels applied to the preset inputs of flip-flops A9-9/8 and B9-9/8.

The credit and start circuitry is sensitive to any accidental or player-produced static charges. If not offset, these charges can enable the start circuitry. To offset static charges, a static suppression circuit is incorporated into the circuitry of the game. The circuit consists of an antenna within the cabinet and diode CR4 and diode Q2 on the computer PWA. When static charges are sensed

by the antenna, a positive level is impressed at the base of transistor Q2, turning on Q2. Turning on Q2 means turning off transistor Q1, which causes the start circuit to be inhibited and the attract mode to be enabled as previously described.

The fourth function of the electronic latch circuit is to furnish a low present level to flip-flops A9-9/8 and B9-9/8 at the end of one or two games, as determined by the two-play/one-play circuit. When the two-play/one-play circuit senses that game credit has expired, the  $\overline{Q}$  output of flip-flop A9-9/8 is forced low. This low is routed through diode CR5 to the base of transistor Q1, turning it off. Turning off Q1 unlatches the electronic latch circuit, causing a low to be furnished to flip-flops A9-9/8 and B9-9/8 via inverter A8-12. This low is used to place the game in the attract mode and inhibit the start circuitry.

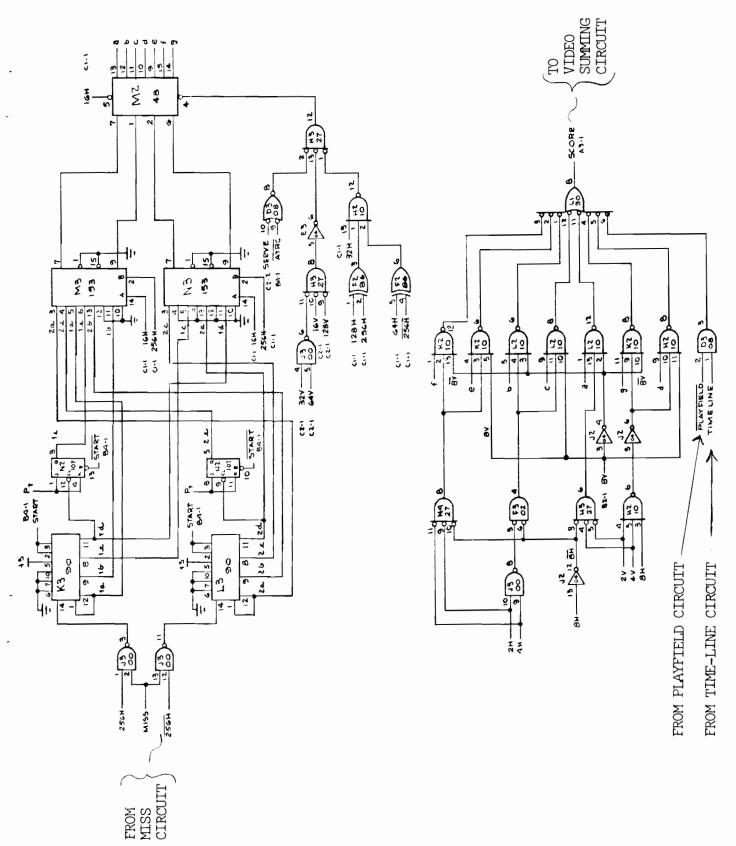

#### CREDIT CIRCUIT:

The credit circuit is shown in Figure 8. This circuit consists of the coin deposit mechanism; diodes CR1 and CR2, resistors R1 and R31; inverter A8-8; flip-flops A8-4/2, B8-5/6, B8-9/8, A9-5, and A9-9/8; NAND gate C8-8; NOR gate C9-13; a light-emitting diode (LED); and the 1P/2P switch. Except for the LED and coin mechanism, all of the foregoing components are located on the computer PWA. The LED is part of the start switch and lights when game credit is established. Both the start switch and the coin mechanism are located on the front panel of the cabinet.

During the time a proper coin is being deposited, a microswitch in the coin deposit mechanism is activated. Actuating the microswitch produces a negative-going pulse that is routed through diode CR1 to pin 1 of flip-flop A8-4/2, setting the flip-flop. This flip-flop is used to prevent transients produced by bouncing contacts of the microswitch from disturbing the circuits of the PWA. The high produced at pin 2 of this flip-flop enables flip-flops B8-5/6 and B8-9/8 and inhibits NOR gate C9-13. Flip-flop B8-5/6 and B8-9/8 for a counter circuit that performs a time-delay function. When enabled, the counter begins counting

32V pulses. If the coin is too small or if a vibration closes the microswitch of the coin mechanism, the microswitch returns to its normally closed position before the count of three, which resets flip-flop A8-4/2. Resetting this flip-flop clears the counter and, consequently, keeps NAND gate C8-8 inhibited.

If a proper coin is inserted in the coin mechanism, NAND gate C8-8 is enabled on the count of three (approximately 10 ms time delay). Enabling NAND gate C8-8 drives its output low, which clears flip-flops A9-5 and A9-9/8 (part of 1P/2P circuit) and triggers the electronic latch circuit. Upon being triggered, the electronic latch circuit releases the preset on flip-flop B9-9/8 of the start circuit. Clearing flip-flop A9-9/8 causes an enabling low level to be applied to pin 11 of NOR gate C9-13, and a high level to inverter A8-8. The low output of this inverter is used to forward bias the LED of the credit indicator, which informs the game player that his coin has been accepted and he may start the game when ready. When the coin moves past the microswitch, the switch returns to its normally closed position, which resets flip-flop A8-4/2, clears flip-flops B8-5/6 and B8-9/8 and enables NOR gate C9-13. Enabling gate C9-13 forces is output high, which releases the low clear level applied to flip-flop B9-5/6 of the start circuit.

The 1P/2P circuit is part of the credit circuit and consists of flip-flops A9-5 and A9-9/8, 1P/2P switch S1, and resistor R1. This circuit allows the game to be set up to provide one game (1P) or two games (2P) for each coin accepted by the credit circuitry.

For example, if the 1P/2P switch is set to 1P, a high is produced at the Q output of flip-flop A9-5. Therefore, when the game is over and the ATRC signal from flip-flop A9-5 is clocked to the Q output of flip-flop A9-9/8. This high output forces the output of NOR gate C9-13 to go low, which inhibits the start circuitry. In addition, the low  $\overline{Q}$  output unlatches the electronic latch, which inhibits the credit and start circuits, and turns off the credit light.

If the 1P/2P switch is set to 2P, a low is produced at the Q output of flip-flop

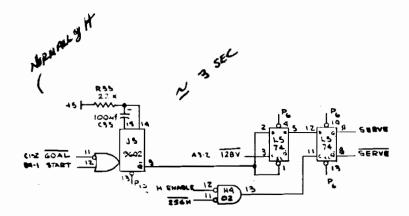

Electronic Latch, Credit, Start, and Time-Line Circuit FIGURE 9.

A9-5 when the negative-going pulse from NAND gate C8-8 occurs when a coin is accepted. Consequently, when the game is over, the fixed high at the D input of flip-flop A9-5 is clocked to the Q output of this flip-flop, but no change occurs at the Q output of flip-flop A9-9/8. Therefore, the electronic latch circuit is not unlatched, the credit light stays on, and NOR gate C9-13 remains enabled. When ready, the game player may press the start pushbutton to begin the second game. At the end of the second game, the high output of flip-flop A9-5 is clocked to the Q output of flip-flop A9-9/8 by the high ATRC signal. This high Q output, in combination with the low  $\overline{Q}$  output, inhibits the start circuit as previously described.

#### START CIRCUIT:

The start circuit is shown in Figure 8 and consists of flip-flops A8-10/C9-10, B9-5/6 and B9-9/8 and the start pushbutton. The start pushbutton is located on the front panel of the cabinet; all other components of the start circuit are located on the computer PWA.

When the credit light is lit, the game is started by pressing the start pushbutton. Providing the attract move is active (ATRC low), pressing and releasing the pushbutton sets and resets flip-flop A8-10/C9-10, causing a positive-going pulse to be applied to the D input of flip-flop B9-5. Flip-flop A8-10/C9-10 is used to prevent transients that are produced by the contacts of the start pushbutton from disturbing the circuits of the computer PWA. If game credit has been established, flip-flop B9-5/6 is enabled by a high clear level from the credit circuit. Consequently, prior to vertical sync, the 256V signal clocks the high output of flip-flop A8-10/A9-10 through to the Q output of flip-flop B9-5/6. This high output (START signal) is applied to various circuits of the computer PWA to help start the game. The low START signal is used to clear flip-flop B9-9/8 and is also used by other circuits of the computer PWA to help start the game. Clearing flip-flop B9-9/8 causes the ATRC signal to go low and the ATRC signal to go high. These signals are routed to various circuits of the computer to help initiate the play mode. When the next 256V clock pulse occurs, the Q output

of flip-flop B9-5/6 goes low; and the  $\overline{\mathbb{Q}}$  output goes high. These states of flip-flop B9-5/6 persist for the remainder of the game.

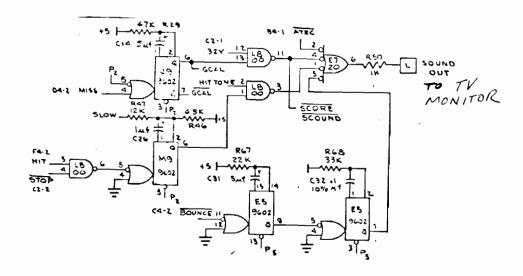

## TIME LINE CIRCUIT:

The time line circuit (shown in Figure 8) consists of resistors R6, R7, R14, R15 and R17; potentiometers R10 and R18; capacitors C4 and C5; transistors Q4 and Q5; timer E9-3; inverters D9-8 and J2-10; NAND gate A2-8; negative-true AND gate A4-6; and flip-flop K1-5. All of these components are located on the computer PWA.

When the  $\overline{\text{ATRC}}$  signal goes high, diode is back biased; and capacitor C4 begins to charge from near ground through R7 and R10 and through the base/emitter junction of Q5 and R14 to +5 VDC. The voltage across C4 is coupled through cascaded emitter-followers Q5 and Q4 to the control voltage input (pin 5) of timer E9. At the beginning of each vertical sync pulse, the  $\overline{\text{VRESET}}$  signal goes low, causing the output at pin E9-3 to go high and capacitor C5 to begin charging through R17 and R18 to +5 VDC. When the voltage at pin E9-6 equals the voltage at pin E9-5, the output at pin E9-3 goes low. As time proceeds, the voltage at pin E9-5 becomes more positive. Consequently, it takes longer and longer for the voltage at pin E9-7 to equal the voltage at pin E9-5. As a result, the duration of the positive pulse developed at pin E9-3 increases with each new TV field. This pulse is inverted (D9-8) and applied to NAND gate A2-8 and negative-true AND gate N4-6.

NAND gate A2-8, flip-flop K1-5, and J2-10 form a window circuit for the TIME LINE signal. Flip-flop K1-5 and inverter J2-10 combine the H, 128H, and 4H signals to form a vertical-window pulse that begins at 128H and ends at 132H. This pulse is applied to pin 9 of NAND gate A2-8. A V pulse taken from the playfield circuit is applied to pin 10 of NAND gate A2-8. The V pulse is high between 80V and 240V and is used to establish the horizontal window timing. NAND gate A2-8 combines the window signals and the time line information (output of inverter D9-8 to form the TIME LINE signal). This signal is routed to the TV monitor via the score and video-summing circuits to cause a vertical

line to appear at the left of the playfield in the TV picture.

Immediately after the game is started, the width of the negative-going pulse at pin A2-11 is narrow relative to its width at the end of the game. Thus, the low TIME LINE signal is allowed to begin soon after vertical position 80V. The point that the TIME LINE signal goes low can be adjusted by potentiometers R10 and R18, which are used to establish the time length of the game. As the width of the negative-going pulse increases in subsequent fields, the appearances of the negative-going TIME LINE signal is progressively delayed in respect to vertical sync. Consequently, the vertical time-line symbol becomes shorter as game time proceeds to indicate the relative time remaining in the game to the player(s).

When the negative-going time-line-delay pulse developed at the output of inverter D9-8 increases in width to the point where it coincides with the low portion of the  $\overline{C}$  &  $\overline{D}$  and  $\overline{128V}$  signals, a high END OF GAME pulse is developed at the output of negative-true AND gate N4-6. This pulse clocks flip-flop B9-9/8, causing a high ATRC signal to appear at the  $\overline{Q}$  output. As previously described, these signals place the game in the attract mode.

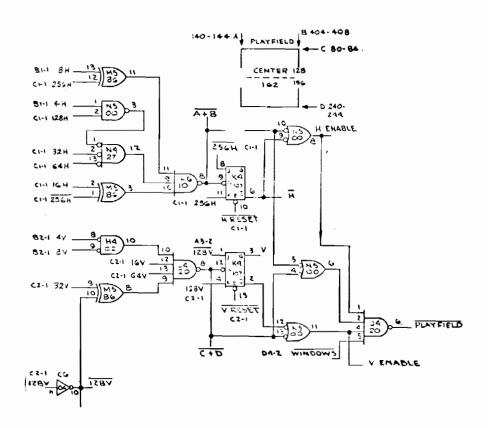

#### PLAYFIELD CIRCUIT:

The playfield circuit (Figure 9) is composed of exclusive OR gates M5-11, M5-3, and M5-8; NAND gates N5-3, H6-8, J4-8, and J4-6; negative-true AND gates N4-12 and H4-10; negative-true OR gates N5-8, N5-6, and N5-11; flip-flops K4-6 and K4-3/2; and inverter C6-10. This circuitry logically combines 8H, 256H, 4H, 128H, 32H, 64H, 16H, 256H, 256H, 4V, 8V, 32V, 128V, 128V, 16V, 64V, and WINDOWS signals to form a PLAYFIELD signal. The PLAYFIELD signal is routed via the score and video summing circuits to the TV monitor where it is used to form the playfield lines.

The 8H, 256H, 4H, 128H, 32H, 64H, 16H,  $\overline{256H}$  signals are logically combined to form the  $\overline{A+B}$  signal, which defines the 4H width of the vertical lines. The

4V, 8V, 16V, 64V, 32V, and 128V are logically combined to form the C+D signal, which defines the 4V width of the horizontal lines. Flip-flop K4-6 combines 256H, 256H, and A+B signals to form a H signal, which is logically combined with the A+B signal to form an H ENABLE signal that defines the vertical window of the playfield. In a similar fashion, flip-flop K4-3/2 logically combines 128V, 128V and C+D signals to form a V signal, which is logically combined with the C+D signal to form a V ENABLE signal that defines the horizontal window of the playfield. Finally, the composite PLAYFIELD signal is formed by logically combining the A+B, C+D, H ENABLE, V ENABLE, and WINDOWS signals in gates N5-6 and J4-6. The WINDOWS signal, which is developed by the window/miss/bounce circuit, causes the goal openings to appear in the vertical playfield lines.

FIGURE 9. Playfield Circuit

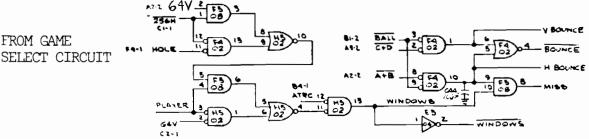

#### GAME SELECT CIRCUIT:

Figure 10 shows the game-select circuit, which consists of flip-flop D9-2/4, AND gate C5-1, and a game-select switch. Except for the front panel game-select switch, all components of the game-select circuit are mounted on the computer PWA. The game select circuit is used to generate 1 PLAYER signal that conditions the logic of the computer PWA to operate in either a one-player or two-player mode of operation.

Setting the game-select switch to 1 (normally closed position) sets flip-flops D9-2/4. Conversely, setting this switch to 2 resets the flip-flop. The output of flip-flop D9-2/4 is applied to AND gate C5-11, which is enabled by a high ATRC signal in the play mode and disabled by a low ATRC signal in the attract mode. When enabled, this gate passes a high or low 1 PLAYER signal depending on whether the game-select switch is set to 1 (player) or 2 (players), respectively. This signal is used to condition various circuits of the computer PWA for the one-player or two-player mode of operation.

FIGURE 10. Game Select Circuit

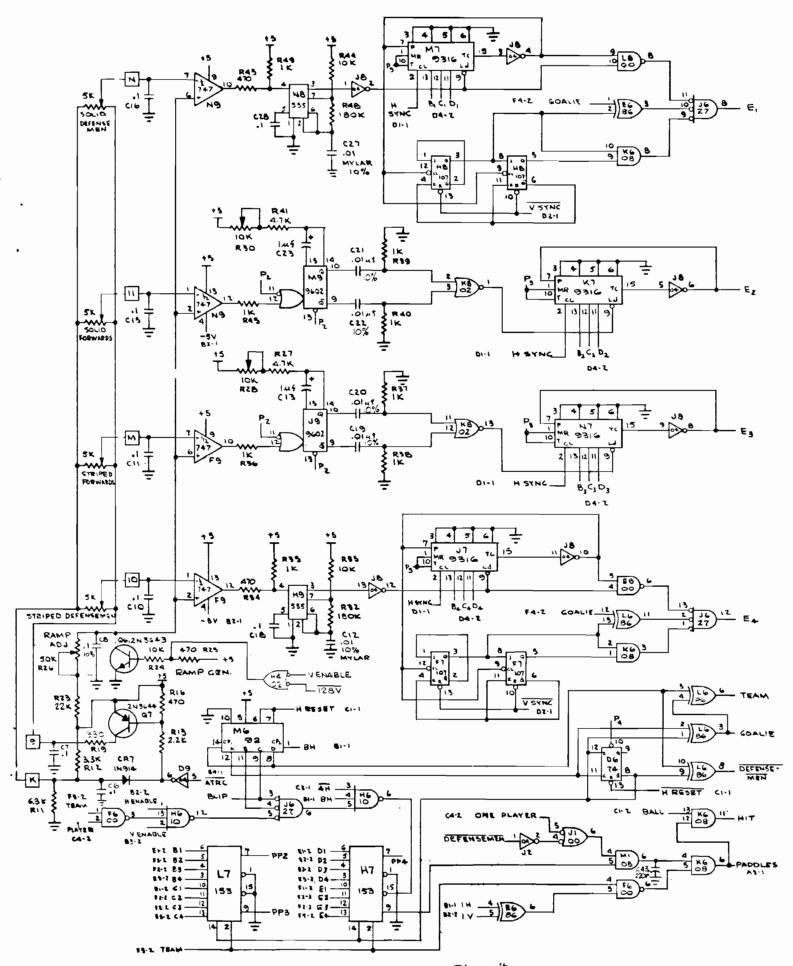

### PLAYERS CIRCUIT:

The players circuit (Figure 11) consists of a vertical window generator, ramp generator, control switch, forwards circuits, defensemen/goalie circuits, multiplexer circuit, check pattern generator, one-player solid defensemen defeat circuit, and player summing circuit. Each of these circuits is discussed in detail in the following paragraphs.

VERTICAL WINDOW GENERATOR: The vertical window generator consists of NAND gates F6-3, H6-12, and H6-6; negative-true AND gate J6-6; exclusive

OR gates L6-6, L6-3, and L6-8; flip-flop D6-8, and waveform generator M6. Waveform generator M6 is actually a specially wired counter that is driven by the 8H signal and is reset each time the H RESET signal occurs. Thus, four waveforms (A, B, C and D) are generated by M6 during each horizontal line.

Waveform A is applied to exclusive OR gate L6-3 and flip-flop D6-8, and waveform D is applied to exclusive OR gates L6-6 and L6-8. When horizontal reset occurs, generator M6 is reset by the H RESET signal; and flip-flop D6-8 is reset by the  $\overline{\text{H RESET}}$  signal. Subsequently, flip-flop D6-8 and gates L6-6, L6-3 and L6-8 logically process waveforms A and D and produce four signals which are identified as TEAM, GOALIE,  $\overline{\text{DEFENSEMEN}}$ , and  $\overline{\text{Q}}$ . The  $\overline{\text{DEFENSE-MEN}}$  signal is applied to the kick circuit and to the one player defensemen defeat circuit, and the GOALIE signal is applied to the defensemen circuits. The TEAM signal is applied to the kick circuit, check pattern generator, multiplexer, and NAND gate F6-3. The multiplexer also receives the  $\overline{\text{Q}}$  signal.

When the game-select 2/1 switch is set to the two-player position (2) during the play mode, the 1 PLAYER signal is low, which forces the output of NAND gate F6-3 high. Each time the electron beam of the picture tube enters the play-field area, the H ENABLE and V ENABLE signals go high, causing the output of NAND gate H6-12 to go low. In turn, each time the B and C signals from generator M6 are low when the output of NAND gate H6-12 is low, the output of gate J6-6 is forced high. This high is NANDed with the  $\overline{4H}$  and 8H signals to form the vertical window signals for the goalies, defensemen, and forwards. The windows for the left team's goalie, defensemen, and forwards begin at horizontal locations 152H, 200H, and 296H, respectively. The windows for the right team's goalie, defensemen, and forwards begin at horizontal positions 392H, 344H, and 248H, respectively. Each window signal is 4H wide and is used in conjunction with the TEAM signal to gate player signals E1, E2, E3 and E4 through multiplexer H7 at the proper times.

When the game-select switch is set to the 1 player position (1) during the PLAY mode, the 1 PLAYER signal is high. Thus, whenever the TEAM signal is high,

FIGURE 11. Players Circuit

the output of NAND gate F6-3 is forced low, which, in turn, forces the output of NAND gate H6-6. Inhibiting NAND gate H6-6 supresses the player window signal. The timing of the TEAM signal is such that only the player window signals for the right team's forwards, defensemen, and goalie are suppressed.

RAMP GENERATOR: The ramp generator consists of transistor Q6 and associated components. Transistor Q6 is driven by the 256V signal from the vertical sync circuit. When the VENABLE 128V signal is low, capacitor C8 changes through potentiometer R26 and resistor R23, causing a positive-going ramp to be formed at the collector of Q6. When the 256V signal goes high, transistor Q6 turns on and discharges C8, terminating the ramp. The sawtooth signal developed at the collector of Q6 is applied to the forwards and defensemen circuits. Potentiometer R26 is used to adjust the scope of the ramp signal, which, in turn, adjusts the symmetry of the goalie travel.

CONTROL SWITCH: The control switch is composed of transistor Q7, inverter D9-6, and associated components. This circuit is used to enable the front-panel player-position controls during the play mode and to disable them during the attract mode. In the play mode, the  $\overline{ATRC}$  signal is high. Inverter D9-6 inverts the high ATRC signal, which turns on Q7 and forward biases diode CR7. Forward biasing CR7 places a low on one side of the player-position controls, and turning on Q7, places a high on the opposite side of these controls. As a result, the controls are enabled and can be used to position the various players of the game. During the attract mode, the  $\overline{ATRC}$  signal is low, which causes the output of inverter D9-6 to be high. This high turns off diode CR7 and transistor Q7, which removes the voltage from the controls. Consequently, the controls are inoperable in the attract mode.

FORWARDS CIRCUITS: The game has two identical forwards circuits. These circuits are used to position the solid and checked forwards during the play mode and furnish player—segment information to the vertical speed control circuit. Because these circuits are identical, only the solid forwards (left side) circuit is discussed in the following paragraphs.

The solid forwards circuit consists of the front-panel solid FORWARDS potentiometer, comparator N9-12 and associated circuitry, one-shot M9-10/9 and associated circuitry, NOR gate K8-1, counter K7, and inverter J8-6. Except for the front-panel solid FORWARDS potentiometer, all of the solid forwards circuitry is located on the computer PWA.

Comparator N9-12 compares the voltage appearing at the swinger of the solid FORWARDS potentiometer and the ramp voltage from the ramp generator. When the ramp voltage equals the swinger voltage, the output of N9-12 goes high. This high triggers one-shot M9-10/9, which furnishes a positive-going pulse to differentiator R39-C21 and a negative-going pulse to differentiator R40-C22. When the leading edge positive- and negative-going spikes are applied to NOR gate K8-1, the output of the gate goes low, which presets counter K7 to zero. Immediately after the spikes decay to zero (low), the output of NOR gate K8-1 goes high, allowing counter K7 to begin counting H SYNC pulses.

At the count of 15, pin 15 of K7 goes high, and the output of inverter J8-6 goes low. This low is applied to pin 7 of the counter, causing it to stop counting. While K7 is counting, the output of inverter J8-6 is high. This high (signal E2) is sent to the multiplexer and is eventually used to cause the top solid forward symbol to appear on the TV screen. Also, during the counting period, the three most significant bits of data (signals D2, C2, and B2) are multiplexed and used to inform the vertical speed control circuit as to what portion of the player is being developed at any given time. The vertical speed control uses this information to determine the vertical rebound or kick angle of the ball when a hit occurs or vertical bounce angle when the ball hits the upper or lower side of the playfield symbol.

When the trailing-edge spikes of the differentiated pulses from one-shot M9-10/9 occur, the output of NOR gate K8-1 again goes low, which initializes counter K7. When the spikes decay, the counteris enabled and subsequently develops the signals from the bottom solid forward. Potentiometer R41 is used to adjust the duration of the pulses produced by one-shot M9-10/9 and, consequently, the

vertical spacing between the top and bottom solid forwards.

As the solid FORWARDS potentiometer is adjusted to make the voltage at pin 1 of comparator N9-12 more positive, it takes longer for the ramp voltage to equal the voltage at pin 1. As a result, counter K7 begins counting later relative to the beginning of vertical sweep; and, therefore, the solid-forward symbols are moved down on the TV screen. Conversely, lowering the pin 1 voltage of the comparator causes the solid-forward symbols to move up the TV screen.

DEFENSEMEN/GOALIE CIRCUITS: Two identical defensemen/goalie circuits are used in the game. These circuits are used to position the solid and checked defensemen and goalies during the play mode and furnish player—segment information to the vertical speed control circuit. Because these circuits are identical, only the solid defensemen/goalie (left side) circuit is discussed in the following paragraphs.

The solid defensemen/goalie circuit consists of the solid DEFENSEMEN potentiometer, comparator N9-10 and associated circuitry, a stable multivibrator N8-3 and associated circuitry, inverters J8-2 and J8-4, counter M7, flip-flops H8-3/2 and H8-5/6, NAND gate L8-8, exclusive OR gate E6-3, AND gate K6-8, and negative-true AND gate J6-8. Except for the front-panel solid DEFENSE-MEN potentiometer, all of the solid defensemen/goalie circuitry is located on the computer PWA.

Comparator N9-10 compares the voltage appearing at the swinger of the solid DEFENSEMEN potentiometer and the ramp voltage from the ramp generator. When the ramp voltage equals the swinger voltage, the output of N9-10 goes high. This high enables a stable multivibrator N8-3, which begins generating a train of pulses.

When the multivibrator begins to oscillate, the output at pin 3 goes high; and, consequently, the output of inverter J8-2 goes low. This low presets counter

M7 to zero and inhibits NAND gate L8-8. When the output of multivibrator N8-7 goes low, counter M7 begins counting H SYNC pulses; and the output of NAND gate L8-8 goes low. The outputs of exclusive OR gate E6-3 and AND gate K6-8 is driven high. This high signal (E1) is sent to the multiplexer and is eventually used to cause the top solid defenseman symbol to appear on the TV screen. Also, during the counting period, the three most significant bits of data (signals D1, C1 and B1) are multiplexed and used to inform the vertical speed control circuit as to what portion of the player is being developed at any given time. The vertical speed control uses this information to determine the vertical rebound or kick angle of the ball when a hit occurs or vertical bounce angle when the ball hits the upper or lower side of the playfield symbol.

At the count of 15, pin 15 of counter M7 goes high; and the output of inverter J8-4 goes low. This low is applied to pin 7 of the counter and to the clock inputs of J-K flip-flops H8-3/2 and H8-5/6. As a result, counter M7 stops counting; and the Q output of flip-flop H8-3 goes high. In addition, the output of NAND gate L8-8 goes high, which forces the output of J6-8 low. This low establishes the lower end of the top solid defenseman symbol.